- •Лекция 1. Информационные процессы в эвм Введение

- •Основные структуры данных

- •Обработка данных

- •Способы представления информации и два класса эвм

- •Кодирование информации

- •Представление данных в эвм.

- •Форматы файлов

- •Кодирование чисел

- •Кодирование текста

- •Кодирование графической информации

- •Кодирование звука

- •Типы данных

- •Лекция 2. Компьютер – общие сведения

- •Основные узлы пк – «Материнская плата»

- •Интерфейсные шины

- •Основные внешние устройства компьютера

- •Вопросы и задания

- •Лекция 3. Многоуровневая компьютерная организация

- •Архитектура компьютера

- •Классическая структура эвм - модель фон Неймана

- •Особенности современных эвм

- •Вопросы и задания

- •Лекция 4. Математическое обеспечение компьютеров

- •Программное обеспечение

- •Специальное

- •Библиотеки стандартных программ и ассемблеры

- •Высокоуровневые языки и системы автоматизированного программирования

- •Диалоговые ос и субд

- •Прикладные программы и case – технологии

- •Компьютерные сети и мультимедиа

- •Операционные системы

- •Лекция 5.Вычислительные системы - общие сведения Введение

- •Общие требования

- •Классификация компьютеров по областям применения

- •Персональные компьютеры и рабочие станции

- •Увеличение производительности эвм, за счет чего?

- •Параллельные системы

- •Суперкомпьютеры

- •Разновидности высокопроизводительных систем и области их применения

- •Ограничения производительности вс

- •Закон Амдала и его следствия

- •Микропроцессорная система

- •Что такое микропроцессор?

- •Микроархитектура процессора

- •512 Кбайт

- •Лекция 6 (с) Устройство управления

- •Микропроцессорная память

- •Структура адресной памяти процессора

- •Интерфейсная часть мп

- •Трансляторы

- •Режимы работы микропроцессорной системы

- •Классификация процессоров

- •Микроархитектура процессора Pentium II

- •512 Кбайт

- •Вопросы и задания

- •Лекция 7. Структурная организация эвм - память

- •Классификация памяти

- •Распределение системной памяти

- •Расширенная

- •Верхняя память (Upper Memory Area) – это 384 Кбайт, зарезервированных у верхней границы системной памяти. Верхняя память разделена на несколько частей:

- •Первые 128 Кбайт являются областью видеопамяти и предназначены для использовании видеоадаптерами, когда на экран выводится текст или графика, в этой области хранятся образы изображений;

- •Видеопамять

- •Оперативная память, типы оп

- •Тэг Строка Слово (байт)

- •Способы организации кэш-памяти

- •1. Где может размещаться блок в кэш-памяти?

- •Алгоритм псевдо lru.

- •2. Как найти блок, находящийся в кэш-памяти?

- •3. Какой блок кэш-памяти должен быть замещен при промахе?

- •4. Что происходит во время записи?

- •Разновидности строения кэш-памяти

- •Вопросы и задания

- •Лекция 8. Логическая организация памяти

- •Виртуальная память

- •Основная память

- •Дисковая память

- •Страничная организация памяти

- •Преобразование адресов

- •Сегментная организация памяти.

- •Свопинг

- •Вопросы и задания

- •Лекция 9. Методы адресации

- •Лекция 10. Внешняя память компьютера Введение

- •Жесткий диск (Hard Disk Drive)

- •Общее устройство нжмд

- •Пластины (диски)

- •Головка записи-чтения

- •Позиционер

- •Контроллер

- •Производительность

- •Структура хранения информации на жестком диске

- •Кластер

- •Магнитооптические диски

- •Лазерные компакт-диски cd - rom

- •Дисковые массивы и уровни raid

- •Raid 0: Базовая конфигурация.

- •Raid1: Зеркальные диски.

- •Вопросы и задания

- •Лекция 11. Основные принципы построения систем ввода/вывода

- •Физические принципы организации ввода-вывода

- •Магистрально-модульный способ построения эвм

- •Структура контроллера устройства ввода-вывода

- •Опрос устройств и прерывания. Исключительные ситуации и системные вызовы

- •Организация передачи данных

- •Стандартные интерфейсы и шины систем ввода-вывода

- •Вопросы и задания

- •Лекция 12. Особенности архитектуры современных высокопроизводительных вс

- •Классификация архитектур по параллельной обработке данных

- •Вычислительные Системы

- •Параллелизм вычислительных процессов

- •Параллелизм на уровне команд – однопроцессорные архитектуры

- •Конвейерная обработка

- •Суперскалярные архитектуры

- •Мультипроцессорные системы на кристалле

- •Технология Hyper-Threading

- •Многоядерность — следующий этап развития

- •Вопросы и задания

- •Лекция 13. Архитектура многопроцессорных вс Введение

- •Smp архитектура

- •Mpp архитектура

- •Гибридная архитектура (numa)

- •Организация когерентности многоуровневой иерархической памяти.

- •Pvp архитектура

- •Кластерная архитектура

- •Проблемы выполнения сети связи процессоров в кластерной системе.

- •Лекция 14. Кластерные системы

- •Концепция кластерных систем

- •Разделение на High Availability и High Performance системы

- •Проблематика High Performance кластеров

- •Проблематика High Availability кластерных систем

- •Смешанные архитектуры

- •Лекция 15 Многомашинные системы – вычислительные сети Введение

- •Простейшие виды связи сети передачи данных

- •Связь компьютера с периферийным устройством

- •Связь двух компьютеров

- •Многослойная модель сети

- •Функциональные роли компьютеров в сети

- •Одноранговые сети

- •Сети с выделенным сервером

- •Гибридная сеть

- •Сетевые службы и операционная система

- •Лекция 17. Сети и сетевые операционные системы Введение

- •Для чего компьютеры объединяют в сети

- •Сетевые и распределенные операционные системы

- •Взаимодействие удаленных процессов как основа работы вычислительных сетей

- •Основные вопросы логической организации передачи информации между удаленными процессами

- •Понятие протокола

- •Многоуровневая модель построения сетевых вычислительных систем

- •Проблемы адресации в сети

- •Одноуровневые адреса

- •Двухуровневые адреса

- •Удаленная адресация и разрешение адресов

- •Локальная адресация. Понятие порта

- •Полные адреса. Понятие сокета (socket)

- •Проблемы маршрутизации в сетях

- •Связь с установлением логического соединения и передача данных с помощью сообщений

- •Синхронизация удаленных процессов

- •Заключение

- •Список литературы:

Лекция 6 (с) Устройство управления

Для реализации любой команды необходимо на соответствующие управляющие входы любого устройства компьютера подать определенным образом распределенную во времени последовательность управляющих сигналов. Часть цифрового вычислительного устройства, предназначенная для выработки этой последовательности, называется устройством управления.

Любое действие, выполняемое в операционном блоке, описывается некоторой микропрограммой и реализуется за один или несколько тактов. Элементарная функциональная операция, выполняемая за один тактовый интервал и приводимая в действие управляющим сигналом, называется микрооперацией. Совокупность микроопераций, выполняемых в одном такте, называется микрокомандой (МК). Микрокоманды, предназначенные для выполнения некоторой функционально законченной последовательности действий, образуют микропрограмму. Устройство управления предназначено для выработки управляющих сигналов, под воздействием которых происходит преобразование кодов в АЛУ, а также операции по записи и чтению данных в/из запоминающего устройства.

Устройства управления делятся на:

УУ с жесткой, или схемной логикой;

УУ с программируемой логикой (микропрограммные УУ).

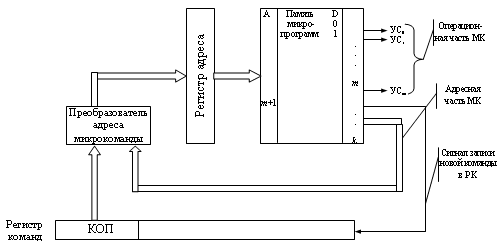

В устройствах управления первого типа для каждой команды, задаваемой кодом операции, строится набор комбинационных схем, которые в нужных тактах вырабатывают необходимые управляющие сигналы. В микропрограммных УУ каждой команде ставится в соответствие совокупность хранимых в специальной памяти слов - микрокоманд. Каждая из микрокоманд содержит информацию о микрооперациях, подлежащих выполнению в данном такте, и указание, какое слово должно быть выбрано из памяти в следующем такте. Микропрограммное устройство управления представлено на рисунке 6.5. Преобразователь адреса микрокоманды преобразует код операции команды, присутствующей в данный момент в регистре команд, в начальный адрес микропрограммы, реализующей данную операцию, а также определяет адрес следующей микрокоманды выполняемой микропрограммы по значению адресной части текущей микрокоманды.

Рис. 6.5 Функциональная

схема микропрограммного устройства

управления

Рис. 6.5 Функциональная

схема микропрограммного устройства

управления

Предположим, что выполняется операция умножения и начальный адрес микропрограммы равен 300, количество разрядов множителя равно 2, а адресная часть микрокоманды содержит адрес микрокоманды, которая должна быть выбрана в следующем такте. В последней микрокоманде в регистр команд загрузится очередная команда, код операции которой определит начальный адрес очередной микропрограммы. В реальных микропрограммных устройствах управления формирование адреса следующей микрокоманды проводится более сложным образом, учитывающим возможности ветвлений и циклического повторения отдельных фрагментов микропрограмм.

Таблица 6.1 Микропрограмма выполнения операции умножения |

||||||||

Адрес МК |

УС1 |

УС2 |

УС3 |

УС4 |

УС5 |

УС6 |

Сигнал записи в РК |

Адрес следующей МК |

300 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

301 |

301 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

302 |

302 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

303 |

303 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

304 |

304 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

Х |

Устройство управления, реализованное по микропрограммному принципу, может легко настраиваться на возможные изменения в операционной части ЭВМ. При этом настройка во многом сводится лишь к замене микропрограммной памяти. Однако УУ этого типа обладают худшими временными показателями по сравнению с устройствами управления на жесткой логике.

ПЗУ микропрограмм - хранит в своих ячейках коды об управляющих сигналах (импульсах), необходимые для выполнения обработки данных. Эти коды, по выбранному дешифратором кодом операции, считывает из ПЗУ микропрограмм необходимую последовательность управляющих сигналов.

Узел формирования адреса (находится в интерфейсной части МП) - устройство, вычисляющее полный адрес ячейки памяти (регистра) по реквизитам, поступающим из регистра команд и регистров микропроцессорной памяти.

Схема взаимодействия ОУ и ПЗУ устройства управления

Итак, вспомним основную схему функционирования операционного устройства – ОУ. В составе любого процессора имеется специальный регистр – счетчик команд. После выполнения очередной команды его содержимое увеличивается на единицу если код одной команды занимает несколько ячеек памяти, то содержимое счетчика увеличивается на длину команды). Существуют специальные команды (передачи управления), которые модифицируют содержимое счетчика, обеспечивая переходы по программе. В оперативной памяти – ОП (иногда говорят в основной памяти, системной памяти) находится наша программа, которая начинается с некоторого адреса (этот адрес находится в счетчике команд), соответствующего имени программы. Она представляет собой совокупность ассемблерных команд (имеется в виду, что программа оттранслирована). Пусть в теле общей программы есть фрагмент сложения двух операндов в формате двухадресной команды:

A [A] + [B]

Или Add A,B

Move C, A

ОП УУ

Instructions -------------------- 300

Add A, B

301

Move C, A 303

--------------------

Data --------А------------ --------В------------

ПЗУ

Адрес 1ой

мк

Адрес 1ой

мк

01

01

02

03 такты

син-ции

07

Таким образом, имя нашей микропрограммы – это начальный адрес в ОП, код операции КОП ассемблерной команды – это начальный адрес некоторой последовательности микрокоманд машинного кода, защитой в ПЗУ устройства управления УУ.