- •Семинар 1. Числовой логический уровень

- •Система счисления.

- •Позиционные системы счисления.

- •Выбор системы счисления

- •Перевод чисел из одной системы счисления в другую

- •Перевод чисел из одной системы счисления в другую, когда одно основание является целой степенью другого.

- •Проблема представления отрицательных чисел

- •Прямой код.

- •Замечания.

- •Дополнительный код.

- •Обратный код.

- •Способы представления чисел в эвм

- •Фиксированная запятая

- •Плавающая запятая

- •Выполнение арифметических операций над числами, представленными с фиксированной запятой.

- •Семинар 2. Цифровой логический уровень и микроархитектурный уровень

- •Электротехническая интерпретация.

- •У ровень физических устройств.

- •Дешифратор

- •Шифратор

- •Регистр сдвига

- •Методы передачи данных

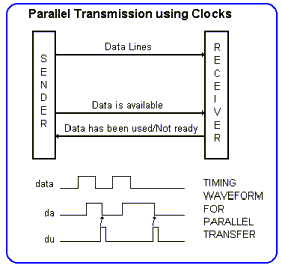

- •Параллельная передача данных

- •Последовательная передача данных

- •Синхронные коммуникации

- •Передача в основной полосе частот и широкополосная передача.

- •Вопросы и задания

- •Семинар 3. Архитектура классической эвм

- •Система кодирования команд

- •Взаимозависимость формата команды и основных параметров эвм

- •Способы адресации

- •Семинар 4. Простой процессор, работающий с четырехадресной командой. Введение

- •Функционирование программируемого процессора

- •Алгоритм работы

- •Задание

- •Семинар 5. Микропроцессор – дальнейшее развитие Введение

- •Модернизация

- •Задание

- •Семинар 6. Дальнейшее совершенствование микропроцессора, одноадресные и безадресные команды. Анализ предыдущей модели

- •Задание

- •Шинная структура связей

- •Семинар 7. Кэш-память Введение

- •Структура кэш-памяти в процессоре i486.

- •Алгоритм псевдо lru.

- •Увеличение производительности кэш памяти.

- •Семинар 8. Режимы работы микропроцессорной системы

- •Архитектура микропроцессорных систем

- •Типы микропроцессорных систем

- •Семинар 9 . Программная модель процессора

- •Общие понятия

- •Регистры процессора

- •Формат команды микропроцессора ia-32

- •Эффективный адрес.

- •Семинар 10. Организация пк Введение

- •Архитектура персонального компьютера

- •Процессоры персональных компьютеров

- •Особенности процессоров Pentium

- •Семинар 11. Интерфейсы пк Введение

- •Последовательный порт(rs-232).

- •Параллельный порт(lpt).

- •Интерфейс ide.

- •Cпецификация Enhanced ide (eide)

- •Интерфейс scsi.

- •Характеристики scsi.

- •Системная магистраль isa

- •Распределение ресурсов компьютера

- •Семинар 12. Видеосистема пк и режимы графической акселерации Введение

- •Мониторы

- •Видеоадаптеры

- •Понятие о графических ускорителях

- •Ускорители двумерной графики

- •Ускорители трехмерной графики

- •Семинар 13. Файловая система компьютера Введение

- •Общие сведения о файлах

- •Типы файлов

- •Атрибуты файлов

- •Организация файлов и доступ к ним

- •Последовательный файл

- •Файл прямого доступа

- •Другие формы организации файлов

- •Операции над файлами

- •Директории. Логическая структура файлового архива

- •Разделы диска. Организация доступа к архиву файлов.

- •Операции над директориями

- •Защита файлов

- •Контроль доступа к файлам

- •Списки прав доступа

- •Заключение

- •Семинар 14. Практика настройки и использования пк. Системный блок

- •Загрузка операционной системы

- •Дисковые накопители

- •Настройка компьютера

- •Настройка видеоадаптера

- •Настройка звуковой карты

- •Настройка cd-rom

- •Защита данных и самого компьютера

- •Использование программы bios setup

- •Модернизация компьютера

- •Увеличение оперативной памяти

- •Установка дополнительных плат

- •Самотестирование при включении

- •Поиск и устранение неисправностей

- •Системная плата

- •Основной микропроцессор

- •Системная и локальная шина.

Регистр сдвига

Регистр сдвига – регистр, обеспечивающий помимо хранения информации, сдвиг влево или вправо всех разрядов одновременно на одинаковое число позиций. При этом выдвигаемые за пределы регистра разряды теряются, а в освобождающиеся разряды заносится информация, поступающая по отдельному внешнему входу регистра сдвига. Обычно эти регистры обеспечивают сдвиг кода на одну позицию влево или вправо. Но существуют и универсальные регистры сдвига, которые выполняют сдвиг как влево, так и вправо в зависимости от значения сигнала на специальном управляющем входе или при подаче синхросигналов на разные входы регистра. Регистр сдвига может быть спроектирован и таким образом, чтобы выполнять сдвиг одновременно не на одну, а на несколько позиций.

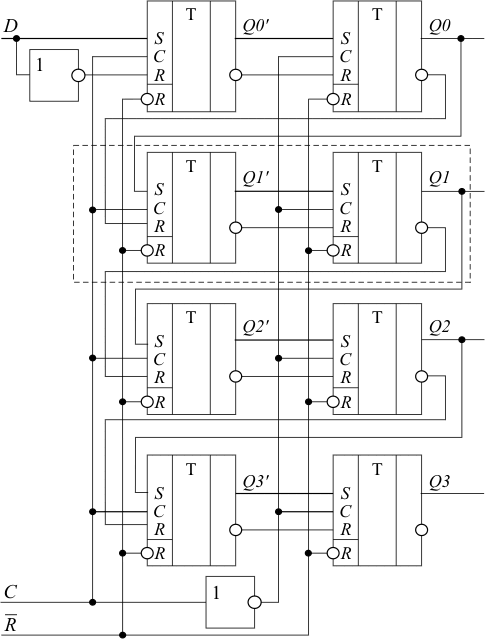

Регистры сдвига строятся на двухступенчатых триггерах. Схема четырехразрядного регистра, выполняющего сдвиг на один разряд от разряда 0 к разряду 3, показана на рисунке, а его условно-графическое обозначение – на рисунке ниже. Ввод информации в данный регистр – последовательный через внешний вход D0. Регистр имеет вход асинхронной установки всех разрядов в "0". Для наглядности каждый двухступечатый регистр представлен двумя одноступенчатыми с соответствующей организацией синхронизации первой и второй ступеней. Пунктиром обозначен реальный двухступенчатый триггер.

Структура регистра сдвига

Структура регистра сдвига

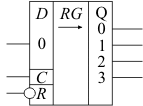

Условно-графическое обозначение

четырехразрядного регистра сдвига с

асинхронным входом установки в "0"

Условно-графическое обозначение

четырехразрядного регистра сдвига с

асинхронным входом установки в "0"

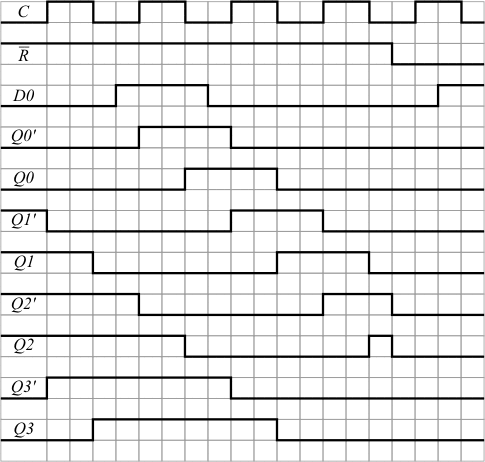

Идеализированная временная диаграмма работы регистра сдвига, структура которого представлена на рисунке. Предполагаем, что начальное состояние регистра следующее: Q0=0, Q1=1, Q2=1, Q3=0.

Временная диаграмма работы регистра

сдвига

Временная диаграмма работы регистра

сдвига

Работа регистра сдвига в каждом периоде сигнала синхронизации разбивается на две фазы: при высоком и при низком значении синхросигнала:

При высоком уровне синхросигнала проводится запись значения выхода (i – 1)-го разряда регистра в первую ступень i-го разряда. Вторая ступень каждого разряда сохраняет свое прежнее значение. В этой фазе состояние первой ступени i-го триггера повторяет состояние второй ступени (i – 1)-го триггера. Вторые ступени каждого триггера, а следовательно, и выходы регистра в целом, остаются неизменными.

При низком уровне синхросигнала значение, записанное в первой ступени каждого триггера, перезаписывается в его вторую ступень. Запись в первую ступень триггера запрещена. В этой фазе состояния первой и второй ступеней каждого триггера становятся одинаковыми.

Поступление сигнала R = 0 вне зависимости от значения сигнала на входе синхронизации С и сигнала на входе D0 устанавливает все разряды регистра в нулевое состояние.

Конечно, эти схемы далеко не исчерпывают все возможные комбинации, которые лежат в основе схемотехники ЭВМ, но это уже другой курс.

Далее мы рассмотрим отрывок из курса «Основы сетей передачи данных», который нам необходим для анализа продвижения данных в компьютере.

Методы передачи данных

Главным требованием предъявляемым к коммуникационным системам является обеспечение передачи данных пользователям и получение доступа к разделяемым ресурсам с гарантированным значением качества сервиса, надежности, производительности, защищенности и масштабируемости. Это требование обеспечивается целым комплексом мер и методов, среди которых первое место занимают:

собственно методы передачи данных (параллельная, последовательная и т.д.);

кодирование и модуляция данных;

взаимная синхронизация передатчика и приемника;

выбор режима передачи данных – синхронная или асинхронная;

выбор методов уплотнения каналов связи – коммутация и мультиплексирование;

выбор среды передачи данных с требуемым значением пропускной способности.

В общем случае, всякая коммуникация осуществляется при участии трех основных субъектов:

отправитель (sender), источник данных;

среда (medium) – это не только электрическая, оптическая или радиолиния связи, но и сам механизм коммуникации;

получатель (receiver), приемник.

Отправитель и получатель осуществляют либо последовательную, либо параллельную передачу данных.