- •1. Порівняльні характеристики технологічних груп імс

- •(Ттл) Транзисторно-транзисторна логіка

- •2. Основні статичні та динамічні характеристики імс

- •Динамічні характеристики ліс

- •3. Завадостійкість імс ттл та ттлш, шляхи їх покращення.

- •4. Вплив дестабілізуючих факторів на характеристики імс.

- •5. Вплив ємності навантаження на швидкодію імс.

- •6. Логічні імс кнон та їх основні характеристики.

- •7. Особливості застосування імс кмон.

- •8. Класифікація тригерів.

- •9. Тригери типу rs та rsc.

- •10. Тригери типу d

- •11. Тригери типу jк.

- •12. Класифікації запам’ятовувальних пристроїв. Технологічна класифікація

- •Класифікація за організацією пам’яті

- •13. Репрограмовані пзп

- •Рпзп з уфс

- •14. Статичні та динамічні оперативні запам’ятовувальні пристрої.

- •Зе на кмон транзисторах

- •15. Основні параметри запам’ятовувальних пристроїв.

- •16. Дешифратори і демультиплексори.

- •17. Шифратори. Розширення кількості входів шифратора.

- •18. Компаратори. Послідовне та паралельне з’єднання багаторозрядних компараторів.

- •19. Конроль парності.

- •20. Двонаправленні шинні формувачі.

- •21. Суматори з паралельним, послідовним та груповим переносом.

- •22. Алп типу 155ипз.

- •23. Регістри зсуву

- •24. Розподільники імпульсів і подільники частоти.

- •25. Асинхронні лічильники

- •26. Синхронні лічильники.

- •27. Двійково-десятковий синхронний лічильник.

- •28. Пмл. Схема макрокомірки.

- •29. Реконфігурована матрична логіка (fpga).

- •30. Програмована матрична логіка. Ерld, cpld.

30 |

Комп'ютерна схемотехніка |

|

1 |

Порівняльні характеристики технологічних груп ІМС..............................................2 |

|

2 |

Основні статичні та динамічні характеристики ІМС..................................................3 |

|

3 |

Завадостійкість ІМС ТТЛ та ТТЛШ, шляхи їх покращення………………………..4 |

|

4 |

Вплив дестабілізуючих факторів на характеристики ІМС. .......................................4 |

|

5 |

Вплив ємності навантаження на швидкодію ІМС……...............................................5 |

|

6 |

Логічні ІМС КНОН та їх основні характеристики......................................................5 |

|

7 |

Особливості застосування ІМС КМОН. ......................................................................7 |

|

8 |

Класифікація тригерів. ..................................................................................................8 |

|

9 |

Тригери типу RS та RSC. ..............................................................................................8 |

|

10 |

Тригери типу D. .............................................................................................................9 |

|

11 |

Тригери типу JК. ..........................................................................................................12 |

|

12 |

Класифікації запам’ятовувальних пристроїв. ...........................................................13 |

|

13 |

Репрограмовані ПЗП....................................................................................................14 |

|

14 |

Статичні та динамічні оперативні запам’ятовувальні пристрої. ............................15 |

|

1 |

Основні параметри запам’ятовувальних пристроїв. ................................................17 |

|

16 |

Дешифратори і демультиплексори. ...........................................................................18 |

|

17 |

Шифратори. Розширення кількості входів шифратора……………………………20 |

|

18 |

Компаратори. Послідовне та паралельне з’єднання багаторозрядних компараторів. ...............................................................................................................21 |

|

19 |

Конроль парності. .......................................................................................................22 |

|

20 |

Двонаправленні шинні формувачі. ...........................................................................25 |

|

21 |

Суматори з паралельним, послідовним та груповим переносом…………………26 |

|

22 |

АЛП типу 155ИПЗ. .....................................................................................................27 |

|

23 |

Регістри зсуву.............................................. ................................................................28 |

|

24 |

Розподільники імпульсів і подільники частоти. ......................................................28 |

|

25 |

Асинхронні лічильники.............................................. ................................................29 |

|

26 |

|

|

27 |

Двійково-десятковий синхронний лічильник. .........................................................30 |

|

28 |

ПМЛ. Схема макрокомірки. .......................................................................................31 |

|

29 |

Реконфігурована матрична логіка (FPGA). ..............................................................32 |

|

30 |

Програмована матрична логіка. ЕРLD, CPLD. .........................................................32 |

1. Порівняльні характеристики технологічних груп імс

ТЛБЗ (Транзисторна логіка безпосередній зв’язок)

Y =X1vX2vX3vX4

=X1vX2vX3vX4

U1=0,7В

U0=0,1-0,4В

Uлогічний=0,3В – логічний рівень

Переваги:

-чим меньший логічний рівень, тим більший рівень швидкодії

Недоліки:

невисока надійність спрацювання

низька завадостійкість

РТЛ (Резистивно-транзисторна логіка)

Переваги: краща завадостійкість

Недоліки:

-погіршена швидкодія

-паразитні ємності

РКТЛ (резистивно-конденсаторна-транзистивна логіка)

Більша швидкодія, велика завадостійкість

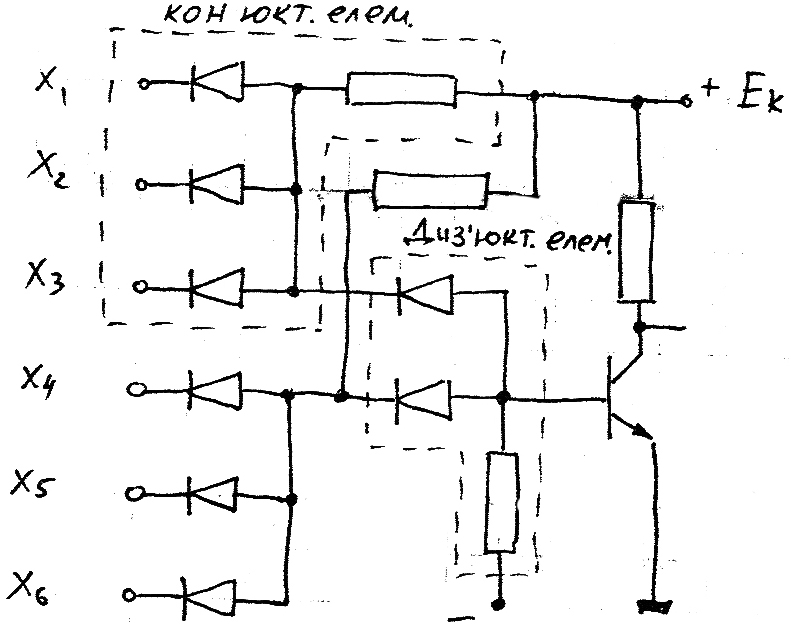

Діодно-транзисторна логіка (ДТЛ)

Y

=X1*X2*X3

V X4*X5*X6

=X1*X2*X3

V X4*X5*X6

Ця інверсія виконується за рахунок транзистора, який може перебувати у виключеному стані.

Якщо на X1 подати 0, то струм буде рівномірно протікати через діод, тоді напруга буде 0≤U0≤0,7В. Тобто низький потенціал на б.-л. вході призводить до того, що на вході буде великий потенціал (1). Такі схеми вже не використовують.

Хороша завадостійкість, мала швидкодія (до 1МГц)

(Ттл) Транзисторно-транзисторна логіка

На відміну від попередньої схеми, для того, щоб на вході був високий потенціал необхідно щоб була на вході була 1:

Якщо 0 ≤UБЕ≤0,55В

=> RКЕ>1мΩ

≤UБЕ≤0,55В

=> RКЕ>1мΩ

0,55≤ UБЕ ≤0,65В => 1мΩ≤RКЕ≤100Ω

0,7≤ UБЕ => RКЕ>100Ω

0≤U0≤0,4B

2,4≤U1≤4B

Така схема може працювати лише на двох рівнях: рівень логічного 0 і рівень логічної 1.

Пізніше з’явилася інші група, в якої покращилися основні параметри: швидкодія і споживання потужності.

ТТЛ з включенням діода Шоткі (ТТЛШ)

Швидкодія цих елементів збільшилась у 5 разів.

Емітерно зв’язана логіка (ЕЗЛ)

Висока або надвисока швидкодія до 1000 МГц

Мала енергія переключення

Незалежність споживаної потужності від частоти переключення

Висока навантажувальна здатність

Висока завадостійкість

Мала вартість

Широкий функціональний набір

Інтегрально-інжекційна логіка (І2Л)

Застосовується для побудови елементів пам’яті. Частота 10 МГц.

Комплементарна на базі МОН транзисторів

Логіка (КМОН)

Використовуються р-канальні та n-канальні польові транзистори.Використовується у 70% інтегральних мікросхем.

2. Основні статичні та динамічні характеристики імс

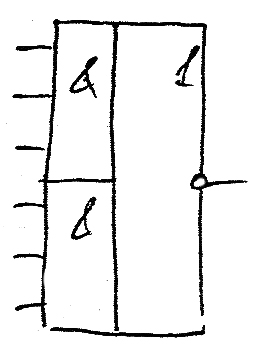

Статичні характеристики ЛІС

1 .

Передавальна характеристика (для

інверсних елементів)

.

Передавальна характеристика (для

інверсних елементів)

Uп – напруга перемикача

Uз+ - додатн.завадост.

Uз- - від’ємн.завадостійк.

ΔUн – зона невизначеності

ΔUн = Un0 – Un'

-------- - характеристика трігерів Шмідта

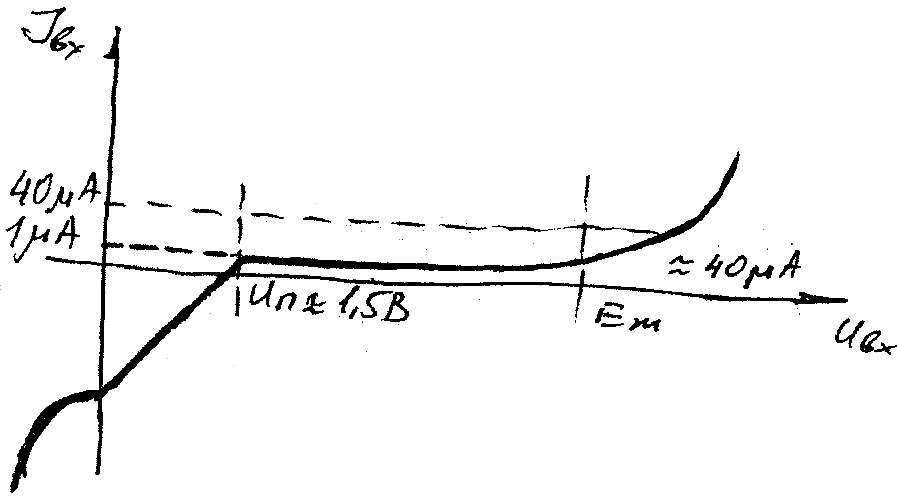

2.Вхідна характеристика – показник залежності Івх. Від Uвх.

В икористовуючи

вхідні характеристики – знаходиться

навантажувальна здатність вихідного

каскаду.

икористовуючи

вхідні характеристики – знаходиться

навантажувальна здатність вихідного

каскаду.

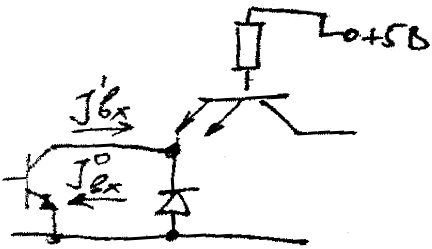

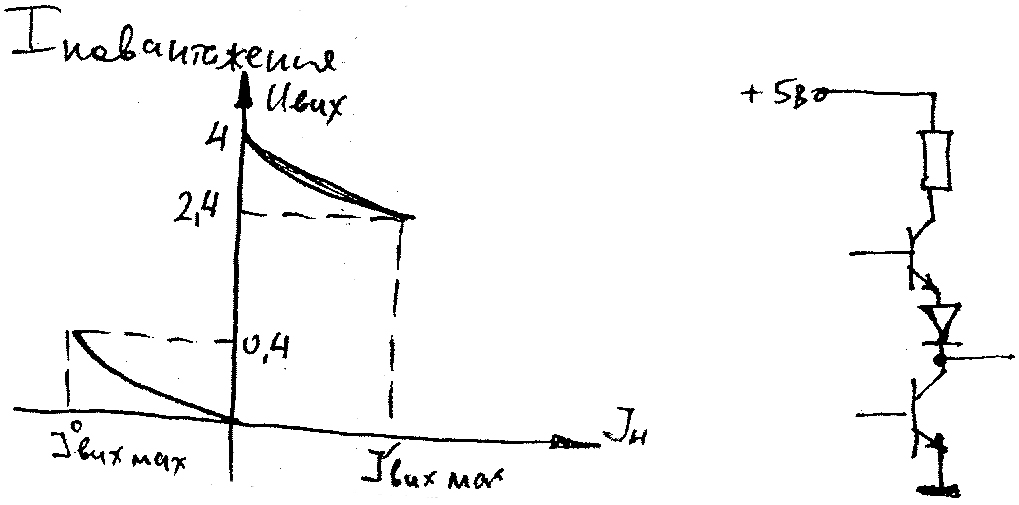

3.Вихідна характеристика – залежність вихідної напруги Uвих. Від Інавантаження

І снують

деякі мікросхеми, що забезпечують

втриччі більші значення Івих при

цих самих значеннях U.

снують

деякі мікросхеми, що забезпечують

втриччі більші значення Івих при

цих самих значеннях U.

Інші параметри:

реалізація логічних функцій

навантажувальна спроможність

коефіцієнт об’єднання по входу

коефіцієнт розгалуження по виходу

споживана потужність (струм)

стійкість інтегральних схем до механічних і температурних впливів

напруга живлення

надійність:

- інтенсивність відмов, λ

- напрацювання на одну відмову, Т

- ймовірність безвідмовної роботи Р(t) на протязі часу t

Статичні параметри

λ= n /NT, де n – число відмов

t – час дослідження

N – кількість елементів, що досліджуються

Вважаємо, що для сучасних ІС λ = 5*10-8.. 10-9 один/год

Т = 1/ λ P(t) = e-λt

Ємність елемента,

Макс/мін напруга живлення,

додатня/від’ємна завадостійкості (Вольти)