- •Конспект по электронике Оглавление

- •Цифробуквенная система обозначения пассивных элементов на принципиальных схемах и на изделиях.

- •Буквенное обозначение точности резисторов и конденсаторов:

- •Плоскостной электронно-дырочный переход.

- •Система обозначения отечественных и импортных полупроводниковых приборов (диодов, тиристоров, транзисторов, электронных микросхем)

- •Фотоэлектрические и излучающие в видимом, ик и уф диапазоне полупроводниковые приборы. Полупроводниковые лазеры. Оптоэлектронные пары. Их применение. Системы динамической индикации

- •Излучающие полупроводниковые приборы.

- •Тепловой шум (Джонсона).

- •Дробовой шум.

- •3) Шум 1/f (фликкер - шум).

- •Формирователи и генераторы импульсных сигналов на оу. Компараторы, триггеры Шмитта. Генераторы линейно-измеряющегося напряжения на оу

- •Типы частотных характеристик фильтров.

- •Расчет фильтров

- •Сравнительные характеристики серии логических микросхем.

- •Двоичные сумматоры. Одноразрядные двоичные сумматоры. Параллельные многоразрядные сумматоры. Структурные схемы, особенности работы. Основные параметры.

Сравнительные характеристики серии логических микросхем.

Элементы КМОП и ЭСЛ

серия |

параметр |

нагрузка |

вид |

||||

отеч. |

зарубеж. |

Рпотр,мВт |

tзд, нс |

Епотр,мДж |

Сн, пФ |

Rн, кОм |

|

134 |

74L |

1 |

33 |

33 |

50 |

4 |

базовые |

155(133) |

74 |

10 |

9 |

90 |

15 |

0,4 |

|

131 |

74H |

22 |

6 |

132 |

25 |

0,28 |

|

555 |

74LS |

2 |

9,5 |

19 |

15 |

2 |

Шотки |

531 |

74S |

19 |

3 |

57 |

15 |

0,28 |

|

1533 |

74ALS |

1,2 |

4 |

4,8 |

15 |

2 |

мод. Шотки |

1531 |

74F |

4 |

3 |

12 |

15 |

0,28 |

|

(~1530) |

74AS |

8,0(30) |

1,75 |

14(55) |

- |

- |

сверх быстр. Шотки |

1554 |

74AC |

0,025 |

3,5 |

0,009 |

500 |

0,2 |

КМОП с возм. ТТЛ |

1564 |

74HC |

0,025 |

10 |

0,025 |

500 |

0,2 |

|

1561 |

H4000 |

0,025 |

40 |

0,1 |

50 |

4 |

КМОП обыч.мод. |

Eпотр = Pпотрtзд =>если tздуменьшить в nраз, то Pпотр увеличится в 2nраз.

ЭСЛ – эмиттерно-связанная логика.

U0 = -0,7 ÷ -0,95 ≈ -0,8

U1 = -1,45 ÷ -1,95 ≈ -1,6

Высокое быстродействие достигается тем, что транзисторы дифференциального каскада и другие не входят в режим насыщения, а также малой разницей между уровнем логического «0» и логической «1» (0,8В). Последнее, в свою очередь, ухудшает помехоустойчивость. Для согласования микросхем различных видов логики используются микросхемы преобразования уровня.

КМОП.

Стандартный КМОП допускает использование Uп от 5В до 15В. Быстродействие изменяется в три раза, возрастает и мощность. Это позволяет непосредственно соединить схемы КМОП и ОУ.

Двунаправленный ключ.

При изменении входного сигнала сопротивление каналов транзистора с n и p каналом изменяется в противоположную сторону. Специальные схемные решения позволяют сделать эквивалентное сопротивление ключа независимым от величины и направления входного сигнала. Величина сопротивления канала ключа достигает единиц Ом. При отсутствии отпирающего напряжения на затворе сопротивление велико (десятки МОм), что равносильно разрыву цепи. Омический характер сопротивления канала позволяет использовать двунаправленные ключи не только для переключения логических сигналов, но и (в отличие от ТТЛ) для переключения аналоговых сигналов, а также для регулировки последних, используя ключ в этом случае в качестве переменного резистора, управляемого напряжением.

Инвертор КМОП

![]()

Защитные диоды обязательно присутствуют во всех логических элементах КМОП, так как они подвержены разрушающему воздействию статического электричества. В инверторе VD3, VD5, VD6 защитные элементы от отрицательных импульсов. Диоды VD1, VD2, VD4 защищают вход и выход от положительных выбросов и ограничивают его на уровне Uп+0,6. Для дополнительной защиты входов, особенно при длинных входных проводах, и для устранения паразитных колебаний последовательно с входом включают резистор для ограничения тока заряда включения емкости.

С хема

И-НЕ

хема

И-НЕ

При логической «1» n-каналы VT3 и VT4 открыта, а p-канальные VT1 и VT2 – заперты на входе логического «0». При подаче хотя бы одного логического «0» на вход, оказывается запертым одним из VT3 или VT4 и открытым хотя бы один из VT1 и VT2, что даст логическую «1» на выходе.

С хема

ИЛИ-НЕ

хема

ИЛИ-НЕ

При двух логических «0» входы VT1 и VT2 закрыты, а VT3 и VT4 открыты. На выходе – логическая «1». При логической «1» на любом из выходов по крайней мере один из n-каналов и хотя бы один из последовательных соединений p-каналов закрыт. На выходе 0.

Существует логические элементы с открытым стоком.

Не использованные входы КМОП надо включать так, чтоб не нарушались условия работы микросхемы в целом. В отличие от ТТЛ можно подключить к Uп напрямую. Нельзя оставлять неподключенными. При случайном соединении выхода с системой питания или с общей линией через открытие. Транзистор пропускает ток, ограниченный только сопротивлением канала и внутренним сопротивлением источника питания. Ток короткого замыкания и мощность рассеивания увеличиваются с ростом напряжения питания. При напряжении питания не более 5В и комнатной температуре 25˚С микросхема не выходит из строя при достаточно долговременном коротком замыкании.

Сопряжение КМОП и ТТЛ.

При сопряжении КМОП и ТТЛ к выходу КМОП можно подключить два входа ТТЛ 155серии и до девяти входов 555 серии. При подключении выхода ТТЛ ко входу КМОП необходимо включить резистор с выхода ТТЛ на источник питания (2кОм) с целью повышения уровня логической «1».

Разновидности функциональных схем:

- комбинационные схемы

- последовательные устройства

Комбинационные схемы характеризуются отсутствием памяти (память – свойство системы сохранять в течении требуемого времени значение сигнала, характеризующее внутреннее состояние цифрового устройства). Сигнал на выходе комбинационного устройства в любой момент времени однозначно определяется сочетанием сигналов на входе и не зависит от его предыдущего состояния. Схемным признаком таких схем является осуществление в цепи обратной связи. Примеры: логические элементы, эл. ключи, дешифраторы, арифметические устройства.

Последовательные обладают памятью и при смене цифр на входе, для предсказания сигнала на выходе, необходимо знать о состоянии, в котором устройство было до этого. В этих устройствах есть обратная связь. Простейшие из них – триггеры, счетчики, резисторы, запоминающие устройства.

Параметры цифровых элементов:

1)надежность – интенсивность отказа V, наработкой на отказ Т, вероятность безотказности;

2)стойкость к механическим и климатическим воздействиям, вибрационным ударам, центробежным силам, вибрациям и т.д.

3) быстродействие;

4) мощность рассеивания;

5) нагрузочная способность;

6) помехоустойчивость.

Интегральные триггеры. Асинхронные и синхронные триггеры. RS-, JK-, D- и Т-триггеры. Принцип действия, структурные и принципиальные схемы, временные диаграммы работы триггерных схем, их основные параметры. Применение триггерных схем для создания цифровых систем управления.

Триггеры – класс устройств, общим свойством которых является способность длительно оставаться в одном из двух (или нескольких возможных) устойчивых состояний и скачком чередовать их под воздействием внешних сигналов. Одно из основных применений – запоминание информации.

Под памятью триггера подразумевают способность оставаться в заданном состоянии и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит или помнит один разряд двоичного числа.

|

|

|

|||

|

Rn |

Sn |

Q |

|

|

1 |

0 |

0 |

|

|

|

0 |

1 |

1 |

0 |

||

1 |

0 |

0 |

1 |

||

1 |

1 |

н/о |

н/о |

||

2 |

0 |

0 |

н/о |

н/о |

|

0 |

1 |

1 |

0 |

||

1 |

0 |

0 |

1 |

||

1 |

1 |

|

|

||

Недостаток: неопределенное состояние.

Для исключения неопределенного состояния разработаны модификации RS-триггеров, у которых при запрещенных входных комбинациях выходной сигнал принимает следующие значения:

R-триггер - 0

S-триггер - 1

E-триггер – Qn

JK-триггер -

![]()

Триггерные системы - RS-триггер как ячейка памяти и УУ.

J, K, V,

(T)C – внешние

входы; Ra,

Sa –

внешние входы ячейки памяти; Q,

![]() - внешние выходы; S', R'

– внутренние входы.

- внешние выходы; S', R'

– внутренние входы.

Функциональное назначение внешних входов

усл. обозн. |

назначение |

информационные входы |

|

S |

вход раздельной установки триггера в состоянии «1» |

R |

вход раздельной установки триггера в состоянии «0» |

J |

вход установки JK-триггера в состоянии «1» |

K |

вход установки JK-триггера в состоянии «0» |

T |

вход счетного триггера |

D |

вход установки D- или DV-триггера в состоянии «1» или «0» |

управляющие входы |

|

V |

подготовительный вход разрешения приема информации |

C |

вход синхронизации (тактирующий) |

УУ – комбинационное устройство, преобразующее входную информацию в комбинацию сигналов под воздействием которых ячейка памяти принимает одно из двух устойчивых состояний. Изменяя схему УУ и способы ее связи с ячейкой памяти можно получить триггеры с различными функциональными свойствами. Сигнал на информационном входе определяется информацией, которая будет записываться с триггер. С помощью подготовительного сигнала можно в нужный момент прервать действие триггера или группы триггеров, сохраняя информацию на выходе (V-сигнал). Исполнительные сигналы (С-сигнал) задают момент приема входной информации и служат для синхронной работы ряда устройств, образующих функциональные узлы.

Асинхронные и синхронные триггеры

По способу ввода информации бывают асинхронные и синхронные триггеры.

Асинхронные триггеры имеют только информационный вход и срабатывают непосредственно за изменением сигналов на входе.

У синхронных триггеров смены информации на информационных входах недостаточно для срабатывания. Необходим дополнительный импульс, подаваемый на тактирующий вход.

Синхронные сигналы вырабатывают специальными генераторами тактирующих импульсов, которые задают частоту смены информации.

Основной недостаток – незащищенность перед опасными состязаниями сигналов, то есть возникновение временных сдвигов из-за различных задержек распространения сигнала, проходящего по различным цепям, низкая помехоустойчивость.

Срабатывание синхронных триггеров происходит при поступлении тактовых импульсов, длительность которых гораздо меньше их периода. В остальное время на входной сигнал триггер не реагирует, то есть, по сравнению с асинхронным, обладает более высокой помехоустойчивостью.

Способы управления, в зависимости от параметра синхронного входа сигнала, используемых для записи информации, триггеры бывают:

со статическим управлением записью (управление по уровню входного сигнала);

с динамическим управлением записью (по фронту или срезу);

двухступенчатое управление.

Способ управления со статическим управлением записью имеет недостаток – триггер в период действия синхронного импульса ведет себя подобно асинхронному. Срабатывает в момент, когда входной сигнал достигает порогового уровня, то есть продолжает действие тактового импульса. Смена сигнала на информационный вход вызывает новое срабатывание.

При динамическом управлении по фронту или по спаду тактового импульса триггер переключается только при переходе от 0 к 1, или от 1 к 0.

Возможность задержки момента опрокидывания триггера на время длительности тактового импульса позволяют по фронту производить считывание, а по срезу – запись информации.

Двухступенчатые триггеры содержат две ячейки памяти, запись информации в которые происходит последовательно в различные моменты времени. Эту структуру называют «ведущий-ведомый» или MS-структура (Master-Slave).

Первая ступень – промежуточная запись входной информации. Вторая ступень – последовательная запись и хранение.

Формирование нового состояния происходит за два такта.

Ввод информации в ведущую ступень происходит с приходом С1. Перезапись соответственно из ведущего в ведомый – с приходом С2, в это же время происходит обновление информации на Q или .

Управлять можно и одним тактовым импульсом. Запись в ведущую по фронту 0-1, перезапись в ведомую – по фронту 1-0.

Динамические двухступенчатые триггеры называют флип-флоп. Статические – лэт.

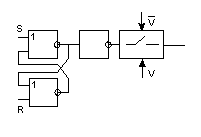

Асинхронные RS-триггеры.

|

|

V |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

1 |

Х |

1 |

1 |

Х |

Х |

0 |

Z |

X – не имеет значения

Z – высокоимпедансное значение выхода (выход отключен от обеих шин источника питания и выходных клемм)

Отсутствие запрещенного состояния обусловлено тем, что не введены выводы .

Синхронные RS-триггеры.

При С = 0 на выходах DD2 и DD1 логическая «1» и RS-триггер на DD3 и DD4 находится в состоянии хранения информации (и не реагирует на изменение R и S). При С = 1, информация на управляющих входах RS-триггера зависит от состояния входа R и S, проинвертированных DD2 и DD1. Входы Sa¯ и Ra¯ предназначены для асинхронной установки триггера в заданное состояние.

Двухступенчатые RS-триггеры.

При высоком уровне на входе С происходит запись в ведущий RS-триггер на DD1 – DD4. Ведомый триггер на DD6 – DD9 блокирован низким уровнем с выходом DD5. При низком уровне на входе С блокируется ведущий триггер (переходит в состояние хранения информации). Высокий уровень с выхода DD5 разрешает перезапись с выхода ведущего на вход ведомого.

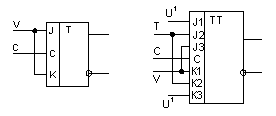

JK-триггеры

JK-триггеры не имеют неопределенных состояний. При всех входных комбинациях, кроме J = K = 1, они действуют подобно RS-триггеру. Причем J играет роль S, а К=R.

При J=K=1 в каждом такте происходит опрокидывание триггера и выходные сигналы меняют свое значение.

JK-триггеры относятся к универсальным устройствам (регистры, счетчики, делители), но кроме того, путем определенных соединений выводов, легко преобразуются в триггеры других типов.

По схеме JK-триггеры отличаются от RS-триггеров наличием обратной связи с выхода на вход, поэтому состояние JK-триггера зависит не только от сигналов на входах J и K, но и от логической связи с ними сигнала с выходов Q и Q¯. Элементы временной задержки играют роль стабилизированного состояния триггера и на его функциональные свойства не влияют. Назначение – создание временного сдвига между моментом ввода входной информации JnQn¯ или KnQn и начала выхода Qn+1 и Qn+1¯.

Без этих цепей во время действия комбинации Jn = Kn = 1 началась бы генерация для предотвращения которой задержка должна быть превыше длительности тактирующих импульсов.

Действие JK-триггера: Qn+1 = Jn Qn¯VKn¯Qn.

Триггер организован по принципу

ведущий-ведомый и имеет по 3 входа J

и K, связанных операцией

&, синхронный вход С, а также асинхронные

входы

![]() и

и

![]() для

установки триггера в состояние «0» и

«1» независимо от сигналов информационных

и тактовых входов.

для

установки триггера в состояние «0» и

«1» независимо от сигналов информационных

и тактовых входов.

1553ТВ6 – 1553ТВ9

У ТВ6 отсутствует вход

![]() ,

у ТВ10 отсутствует вход

,

у ТВ10 отсутствует вход

![]() .

У ТВ11 объединены входы С и

для двух триггеров. У ТВ15 – вход

.

У ТВ11 объединены входы С и

для двух триггеров. У ТВ15 – вход

![]() ,

что позволяет преобразовывать эти

триггеры путем объединения J

и

.

,

что позволяет преобразовывать эти

триггеры путем объединения J

и

.

RS-триггер. ( в скобках R-триггер)

Е-триггер

D-триггеры

D –триггеры

имеют только один информационный вход.

Сигнал на выходе Q в такте

n+1 повторяет входной

сигнал Dn

в предыдущем такте n и

сохраняет это состояние до следующего

тактирующего импульса, то есть

осуществляется задержка на один такт

информации, существующей на входе D

(Delay).

–триггеры

имеют только один информационный вход.

Сигнал на выходе Q в такте

n+1 повторяет входной

сигнал Dn

в предыдущем такте n и

сохраняет это состояние до следующего

тактирующего импульса, то есть

осуществляется задержка на один такт

информации, существующей на входе D

(Delay).

Qn+1 = Dn

ТМ7

D–триггеры серии ТМ7 со статическим управлением внутренними, объединенными попарно, синхронизирующими входами используются в качестве четырехразрядного регистра хранения информации с попарным тактированием разряда, а также в качестве буферной памяти и элемента задержки.

У ТМ5 отсутствует инверсный выход.

ТМ8 – с динамическим управлением.

DV-триггеры

У DV-триггера разрешающий уровень появляется до сигнала. Если V = 1, то триггер функционирует как D-триггер, при V = 0 – переходит в режим хранения информации. Это расширяет функцию D-триггера, который не может хранить информацию более одного такта.

T- и TV-триггеры.

T-триггер – счетный триггер, который имеет один информационный вход и меняет свое состояние всякий раз, когда меняет свое значение входной сигнал. В зависимости от того, фронт или срез используется для управления, считается, что триггер имеет прямой или инверсный вход. Единственный вид триггера, состояние которого определяется состоянием в предыдущем такте, а не от входной информации. Выполняет операцию сложения по модулю 2. Легко получается из D- или JK-триггера.

TV-триггер Сихронный TV-триггер

Несимметричные триггеры (Триггеры Шмита).

![]()

Триггер Шмитта на транзисторах. Нужен для ускорения сигнала.

|

КМОП |

ТТЛ |

R1 |

(10 |

(200 500)k |

R2 |

(0,1 1)k |

(2,2 3,3)k |

Счетчики импульсов. Двоичные счетчики и счетчики с произвольным коэффициентом счета. Принцип действия, структурные и принципиальные схемы, временные диаграммы работы счетчиков, их основные параметры. Разновидности счетчиков, особенности использования счетчиков при создании цифровых систем управления.

Счетчиком называется устройство,

сигналы на выходе которого в определенном

коде отображают число импульсов,

поступивших на счетный вход. Счетчик,

образованный цепочкой из m

триггеров может подсчитать в двоичном

коде

![]() импульсов. Каждый из триггеров называется

разрядом счетчика. Число

импульсов. Каждый из триггеров называется

разрядом счетчика. Число

![]() называется коэффициентом или модулем

счета.

называется коэффициентом или модулем

счета.

Информация может сниматься с прямых и

инверсных выходов триггеров. Когда

число входных импульсов

![]() ,

то при n входа равном

Kсч происходит

переполнение, счетчик возвращается в

нулевое состояние и повторяет цикл.

Каждый разряд счетчика делит частоту

входных импульсов пополам. Для

периодических сигналов

,

то при n входа равном

Kсч происходит

переполнение, счетчик возвращается в

нулевое состояние и повторяет цикл.

Каждый разряд счетчика делит частоту

входных импульсов пополам. Для

периодических сигналов

![]() .

.

Коэффициент счета называют коэффициентом деления, следовательно каждый счетчик может использоваться как делитель частоты.

Обозначения:

СТ 2 – двоичный

СТ10 – двоично-десятичный

СТ2/10 – переключающийся

Основные параметры: емкость и быстродействие. Емкость численно равна коэффициенту счета и характеризует число импульсов, доступных счету за 1 цикл. Быстродействие определяется двумя параметрами: разрешающей способностью и временем установления.

Под разрешающей способностью подразумевают минимальное время между двумя сигналами, при которых еще не возникают сбои в работе tразр.сч.

Время установления кода tуст равно времени между моментом поступления входного сигнала и переходом счетчика в новое состояние.

Счетчики классифицируются следующим образом:

по модулю счета:

двоичные

двоично-десятичные

с произвольным фиксированным модулем счета

с переменным модулем

по направлению счета:

суммирующие

вычитающие

реверсивные

по способу организации внутренних связей

с последовательным переносом (асинхронные)

с параллельным переносом (синхронные)

с комбинированным переносом

кольцевые

Классификационные признаки независимы и могут встречаться в разных комбинациях.

Число, записанное в счетчик, определяется по формуле:

![]()

где m – номер триггера,

Q – может принимать значение «1» и «0»,

![]() – вес младшего разряда.

– вес младшего разряда.

Введением дополнительных логических

связей (обратных и прямых) счетчики

могут быть обращены в недвоичные, для

которых

![]() .

Например, двоично-десятичные с Ксч=10

(двоичный по коду счета, десятичный по

числу состояний). Организуется из 4-х

разрядных двоичных путем исключения

избыточных состояний за счет введения

дополнительных связей. Когда счетчик

используется в качестве делителя,

направление счета роли не играет.

.

Например, двоично-десятичные с Ксч=10

(двоичный по коду счета, десятичный по

числу состояний). Организуется из 4-х

разрядных двоичных путем исключения

избыточных состояний за счет введения

дополнительных связей. Когда счетчик

используется в качестве делителя,

направление счета роли не играет.

Счетчики с последовательным переносом представляют собой цепочку триггеров, в которых импульсы, подлежащие счету, поступают на вход 1-го триггера, а сигнал переноса передается последовательно от одного разряда к другому.

Достоинства: простота схемы и увеличение разрядности.

Недостатки: низкое быстродействие из-за последовательного принципа работы.

Счетчики с параллельным переносом.

У них счетные импульсы подаются одновременно на все тактовые входы, а каждый из триггеров цепочки служит по отношению к последующему только источником информационных сигналов. Срабатывание триггеров параллельного счетчика происходит синхронно, а задержка переключения всего счетчика равна задержке одно триггера.

В счетчике с параллельно-последовательным переносом триггеры соединены в группы так, что отдельные группы образуют счетчики с параллельным переносом внутри группы, а группы соединяются в счетчик с последовательным переносом. Общий коэффициент счета равен произведению коэффициентов счета всех групп.

Счетчики ТТЛ с последовательным переносом

Состоят из 4-х одинаковых JK-триггеров, которые могут использоваться как по прямому назначению, так и в качестве ТК-триггеров. Переброс осуществляется по срезу. Три триггера соединяются в последовательную цепочку, 4-й самостоятельно.

ИЕ5

ИЕ4 (ИЕ5)

ИЕ4

ИЕ2

Счетчик ТТЛ с параллельным переносом

Двоично-десятичный суммирующий счетчик.

Имеет 4 входа предварительной установки

счетчика при V1=0 независимо

от предыдущего состояния и сигналов на

входах С, V2, V3.

При

![]() происходит нормальный счет, причем

переброс осуществляется по переднему

фронту. Счет либо от нуля, либо от

информации, записанной на входы D.

происходит нормальный счет, причем

переброс осуществляется по переднему

фронту. Счет либо от нуля, либо от

информации, записанной на входы D.

При «1» на входе V3 на выходе Р формируется импульс логической «1» (перенос) с девятым входным импульсом.

V3 – разрешает перенос.

V2=0 – прерывает счет, однако информация на выходах при этом сохраняется.

V1 – предварительная запись.

Быстродействующий синхронный многокаскадный счетчик

Синхронный многокаскадный

ИЕ6, ИЕ7

4-х разрядные быстродействующие реверсивные счетчики-делители с параллельным переносом между разрядами. По входам предварительной информации D ввод производится при низком уровне на С. Входы +1 и -1 счетные. Последовательность входных импульсов подается на один из этих входов в зависимости от того, в каком направлении (прямом / обратном) требуется вести счет. На выходе ≥15 (≥9) появляется импульс при выходной комбинации «1111» («1001»). На выходе ≤0 – при «0000». Меньше нуля – для режима вычитания.

Наращивание счетчиков

Последовательный.

Последовательный быстродействующий

ИЕ8

6-разрядный двоичный делитель числа входных импульсов с перестраиваемым коэффициентом деления или программируемый преобразователь кодов в число импульсов.

ИЕ14 (ИЕ15)

Ф ункциональные

микросхемы аналогичны ИЕ2 и ИЕ5. Имеют

входы предварительной установки D

высоким уровнем на Е.

ункциональные

микросхемы аналогичны ИЕ2 и ИЕ5. Имеют

входы предварительной установки D

высоким уровнем на Е.

Регистры. Параллельные, последовательные и параллельно-последовательные регистры. Структурные схемы, особенности работы и основные параметры регистров различных типов. Применение регистров в цифровых системах управления.

Регистры – функциональные узлы, предназначенные для приема, хранения, передачи и преобразования информации.

Используются в качестве управляющих и запоминающих устройств генераторов и преобразователей кодов, счетчиков и делителей частоты, узлов временной задержки. Строятся на синхронных триггерах с динамическим или статическим управлением. Занесение информации в регистр называется операцией ввода или записью. Выдача информации к внешним устройствам характеризует операцию вывода или считывание. Запись информации в регистр не требует его предварительного обнуления.

Регистры делятся на:

сдвигающие

накопительные (памяти, хранения)

универсальные.

Регистры памяти предназначены для хранения двоичной информации небольшого объема в течение короткого промежутка времени. Представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод и вывод информации производится одновременно во всех разрядах параллельного кода. Ввод обеспечивается тактовым командным импульсом. Считывание может производиться в прямом и обратном коде (с инверсных выходов).

Регистры сдвига. Сущность сдвига – с приходом каждого тактового импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования «0» и «1». При сдвиге вправо бит из более старшего разряда сдвигается в младший. При сдвиге влево – наоборот.

Сдвигающие регистры классифицируются:

по способу ввода и вывода информации на:

параллельные

последовательные

комбинированные

по направлению сдвига на:

однонаправленные

реверсивные

Обозначаются: RG ←, → и ↔ (влево, вправо и реверсивные)

Универсальные в зависимости от управляющих сигналов могут выполнять как операцию хранения, так и сдвиг.

4-х разрядный сдвигающий регистр с последовательным вводом.

Допустим, что в регистр последовательно вводится начиная с младшего разряда двоичный код 1101, который поступает с внешнего устройства синхронно с тактовыми импульсами. С первым тактовым импульсом в триггер DD1 записывается «1» младшего разряда. Со следующим тактовым импульсом эта «1» будет сдвинута в триггер DD2 и окажется на его выходе. Одновременно в 1-ый триггер запишется «0». После 4-х тактовых импульсов параллельный код на выходах Q1—Q4 будет соответствовать последовательному входному. После пятого тактового импульса сигнал, бывший на выходе Q4 выводится из регистра и пропадает. После 8 тактов регистр полностью очищен.

Дополнительная логика позволяет вводить информацию параллельно и снимать последовательно.

Сдвигающийся регистр может быть использован в качестве кольцевого счетчика или счетчика Джонса, который применяется для последовательного вывода информации без ее стирания.

Для этого информация с выхода регистра по цепи ОС снова вводится на вход. Пока на V единица, информация вводится в регистр по входу D и обратная связь не действует. За n тактов запоминается n разрядный код. Затем на V устанавливается «0» тактовыми импульсами по входу С. Информация с выхода Qn снова вводится в регистр одновременным последовательным (возможно и параллельным) считыванием и через n тактов находится в исходном состоянии.

ИР-1

Ч етырехразрядный

регистр сдвига с последовательным или

параллельным вводом информации и

параллельным выводом (может быть и

последовательным).

Он может выполнять:

етырехразрядный

регистр сдвига с последовательным или

параллельным вводом информации и

параллельным выводом (может быть и

последовательным).

Он может выполнять:

ввод информации параллельным кодом

ввод информации последовательным кодом со сдвигом влево

ввод информации последовательным кодом со сдвигом вправо

хранение.

Регистр имеет:

2 тактовых входа С1 и С2.

управляющий вход выбора режима V2

5 информационных входов (V1 для ввода в последовательном коде, D1-D4 для записи в параллельном коде)

4 выхода Q1-Q4.

Ввод информации параллельным кодом осуществляется при V2=1 и C2=0. Сдвиг информации в триггерах происходит по перепаду 1-0 на С2. Входы V1 и C1 при этом блокированы. В этом же режиме по входам V2, С2 производится преобразование последовательного кода в параллельный со сдвигом влево. В этом случае поток информации происходит в обратном направлении. Для этого соединяют Q4 – D3, Q3 – D2, Q2 – D1. Информация подается на D4. Сдвиг влево по перепаду 1-0 на С2.

V2 |

V1 |

С1 |

С2 |

|

1 |

X |

X |

10 |

запись параллельного кода, сдвиг влево |

0 |

вход |

10 |

X |

запись последовательного кода, сдвиг вправо |

Во избежание сбоев при смене состояний V2 должна происходить при C1=C2=0.

Ввод информации последовательным кодом: входная информация подается на V1, а тактовые импульсы на С1. Сдвиг вправо происходит при каждом перепаде 10 тактовых импульсов.

ИР-13

У ниверсальный

8-ми разрядный регистр сдвига.

ниверсальный

8-ми разрядный регистр сдвига.

R |

С |

S1 |

S0 |

DR |

DL |

Режим работы |

1 |

01 |

1 |

1 |

* |

* |

параллельный ввод |

1 |

1 |

0 |

0 |

* |

* |

хранение |

1 |

1 |

1 |

0 |

* |

0 |

сдвиг влево Q8=0 Q8=1 |

1 |

1 |

1 |

0 |

* |

1 |

|

1 |

1 |

0 |

1 |

0 |

* |

сдвиг вправо Q1=0 Q1=1 |

1 |

1 |

0 |

1 |

1 |

* |

|

0 |

* |

* |

* |

* |

* |

установка нуля |

ИР-15

4-х разрядный регистр хранения.

П ри

Е1=Е2=0 – параллельный ввод, иначе хранение.

ри

Е1=Е2=0 – параллельный ввод, иначе хранение.

EZ – выводы.

При EZ1= EZ2=0 – вывод информации, иначе выходы отключены от шин питания и от схемы управления.

ИР-17

12-разрядный регистр последовательного приближения

ИР-26

Регистровый файл на четыре 4-х разрядных слова.

Другие регистры:

ИР-11 – 4-х разрядный сдвиговый регистр.

ИР-12 – 4-х разрядный параллельный сдвиговый регистр.

ИР-16 – универсальный 4-х разрядный сдвиговый регистр.

ИР-18 – 6-х разрядный параллельный регистр с D-триггерами.

ИР-19 – 4-х разрядный параллельный регистр с O-триггерами.

ИР-20 – 4-х разрядный двухкодовый регистр.

ИР-21 – 4-х разрядное сдвигающее устройство.