- •Элемент или

- •Счетчики

- •Классификация счётчиков

- •Суммирующий последовательный счётчик

- •Вычитающий последовательный счётчик

- •Реверсивный последовательный счётчик

- •Параллельный суммирующий счётчик

- •Счетчики с параллельным переносом

- •Разработка принципиальной схемы Формирователь импульсов

- •Составление структурной схемы счётчика

- •Составление функциональной схемы счётчика

- •Простейшие одноразрядные счетчики импульсов

- •Регистры.

- •Преобразователем кодов

Регистры.

Регистрами называются последовательностные цифровые устройства, выполняющие функции приема, хранения и передачи информации. Информация в регистре хранится в виде двоичного кода, т.е. представлена комбинацией сигналов логического нуля и логической единицы. Каждому разряду кода, записанному в регистр, соответствует свой разряд регистра, как правило, на основе триггеров RS-, D- или JK-типа. Основным классификационным признаком, по которому различают регистры, является способ записи информации или кода числа в регистр. По этому признаку можно выделить регистры следующих типов:

параллельные;

последовательные;

последовательно-параллельные.

В параллельные регистры запись (считывание) числа осуществляется параллельным кодом, т.е. во все разряды регистра одновременно. Последовательные регистры характеризуются последовательной записью (считыванием) кода числа, начиная с младшего разряда или старшего путем последовательного сдвига кода тактирующими импульсами. В последовательно-параллельных регистрах ввод или вывод информации может осуществляться как в параллельном, так и в последовательном кодах.

Время ввода числа в регистр параллельного типа равно времени ввода одного разряда. Время ввода числа в регистр последовательного типа равно m×T, где m - число разрядов вводимого числа, а T - период следования тактирующих сигналов, осуществляющих ввод (вывод) информации.

По способу представления вводимой информации различают регистры однофазного и парафазного типа. В однофазных регистрах информация вводится по одному каналу (прямому или инверсному). Информация на выходе представлена в прямом или в обратном коде. В парафазных регистрах ввод информации осуществляется по двум каналам одновременно (прямому и инверсному), т.е. информация представлена одновременно в прямом и обратном кодах. Информация на выходе, как правило, также представляется в прямом и инверсном кодах.

Параллельные регистры. Параллельный регистр используется для кратковременного хранения чисел, представленных в параллельном двоичном коде. Поэтому параллельные регистры называются еще регистрами памяти. Рассмотрим способы построения регистров памяти на триггерах RS-типа. Каждый триггер служит для хранения одного разряда числа, значит, для хранения m-разрядного двоичного числа необходимо иметь m RS-триггеров. Как следует из таблицы переходов RS-триггера, для записи единицы необходимо подавать единицу на вход S и нуль на вход R, а для записи нуля – наоборот – единицу на входR и нуль на вход S, т.е. информация должна поступать на оба входа RS-триггера. Полученный регистр будет парафазным, причем вход S - прямой, а вход R - инверсный. Для синхронной записи во все триггеры одновременно, их тактовые входы необходимо объединить в одну шину (рис. 5.20).

Рис. 5.20. Структурная схема параллельного парафазного регистра на синхронных RS-триггерах.

Чтобы получить нулевой сигнал на выходе, при Sn=0, необходимо чтобы Qn=0, т.е. перед записью необходимо обнулить триггер. Для этого нужно объединить все входы R и при подаче на информационные входы S сигнала с уровнем логического нуля, подать на объединенные входы R логические единицы (рис. 5.21). Таким образом, осуществляется предварительная установка триггеров в нулевое состояние. Если теперь на входы S соответствующих триггеров подать значения записываемых разрядов исходного кода, то они зафиксируются на выходах триггеров.

Рис. 5.21. Структурная схема параллельного однофазного регистра на синхронных RS-триггерах.

Таким образом, при реализации регистров на основе RS-триггеров требуется подача разрядов исходного числа в прямом и инверсном коде, либо предварительное обнуление всех триггеров, что не всегда является удобным. В этом отношении удобны регистры на D-триггерах. В них информация может быть установлена по одному входу и без предварительной установки в нуль

Рис. 5.22. Структурная схема параллельного регистра на D-триггерах.

Последовательные регистры. Последовательный регистр предназначен для кратковременного хранения информации, но, в отличие от параллельного регистра, в нем осуществляется логическая операция сдвига кода хранимого числа на любое количество разрядов. Ввод информации в последовательный регистр осуществляется по одному последовательному каналу V. Сдвиг кода числа происходит с помощью синхронизирующих импульсов С, в результате подачи которых осуществляется сдвиг всех разрядов кода числа со входа к выходу или наоборот. Как и в случае параллельных регистров, последовательный регистр может быть синтезирован на базе триггеров RS-типа (JK-типа), но наиболее удобным для этих целей является использование D-триггеров. (рис. 5.23). Из рисунка видно, что информация с первым тактирующим импульсом с входа V передается на выход первого и вход второго триггеров. С приходом второго тактирующего импульса информация из первого триггера перепишется на выход второго триггера. На выход первого триггера запишется новое значение с входа V. Таким образом, будет осуществляться сдвиг исходного кода вправо. Отсюда последовательные регистры называются еще регистрами сдвига. Информация выводится из триггера по одному выходу Q.

Рис. 5.23. Структурная схема последовательного регистра.

Для построения последовательного реверсивного регистра, в котором код числа может сдвигаться как влево, так и вправо, необходимо между триггерами регистра включить устройства управления направлением сдвига. Эти устройства в зависимости от значения управляющих сигналов «сдвиг вправо» и «сдвиг влево» должны переключать входы каждого триггера регистра либо к выходам предыдущего, либо к выходам последующего триггера (рис. 5.24). Поскольку элемент 2И-ИЛИ-НЕ, выполняющий роль коммутатора, инвертирует значения сигналов, то для подачи на входы соответствующих разрядов сдвигаемого кода в прямом виде, необходимо использовать инверсные выходы этих триггеров. Информацию на самый первый элемент 2И-ИЛИ-НЕ с входа V последовательного ввода необходимо подавать через инвертор. В практических схемах для упрощения процесса управления режимами направления сдвига вместо двух сигналов «сдвиг вправо» и «сдвиг влево», используется только один из этих сигналов. Второй сигнал формируется через инвертор.

Рис. 5.24. Структурная схема последовательного реверсивного регистра.

Последовательные регистры находят ограниченное применение. Широкое распространение получили последовательно-параллельные регистры. На их базе строятся преобразователи кодов из последовательного в параллельный и из параллельного в последовательный. Для реализации параллельного вывода информации в последовательном регистре достаточно использовать выходы Qi всех триггеров. Чтобы реализовать ввод информации как в последовательном, так и в параллельном виде, можно использовать D-триггеры с асинхронной установкой в нуль или единицу. Пример такой структуры приведен на рис. 5.25.

Рис. 5.25. Структурная схема последовательно-параллельного регистра.

Как

и в последовательном регистре, ввод

информации в последовательном коде

осуществляется по входу V.

Для тактирования сдвига синхровходы

всех триггеров объединены. При этом,

для возможности введения кода числа в

параллельном виде используются элементы

И-НЕ ЛЭ1i и

ЛЭ2i в

своих разрядах. Элемент ЛЭ1i осуществляет

функцию стробирования и инвертирования

разряда Di при

единичном уровне управляющего сигнала

«параллельная запись». В результате

на вход S установки

в единицу триггера Тi проходит

инверсное значение разряда ![]() параллельного

кода числа только в том случае, если

сигнал разрешения на линии «параллельная

запись» имеет единичное значение.

Элемент ЛЭ2iвыполняет

функцию инвертирования сигнала с

элемента ЛЭ1i и

передачи его на вход R сброса

триггера Тi также

по активному уровню сигнала разрешения

параллельной записи. В результате

парафазный код всех разрядов параллельного

кода проходит на соответствующий

триггер только при активном уровне

сигнала разрешения параллельной записи.

Поскольку элементы ЛЭiимеют

инверсные выходы, то триггеры Тi должны

иметь инверсные входы R и S.

параллельного

кода числа только в том случае, если

сигнал разрешения на линии «параллельная

запись» имеет единичное значение.

Элемент ЛЭ2iвыполняет

функцию инвертирования сигнала с

элемента ЛЭ1i и

передачи его на вход R сброса

триггера Тi также

по активному уровню сигнала разрешения

параллельной записи. В результате

парафазный код всех разрядов параллельного

кода проходит на соответствующий

триггер только при активном уровне

сигнала разрешения параллельной записи.

Поскольку элементы ЛЭiимеют

инверсные выходы, то триггеры Тi должны

иметь инверсные входы R и S.

Если выход последнего триггера соединить с входом первого, то получится кольцевой регистр сдвига. Записанная в его разряды информация под воздействием сдвигающих импульсов будет циркулировать по замкнутому кольцу. Кольцевой регистр иначе называется кольцевым счетчиком. Его коэффициент пересчета равен числу разрядов n последовательного кода. Единица, записанная в один из разрядов, периодически будет появляется в нем после того, как будут поданы n сдвигающих импульсов. В условном графическом обозначении функция регистра задается символами «RG», а в маркировке микросхем – символами «ИР».

Универсальные регистры

Регистры сдвига выполняют обычно как универсальные последовательно-параллельные микросхемы. Это связано с необходимостью записи в регистр параллельного двоичного кода при преобразовании параллельного кода в последовательный.

Переключение регистра из параллельного режима работы в последовательный и наоборот осуществляется при помощи мультиплексора (коммутатора). Использование коммутатора позволяет входы триггеров регистра либо подключать к внешним выводам микросхемы, либо подключать к выходу предыдущего триггера.

Напомню, что двухвходовый мультиплексор можно реализовать при помощи логических элементов “2И-2ИЛИ”. Элементы “И” при этом работают в качестве электронных ключей, а элементы “ИЛИ” объединяют их выходы.

Схема универсального регистра с использованием коммутаторов на логических элементах “2И-2ИЛИ” приведена на рисунке 5.

Рисунок 5. Схема универсального регистра.

В этой схеме для переключения регистра из последовательного режима работы в параллельный используется вывод V. Подача на этот вход единичного потенциала превращает схему в параллельный регистр. При этом на входы ключей, подключенных к информационным входам D, подаётся единичный потенциал. Это приводит к тому, что сигналы с входов параллельной записи данных поступают на входы логических элементов “ИЛИ”, а на входы ключей, подключенных к выходам предыдущих триггеров, подаются нулевые потенциалы. То есть на выходах этих ключей будут присутствовать нулевые потенциалы, и они не будут мешать работе.

Подача на вход V нулевого потенциала приводит к отключению входов параллельных данных от входов триггеров. Сигналы же с выхода предыдущего триггера свободно проходит через верхние логические элементы “И” на вход последующего триггера, так как на его второй вход подаётся единичный потенциал.

Инверторы на входах V и C использованы для усиления входного сигнала по току. В результате входной ток микросхемы будет равен не суммарному току четырёх логических элементов “И”, а входному току инвертора.

Условно-графическое изображение универсального регистра приведено на рисунке 6. Вход последовательного ввода данных на этом рисунке обозначен как DI и отделён от других групп входов чертой. Точно так же выделены в отдельные группы и входы управления V и синхронизации C.

Рисунок 6. Обозначение универсального регистра на принципиальных схемах.

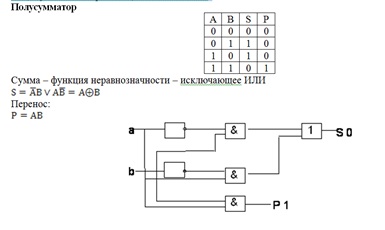

Типы сумматоров. Принцип построения параллельного сумматора с параллельным переносом

Сумматоры выполняют арифметическое сложение и вычитание двоичных чисел. Являются ядром АЛУ. Аппаратная сложность и быстродействие сумматора – важные параметры, поэтому разработано множество вариантов сумматоров

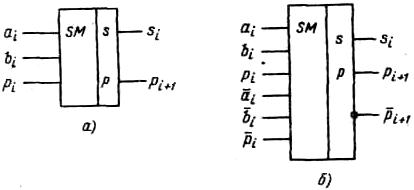

Типы сумматоров: полусумматоры, одноразрядные полные, для последовательных операторов, для параллельных операндов с последовательным переносом, для параллельных операндов с параллельным переносом, групповой структуры с цепным переносом, групповой структуры с параллельным переносом, с условным переносом, накапливающий

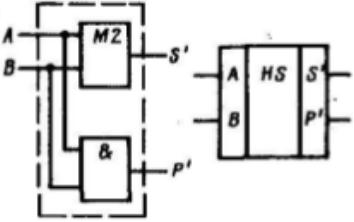

Одноразрядный сумматор

Если складываются два многоразрядных двоичных числа, полусумматор можно использовать только для младшего разряда. Во всех остальных случаях складываются 3 числа, так как может произойти перенос из предыдущего разряда

б) – с прямыми и инверсными входами

входы |

выходы |

||||||

слагаемые |

перенос |

сумма |

перенос |

||||

A |

B |

Pi–1 |

Si |

Pi |

|||

0 |

0 |

0 |

0 |

0 |

|||

0 |

1 |

0 |

1 |

0 |

|||

1 |

0 |

0 |

1 |

0 |

|||

1 |

1 |

0 |

0 |

1 |

|||

0 |

0 |

1 |

1 |

0 |

|||

0 |

1 |

1 |

0 |

1 |

|||

1 |

0 |

1 |

0 |

1 |

|||

1 |

1 |

1 |

1 |

1 |

|||

Минимизация функций:

![]()

По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:

последовательные, в которых обработка чисел ведётся поочерёдно, разряд за разрядом на одном и том же оборудовании;

параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование.

Параллельный сумматор в простейшем случае представляет собой n одноразрядных сумматоров, последовательно (от младших разрядов к старшим) соединённых цепями переноса. Однако такая схема сумматора характеризуется сравнительно невысоким быстродействием, так как формирование сигналов суммы и переноса в каждом i-ом разряде производится лишь после того, как поступит сигнал переноса с (i-1)-го разряда.Таким образом, быстродействие сумматора определяется временем распространения сигнала по цепи переноса. Уменьшение этого времени — основная задача при построении параллельных сумматоров.

Для уменьшения времени распространения сигнала переноса применяют: конструктивные решения, когда используют в цепи переноса наиболее быстродействующие элементы; тщательно выполняют монтаж без длинных проводников и паразитных ёмкостных составляющих нагрузки и (наиболее часто) структурные методы ускорения прохождения сигнала переноса.

По способу организации межразрядных переносов параллельные сумматоры, реализующие структурные методы, делят на сумматоры:

с последовательным переносом;

с параллельным переносом;

с групповой структурой;

со специальной организацией цепей переноса.

Важнейшими параметрами сумматоров являются:

разрядность;

статические параметры: Uвх, Uвх, Iвх и так далее, то есть обычные параметры интегральных схем;

динамические параметры. Сумматоры характеризуются четырьмя задержками распространения:

от подачи входного переноса до установления всех выходов суммы при постоянном уровне на всех входах слагаемых;

от одновременной подачи всех слагаемых до установления всех выходов суммы при постоянном уровне на входе переноса;

от подачи входного переноса до установления выходного переноса при постоянном уровне на входах слагаемых;

от подачи всех слагаемых до установления выходного переноса при постоянном уровне на входах слагаемых.