- •Оперативная память эвм. Структура запоминающего устройства с произвольным доступом

- •Оперативная память эвм. Структура запоминающего устройства с двухкоординатной выборкой

- •Оперативная память эвм. Структура запоминающего устройства со стековой организацией

- •Оперативная память эвм. Структура запоминающего устройства с магазинной организацией

- •Организация оперативной памяти. Многоблочная память

- •Организация оперативной памяти с многоканальным доступом. Схема анализа приоритета при подключении каналов

- •Организация памяти. Иерархические уровни. Двух- и трехуровневая организация памяти

Оперативная память эвм. Структура запоминающего устройства с произвольным доступом

Запоминающее устройство с произвольным доступом (сокращённо ЗУПД; также Запоминающее устройство с произвольной выборкой, сокращённо ЗУПВ; RandomAccessMemory) – один из видов памяти компьютера, позволяющий единовременно получить доступ к одной ячейке(всегда за одно и то же время, вне зависимости от расположения) по её адресу на чтение или запись.

Назначение ОЗУ

Хранение данных и команд для дальнейшей их передачи процессору для обработки. Информация может поступать из оперативной памяти не сразу на обработку процессору, а в более быструю, чем ОЗУ, кэш-память процессора.

Хранение результатов вычислений, произведенных процессором.

Считывание (или запись) содержимого ячеек.

Особенности работы ОЗУ

Оперативная память может сохранять данные лишь при включенном компьютере. Поэтому при его выключении обрабатываемые данные следует сохранять на жестком диске или другом носителе информации. При запуске программ информация поступает в ОЗУ, например, с жесткого диска компьютера. Пока идет работа с программой она присутствуют в оперативной памяти (обычно). Как только работа с ней закончена, данные перезаписываются на жесткий диск. Другими словами, потоки информации в оперативной памяти очень динамичны.

ОЗУ представляет собой запоминающее устройство с произвольным доступом. Это означает, что прочитать/записать данные можно из любой ячейки ОЗУ в любой момент времени. Для сравнения, например, магнитная лента является запоминающим устройством с последовательным доступом.

Логическое устройство оперативной памяти

Оперативная память состоит их ячеек, каждая из которых имеет свой собственный адрес. Все ячейки содержат одинаковое число бит. Соседние ячейки имеют последовательные адреса. Адреса памяти также как и данные выражаются в двоичных числах.

Обычно одна ячейка содержит 1 байт информации (8 бит, то же самое, что 8 разрядов) и является минимальной единицей информации, к которой возможно обращение. Однако многие команды работают с так называемыми словами. Слово представляет собой область памяти, состоящую из 4 или 8 байт (возможны другие варианты).

Типы оперативной памяти

Принято выделять два вида оперативной памяти: статическую (SRAM) и динамическую (DRAM). SRAM используется в качестве кэш-памяти процессора, а DRAM - непосредственно в роли оперативной памяти компьютера.

SRAM состоит из триггеров. Триггеры могут находиться лишь в двух состояниях: «включен» или «выключен» (хранение бита). Триггер не хранит заряд, поэтому переключение между состояниями происходит очень быстро. Однако триггеры требуют более сложную технологию производства. Это неминуемо отражается на цене устройства. Во-вторых, триггер, состоящий из группы транзисторов и связей между ними, занимает много места (на микроуровне), в результате SRAM получается достаточно большим устройством.

В DRAM нет триггеров, а бит сохраняется за счет использования одного транзистора и одного конденсатора. Получается дешевле и компактней. Однако конденсаторы хранят заряд, а процесс зарядки-разрядки более длительный, чем переключение триггера. Как следствие, DRAM работает медленнее. Второй минус – это самопроизвольная разрядка конденсаторов. Для поддержания заряда его регенерируют через определенные промежутки времени, на что тратится дополнительное время.

Основными характеристиками ОЗУ являются информационная емкость и быстродействие. Емкость оперативной памяти на сегодняшний день выражается в гигабайтах.

SRAM на биполярных транзисторах представляет собой матрицу запоминающих элементов (ЗЭ), каждый из которых может быть установлен в одно из устойчивых состояний. Таким элементом обычно является триггер или вентиль. На одном кристалле биполярных ИС можно изготовить ОЗУ на 1024 бита, с временем выборки менее 100 нс, снабжённые схемами управления. Одной из основных частей ЗУ является матрица-накопитель, в которой, естественно, и происходит накопление информации. Построение (организация) матрицы определяется способом выборки (опроса) ЗЭ при записи или считывании.

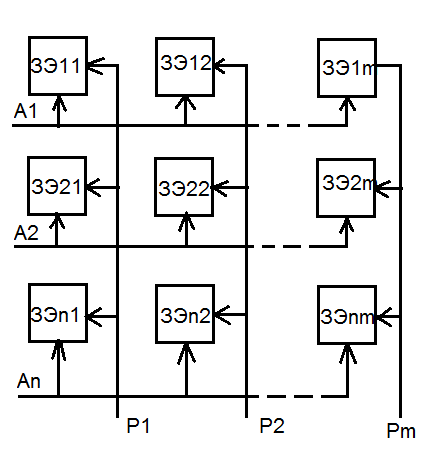

Рисунок Структура ЗУ с пословной выборкой

В структурной схеме матрицы с пословной выборкой и одной ступенью дешифрации (рисунок) одна строка образует слова из mразрядов. На схеме символами A1, A2, … Anобозначены адресные, а Р1, Р2, … Рm–разрядные шины. Как видно из схемы, адресные шины электрически связаны с каждым ЗЭ данного слова, в то время как разрядная шина имеет связь с ЗЭ одного разряда всех слов. При наличии в адресной шине Aiсигнала, соответствующего уровню 1, состояние каждого из ЗЭ в слове по адреcу Aiможет быть считано по разрядным шинам Р1, Р2, … Рm. Если необходимо записать информацию по выбранному адресу Ai,то разрядным шинам Р1, Р2, … Рm, подаётся, в зависимости от кода информации сигнал 1 или 0 на каждый из ЗЭ Ai1, Ai2, … Aim.На структурной схеме для простоты не показаны схема управления матрицей (дешифратор с адресными формирователями, усилители считывания и записи), которые для сокращения числа выводов корпуса включаются в состав ИС и изготавливаются на одном кристалле вместе со схемой матрицей.

Простейшим ЗЭ запоминающего устройства с пословной выборкой является RS-триггер, который может быть построен из двух инверторов (рис. 6.7 а). Эмиттеры 1 МЭТ VT1 и VT2 соединены с адресной шиной А1, потенциал на которой в установившемся состоянии является самым низким потенциалом схемы. Разрядные шины Piи Pjсоединены с эмиттерами 2 триггеров VT1 и VT2 соответственно.

На разрядную шину Piподаётся опорное напряжение, общее для всех ЗЭ матрицы. Соотношение между опорным напряжением Uоп, напряжением Uр, подаваемым в разрядную шину Pjи напряжением Ua, подаваемым в адресную шину, определяет режим работы ЗЭ: хранение информации, запись или считывание.

Рассмотрим работу ЗЭ в каждом из трёх режимов.

Режим хранения информации характеризуется соотношением:

Ua< (Uоп = Up)

Схема находится в одном из устойчивых состояний, при котором открыт триггер VT1 или VT2 в зависимости от того, какая информация была предварительно записана: 1 или 0. Ток протекает по эмиттеру 1 одного из триггеров, в то время, как эмиттеры 2 отключены.

Рассмотрим режим считывания. Пусть в RS-триггере была записана единица. Считаем, что при этом транзистор VT2 открыт, а VT1- закрыт. За 1 принимаем наличие тока в цепи открытого триггера. Чтобы транслировать эту информацию в разрядную шину, необходимо переключить цепи эмиттеров: закрыть схему по эмиттерам1 и открыть по эмиттерам2, оставив состояние триггера без изменения (после смены эмиттеров попрежнему VT2 открыт, VT1- закрыт). Для этого необходимо изменить напряжение на адресной шине таким образом, чтобыUa> (Up = Uоп). В этом случае ток через эмиттер 2 открытого триггера VT2 потечёт в разрядную шину Pj. Наличие тока в разрядной шине соответствует считываемой 1, отсутствие тока в разрядной шине (при закрытомVT2 и открытомVT1)определяет считывание 0.

Режим записи зависит от состояния, в которое необходимо установить ЗЭ. Если триггер находится в состоянии 1 (триггер VT2 открыт, VT1 – закрыт), то для записи 0 необходимо по разрядной шине Pjподать потенциал Up, превышающий опорный Uоп. При этом триггер перейдёт в новое состояниетранзисторVT2 закроется, а VT1 - откроется. Таким образом, условие записи 0 имеет вид:Ua> (Up = Uоп) и Up>Uоп, а условие записи 1: Ua> (Up = Uоп) и Up<Uоп.

Временная диаграмма работы ЗЭ показана ниже. Таким образом, у подобных ЗЭ на биполярных транзисторах главные параметры – ток считыванияIсч и напряжение записи Uзп.

Время выборки данных по ЗУ небольшой емкости на биполярных схемах ТТЛ может составить 30-40нс. Важный параметр ЗУ – потребляемая мощность. Она может составлять 0,5 – 1,5 мВт/бит.

Запоминающий элемент ЗУ с пословной выборкой,где: а – RS- триггер в качестве запоминающего элемента, б – временная диаграмма работы ЗЭ.