- •Автоматизація проектування комп’ютерних систем

- •Лабораторна робота № 1. Середовище розробки Aldec Active-hdl

- •Лабораторна робота № 2. Проектування блоку регістрової пам’яті.

- •Лабораторна робота № 3. Проектування арифметико-логічного пристрою з акумулятором Мета роботи:

- •Загальні відомості

- •Лабораторна робота № 4. Проектування керуючого пристрою. Мета роботи:

- •Загальні відомості

- •Цикл if (вибірка інструкції)

- •Цикл ex (обчислення результату)

- •Абстрактні автомати

- •Хід роботи

Абстрактні автомати

При проектуванні керуючих пристроїв доцільно застосувати поняття Скінченного автомату – абстракції, що описує зміни стану об'єкта, залежно від поточного стану та зовнішньої інформації.

Автомат Мура — скінченний автомат, вихід якого залежить від його стану і не залежить від його входу.

Автомат Мілі — скінченний автомат, вихід якого визначаються його станом, та вхідними сигналами.

Проектування керуючого пристрою здійснимо на основі автомата Мілі. Використаємо засіб State Editor, призначений для проектування керуючих автоматів за допомогою графічного редактора з подальшою автоматичною трансляцією з графічного відображення у VHDL-опис.

При реалізації засобами VHDL, відобразимо функцію переходів між станами та функцію виходів у вигляді двох процесів. Функція переходів забезпечує коректне встановлення стану керуючого пристрою при надходженні сигналу початкового скиду (reset) та подальше переключення станів. Функція виходів активує потрібні керуючі сигнали на кожному такті згідно правил описаних вище. Керуючі сигнали надходять до операційного пристрою та основної пам’яті й забезпечують виконання кожної інструкції з набору мікропроцесора.

Хід роботи

Для кодування інструкцій процесора доцільно використати мнемонічні позначення. Константи-мнемоніки додати до package-файлу, створеного в лаб. роботі 3:

-- Constants for Instruction Codes

CONSTANT CLEAR_C: std_logic_vector (7 DOWNTO 0):= "00000000";

CONSTANT SET_C: std_logic_vector (7 DOWNTO 0):= "00000001";

CONSTANT SKIP_C: std_logic_vector (7 DOWNTO 0):= "00000010";

CONSTANT SKIP_Z: std_logic_vector (7 DOWNTO 0):= "00000011";

CONSTANT JMP_IX: std_logic_vector (7 DOWNTO 0):= "00000100";

CONSTANT LDA_IMM: std_logic_vector (3 DOWNTO 0):= "0001";

CONSTANT ADDA_IMM: std_logic_vector (3 DOWNTO 0):= "0010";

CONSTANT STA_RG: std_logic_vector (3 DOWNTO 0):= "0011";

CONSTANT LDA_RG: std_logic_vector (3 DOWNTO 0):= "0100";

CONSTANT ADDA_RG: std_logic_vector (3 DOWNTO 0):= "0101";

CONSTANT XORA_RG: std_logic_vector (3 DOWNTO 0):= "0110";

CONSTANT TESTA_RG: std_logic_vector (3 DOWNTO 0):= "0111";

CONSTANT STORE: std_logic_vector (3 DOWNTO 0):= "1000";

CONSTANT LOAD: std_logic_vector (3 DOWNTO 0):= "1001";

CONSTANT SET_IXH: std_logic_vector (3 DOWNTO 0):= "1010";

CONSTANT SET_IXL: std_logic_vector (3 DOWNTO 0):= "1011";.

Створити нову діаграму станів:

File- New – State Diagram

Створити пристрій з назвою Control, входами

clock: IN std_logic;

reset: IN std_logic;

MEM_read: OUT std_logic;

inc_pc:OUT std_logic;

ld_ir: OUT std_logic;

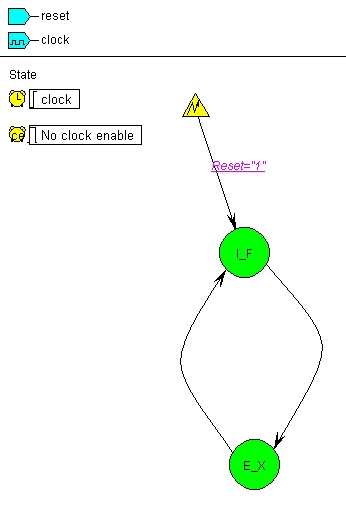

Перейменувати Змінну стану Sreg0 в State. Використовуючи палітру інструментів FSM Toolbar або меню FSM, додати до діаграми станів:

Стани (State

)

I_F та E_X;

)

I_F та E_X;Переходи (Transitions

)

між станами I_F->E_X та навпаки

)

між станами I_F->E_X та навпакиІндикатор початкового Стану (Reset/Initial State Indicator,

)

з переходом до стану стану I_F, за умовою

(condition,

)

з переходом до стану стану I_F, за умовою

(condition,

) Reset ="1" (рис. 4).

) Reset ="1" (рис. 4).

Рис. 5. Діаграма станів керуючого пристрою.

Змінити тип сигналу Reset на асинхронний (не залежить від тактового входу Clock).

Меню FSM – Code Generation Settings – Закладка General –HDL Style – вибрати опцію «Two Processes» - Генерувати один процес для переходу між станами і другий для реалізації керуючих сигналів.

Меню FSM – Generate Code – Згенерувати HDL код, ознайомитися із ним, провести компіляцію.

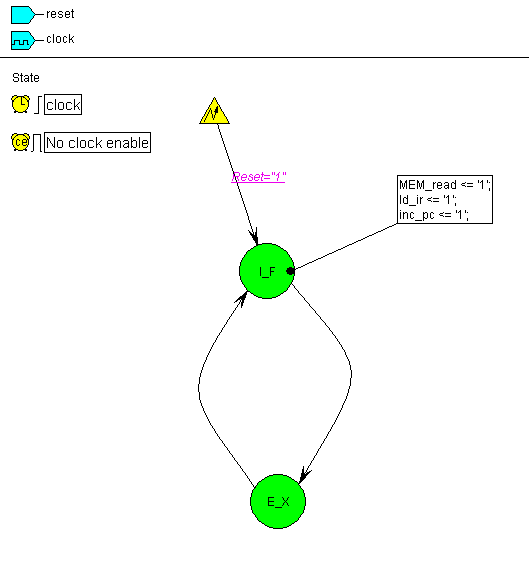

Використовуючи палітру інструментів FSM Toolbar або меню FSM, додати до діаграми станів дії в стані I_F (State Actions

):

):

MEM_read <= '1';

ld_ir <= '1';

inc_pc <= '1';

як показано на рис. 5.

Рис. 6. Діаграма станів з заданими керуючими сигналами стану I_F.

Меню FSM – Generate Code – Згенерувати HDL код, ознайомитися із ним, провести компіляцію.

Для генерування керуючих сигналів на кроці E_X, залежно від поточної інструкції (Входу IR) можна продовжити роботу в режимі State Edіtor Але для кращого вивчення отриманого коду, зробимо це за допомогою HDL Editor.

Щоб уникнути збоїв компіляції при розбіжності між діаграмою станів та HDL-кодом потрібно перенести згенерований код до нового файлу та продовжити роботу в цьому файлі!

Додати оператор використання Package файлу

Розширити перелік портів пристрою:

IR: IN std_logic_vector(7 DOWNTO 0);

Z: IN std_logic;

C: IN std_logic;

MEM_write: OUT std_logic;

MEM_select: OUT std_logic;

jump_pc: OUT std_logic;

sel_dm: OUT std_logic;

alu_op: OUT std_logic_vector(3 DOWNTO 0);

ld_op: OUT std_logic;

data_out: OUT std_logic;

Rg_op: OUT std_logic;

write_ixh: OUT std_logic;

write_ixl: OUT std_logic;

RgWrite: OUT std_logic

В блоці architecture, поза процесами, згенерувати вихідний сигнал активування зовнішнього блоку пам’яті, незалежно від стану автомату (в даній реалізації пам'ять завжди активована):

MEM_select <= '1';

На початку процесу, що реалізує функцію виходів (State_NextState: process), деактивувати усі керуючі сигнали:

sel_dm <= '0';

MEM_read <= '0';

MEM_Write <= '0';

ld_ir <= '0';

inc_pc <= '0';

jump_pc <= '0';

alu_op <= NOP_OP;

ld_op <= '0';

data_out <= '0';

Rg_op <= '0';

RgWrite <= '0';

write_ixh <= '0';

write_ixl <= '0';

Для Стану E_X Використати конструкцію IF..ELSIF для аналізу регістру інструкції та генерування вихідних сигналів залежно від поточного його вмісту, наприклад:

IF(IR=CLEAR_C) THEN alu_op <= CLR_C_OP;

ELSIF(IR=SET_C)THEN alu_op <= SET_C_OP;

ELSIF -- продовжити за аналогією згідно пункту 5

END IF;

Працюючи по двоє, розробити код, що активує керуючі сигнали етапу EX для виконання двох інструкцій процесора, згідно таблиць 2-6. З наступного списку вибрати інструкції відповідно порядкових номерів студентів в групі (від 1 до 14, далі - циклічно).

SKIP_C

SKIP_Z

JMP_IX

LDA_IMM

ADDA_IMM

STA_RG

LDA_RG

ADDA_RG

XORA_RG

TESTA_RG

STORE

LOAD

SET_IXH

SET_IXL

Відкомпілювати код та провести моделювання роботи керуючого пристрою при виконанні заданих інструкцій з використанням часових діаграм.

Скласти звіт з виконання лабораторної роботи обсягом 2-3 сторінки друкованого тексту та захистити його. Зміст повинен містити кінцевий HDL код проектованого пристрою. Рекомендується додати часову діаграму.

Література:

Сергиенко А. М. VHDL для проектирования вычислительных устройств. ТИД "ДС". 2003. C. 208

Список рекомендованої літератури

Сергиенко А. М. VHDL для проектирования вычислительных устройств. ТИД "ДС". 2003. C. 208