- •1.1 Пояснити що таке мікроархітектурний рівень комп’ютера

- •1.2 Дати опис послідовності мікрооперацій в іjvm Міс-1 в одному циклі синхронізації?

- •1.3 Дати опис взаємодії іjvm Міс-1 з основною пам’яттю.

- •1.5 Скільки команд має іjvm Міс-1. Перерахуйте основні групи команд і дайте пояснення їх призначення.

- •1.6 Поясніть роботу стека операндів на прикладі

- •1.7 Опишіть інтерпретацію в Міс-1 команди умовного переходу ifeq

- •1.8 Поясніть призначення мікрокоманди Маіn1

- •1.9 Як побудована кеш-пам’ять прямого відображення? Поясніть, що таке тег. Що таке «промах кеш-пам’яті»

- •1.10 Опишіть типи даних і формати команд віртуальної машини Java

- •1. Намалювати тракт даних мікроархітектури віртуальної машини іjvm. Пояснити призначення і його функціонування.

- •2. Намалювати схему мікроархітектури Міс-1 і коротко пояснити управління її мікрокомандами.

- •3. Пояснити що таке старший біт і призначення бітів n і z.

- •4. Яке призначення регістра sp і які значення він набуває?

- •5. Приведіть простий приклад компіляції з мови Java на мову ассемблера Java

- •6. Опишіть інтерпретацію в Міс-1 команди bipush

- •7. Опишіть інтерпретацію в Міс-1 команди if_icmeq

- •8. Які типи організації (моделі) кеш-пам’яті вам відомі. Які типи взаємодії процесор пам’ять вам відомі?

- •9. Поясніть як здійснюється прогнозування переходів (галужень)

- •10. Опишіть типи команд віртуальної машини Java

- •Пояснити синхронізацію тракту даних із використанням часової діаграми віртуальної машини Java

- •Пояснити що таке мікрокоманда іjvm. Дати опис формату мікрокоманд віртуальної машини Java.

- •Пояснити, що таке стек і його призначення. Привести приклад графічного зображення стеку і пояснити його роботу.

- •Описати принцип організації пам’яті іjvm. Пояснити призначення і адресацію різних областей пам’яті: констант, фреймів локальних змінних і області процедур

- •Поясніть в загальних рисах, як здійснюються інтерпретація команд іjvm Міс-1.

- •Опишіть інтерпретацію в Міс-1 команди iload.

- •Опишіть інтерпретацію в Міс-1 команди istore

- •Що таке просторова і часова локалізація адрес в кеш-пам’яті

- •Опишіть, як здійснюється програмне введення-виведення.

1.8 Поясніть призначення мікрокоманди Маіn1

Main1 PC=PC+1; fetch; goto(MBR) MBR містить код операції, отримання наступного байту.

Main1 – це мітка початку основного циклу.

Main1 – це ствердження, що в PC завантажено адресу комірки пам’яті, в якій міститься код операції. Більше того, це код операції викликаний в регістр MBR

1.9 Як побудована кеш-пам’ять прямого відображення? Поясніть, що таке тег. Що таке «промах кеш-пам’яті»

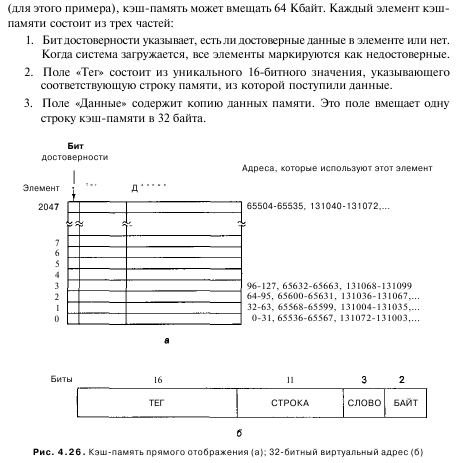

Найпростіший тип кеш-пам'яті - це кеш-пам'ять прямого відображення. Призаходів однорівневої кеш-пам'яті прямого відображення зображений на рис. 4.26, а. Данва кеш-пам'ять містить 2048 елементів. Кожен елемент (ряд) може вміщати

рівно

один рядок з основної пам'яті. Якщо

розмір рядка кеш-пам'яті 32 байтаДля

цього прикладу), кеш-пам'ять може вміщати

64 Кбайт. Кожен елемент кеш-пам'яті

складається з трьох частин:

рівно

один рядок з основної пам'яті. Якщо

розмір рядка кеш-пам'яті 32 байтаДля

цього прикладу), кеш-пам'ять може вміщати

64 Кбайт. Кожен елемент кеш-пам'яті

складається з трьох частин:

1. Біт достовірності вказує, чи є достовірні дані в елементі чи ні.

Коли система завантажується, всі елементи маркуються як недостовірні.

2. Поле «Тег» складається з унікального 16-бітового значення, яке зазначає

відповідний рядок пам'яті, з якої надійшли дані.

3. Поле «Дані» містить копію даних пам'яті. Це поле вміщає одну

рядок кеш-пам'яті в 32 байти.

оли центральний процесор видає адресу пам'яті, апаратне забезпечення

виділяє з цієї адреси 11 бітів поля «РЯДОК» і використовує їх для пошуку

в кеш-пам'яті одного з 2048 елементів

У разі вдалого обра-

дення слово береться прямо з кеш-пам'яті, і тоді не потрібно звертатися до основ-

ної пам'яті. З елемента кеш-пам'яті береться тільки потрібне слово. Інша частина елемента не використовується. Якщо елемент кеш-пам'яті недійсний (недостоверен) або поля «Тег» не збігаються, то потрібного слова немає в пам'яті. Така ситуація називається промахом кеш-пам'яті. У цьому випадку 32-бай

1.10 Опишіть типи даних і формати команд віртуальної машини Java

Java - це мова з суворим контролем типів. Це означає, що кожен операнд має особливий тип і розмір, який відомий у період компіляції. Це відбиток у ви- але в типах, підтримуваних JVM. JVM підтримує числові типи, приведенние в табл. 5Л. Цілі числа зі знаком використовують додатковий код.Формати команд 353 Цілі числа без знака в мові Java не присутні і не підтримуються JVM, як і двійково-десяткові числа.

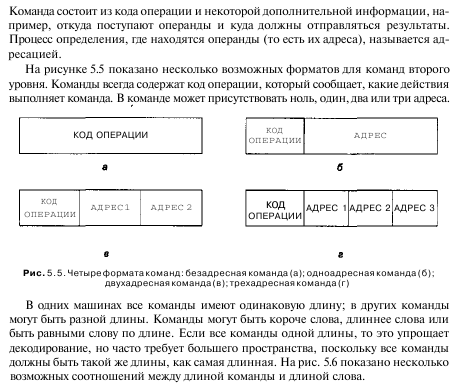

Команда складається з коду операції і деякої додаткової інформації, на- приклад, звідки надходять операнди і куди рушать результати. Процес визначення, де знаходяться операнди (тобто їх адреси), називається ад- ресаціей. На малюнку 5.5 показано кілька можливих форматів для команд другого рівня. Команди завжди містять код операції, який повідомляє, які дії виконує команда. У команді може бути присутнім нуль, один, два або три адреси.

Варіант 2

1 |

Пояснити призначення і використання віртуальної машини JVM. Пояснити відмінність ІJVM і JVM. |

Рівень команд машини JVM незвичайний, але досить простий. Ми вже частково розглянули його під час вивчення машини JVM. Модель пам'яті JVM точно така ж, як у IJVM, про яку ми говорили в розділі 4 (див. рис. 4.9), але з однією додатковою областю, про яку ми зараз розповімо. Порядок байтів зворотний. Пам'ять містить 4 основні області: фрейм локальних змінних, стек операндів, область процедур і набір констант. Нагадаємо, що в реалізаціях Mic-x машини IJVM на ці області вказують регістри LV, SP, PC і СРР. Доступи до пам'яті повинні здійснюватися тільки по зсуві від одного з цих регістрів; покажчики і абсолютні адреси пам'яті не використовуються. Хоча JVM не вимагає наявності цих регістрів, в більшості реалізацій такі регістри (або подібні до них) є. Відсутність вказівників для доступу до локальних змінних і констант не випадково. Це потрібно для досягнення однієї з головних цілей мови Java: можливості завантажувати двійкову програму з Інтернету і виконувати її, не побоюючись шпигунських програм або будь-якого збою в машині, на якій це програма виконується. Якщо обмежити використання покажчиків, можна домогтися високої безпеки.

2 |

Пояснити призначення і роботу регістрів пам’яті віртуальної машини ІJVM. |

регістр СРР- має у собі адрес першого слова набору констант

регістр LV - регістр, який має у собі адрес першої змінної фрейма

регістр SP - регістр, що має у собі адрес команди, яка повинна викликатися наступною

(неповне)

4. |

Що таке фрейм локальних змінних? Яке його призначення, де він розміщений і як організований? Що таке стек операндів? Яке його призначення де він розміщений і як організований? |

4. Фрейм локальних зміних. Це область призначена для збереження змінних під час виконання процедури. Вона називається фреймом локальних змінних. В початку цього фрейму знаходиться параметри (або аргументи) викликаної процедури. Фрейм локальних змінних не включає у себе стек операндів. Він поміщається окремо. Виходячи з обмірковувань працездатності, ми помістили стек операндів прямо над фреймом локальних змінних. Існує неявний регістр, який має у собі адрес першої змінної фрейму. Ми називемо цей регістр LV (local variable – локальна змінна). Параметри викликаної процедури зберігаються в початку фрейму локальних змінних.

Стек операндів. Стек опера днів не повинен перевищувати певний розмір, який зарання вираховується компілятором Java. Простір стеку операндів розміщується прямо над фреймом локальних змінних

6. |

Опишіть інтерпретацію в Міс-1 команд арифметичних та логічних операцій ІJVM IADD, IAND. |

6. IAND – логічне і

IADD – сумма 2 значень

7. |

Опишіть інтерпретацію в Міс-1 команди GOTO |

7. команда безумовного переходу

8. |

Поясніть, як організована кеш-пам’ять в Міс-1 і чому. |

8. кеш-пам’ять вміщає найбільш часто

використовувані слова, що збільшує швидкість доступа до них. Якщо достатньо великий відсоток потрібних слів знаходится в кеш-пам’яті, час очікувания може сильно скоротитися.

Одна з найбільш еффективних технологій одночасного збільшення пропускної здатності та зменшення часу очікування є використання декількох блоків кеш-пам’яті. Основна технологія введения окремої кеш пам’яті для команд та окремої для данних (розділеної кеш-памяті). Така

кеш-пам’ять має декілька переваг.По перше, операціі можуть починатися незалежно в кожній кеш-пам’яті, що подвоює пропускную здатність системи пам’яті. Саме по цій причині у мікроархітектурі Mic-1 нам знадобились два окремих порта пам’яті: особливий порт для кажної кеш-пам’яті. Відмітимо, що кожна кеш-пам’ять має незалежний доступ до основної пам’яті.

9. |

Поясніть як побудована асоціативна кеш-пам’ять? |

9. У цій схемі усунений недолік кеш-пам'яті з прямим відображенням, оскільки будь-який блок ОЗП може відображуватися в будь-якому рядку кеш-пам'яті. У кеш-пам'ять ознак записується 30-розрядна ознака, тобто старші 30 розрядів А31—А2 адреси 4-байтного блоку ОЗП. У рядок кеш-пам'яті даних записується 4-байтный блок. Якщо кеш-пам'ять не заповнена, блок записується в будь-який вільний рядок. Якщо кеш-пам'ять заповнена, блок з ОЗП записується в той рядок кеш-пам'яті даних, до якої була найменша кількість звернень. Недоліки кеш-пам'яті з прямим відображенням усуваються за рахунок додаткових засобів визначення блоку, до якого була найменша кількість звернень. При цьому також збільшується час обробки запитів із-за необхідності порівняння 30-розрядної адреси і ознаки, записаної в кеш-пам'яті ознак. Максимальна кількість таких порівнянь складає 16К.

10. |

Опишіть способи адресації віртуальної машини Java |

10. В машини JVM немає спільних способів адресаціі у тому сенсі, що кожна команда утримує в собі кілька бітів, які повідомляють, як потрібно вирахувати адресу (як в Pentium 2, на приклад). Замість цього тут з кожною командою пов’язан один особливий спосіб адресаціі. Оскільки в JVM немає видимих регістрів, регістрова і непрямий регістрова адресація тут неможлива. Декілька команд, наприклад BIPUSH, використовують безпосередню адресацію. Єдиний залишившийся доступний спосіб – індексна адресалі. Вона використовується командами LOAD, ISTORE, LDOW, а також деякими командами, які визначають змінну, пов’язану з яким-небудь неявним регістром, зазвичай LV або CPP. Команди переходу також використовують індексну адресацію, але при цьому РС розглядається як регістр.

Варіант 3