- •История развития вычислительной техники.

- •3. Схемы с мягкой и жесткой логикой.

- •Децентрализованный арбитраж.

- •9. Полупроводниковая rom память.

- •10. Оперативная асинхронная память.

- •В11. Оперативная синхронная память.

- •Характеристики sdram

- •16. Способы адресации. Трансляция адресов lba и chs.

- •17. Организация raid – массивов.

- •В18 Логическая структура накопителей на жестких дисках. Mbr.

- •В19 Логическая структура накопителей на жестких дисках. Gpt

Характеристики sdram

Память принято характеризовать различными параметрами, важнейшим из которых является пропускная способность, определяющая максимальное количество байт, передаваемых по шине данных за одну секунду. Для того чтобы определить пропускную способность памяти, нужно частоту системной шины умножить на количество байт, передаваемых за один такт. Память SDRAM имеет 64-битную (8-байтную) шину данных, поэтому пропускная способность SDRAM-памяти определяется по формуле:

Пропускная способность (Мбайт/с) = частота системной шины (МГц) х 8 байт.

RAS to CAS Delay - это промежуток времени, измеряемый в тактах системной шины, между сигналами RAS и СAS, то есть задержка подачи сигнала СAS относительно сигнала RAS.

CAS Latency определяет задержку по времени в тактах, которая происходит с момента подачи сигнала CAS до выдачи первого элемента данных на шину. Каждый последующий элемент данных появляется на шине данных в очередном такте. Для SDRAM-памяти эта задержка может составлять два или три такта.

Завершение цикла обращения к банку памяти осуществляется подачей команды деактивации. Эта команда подается за один или за два такта перед выдачей последнего элемента данных. Время деактивации RAS Precharge также измеряется в тактах и может быть равно двум или трем.

В12. КЭШ-память. Функции кэш-контроллера

КЭШ — промежуточный буфер с быстрым доступом, содержащий информацию, которая может быть запрошена с наибольшей вероятностью. Доступ к данным в кэше идёт быстрее, чем выборка исходных данных из оперативной (ОЗУ) и быстрее внешней (жёсткий диск или твердотельный накопитель) памяти, за счёт чего уменьшается среднее время доступа и увеличивается общая производительность компьютерной системы.

Задача КЭШа- 1) Обеспечение быстрого доступа к данным, 2)Согласование интерфейсов процессора и контроллера памяти , 3) Упреждающая загрузка и отложенная запись данных

В общем виде использование кэш-памяти поясним следующим образом. Когда ЦП пытается прочитать слово из основной памяти, сначала осуществляется поиск копии' этого слова в кэше. Если такая копия существует, обращение к ОП не производится, а в ЦП передается слово, извлеченное из кэш-памяти. Данную ситуацию принято называть успешным обращением или попаданием (hit). При отсутствии слова в кэше, то есть при неуспешном обращении — промахе (miss),— требуемое слово передается в ЦП из основной памяти, но одновременно из ОП в кэш-память пересылается, блок данных, содержащий это слово.

На эффективность применения кэш-памяти в иерархической системе памяти влияет целый ряд моментов. К наиболее существенным из них можно отнести:

*емкость кэш-памяти;

*размер строки;

*способ отображения основной памяти на кэш-память;

*алгоритм замещения информации в заполненной кэш-памяти;

*алгоритм согласования содержимого основной и кэш-памяти;

*число уровней кэш-памяти.

Контроллер кэш Контроллер кэш памяти оперирует со строками данных (cache line) фиксированной длины (или блоками данных). С каждой строкой кэш (блоком) связана информация об адресе скопированного в нее блока основной памяти и признаки ее состояния. Строка может быть действительной (valid) - это означает, что в текущий момент времени она достоверно отражает соответствующий блок основной памяти, или недействительной (пустой). Строки кэш памяти обычно выделяются только при операциях чтения. Запись блока, не имеющего копии в кэш памяти, производится только в основную память. Поведение кэш-контроллера при операции записи в память, когда копия затребованной области находится в некоторой строке кэш памяти, определяется его политикой записи (Write Policy).

Кэш-контроллер перехватывает запрос и отслеживает, есть ли нужные данные в КЭШе, если нет, то получается промах и запрос передается в ОЗУ. Поскольку КЭШ контроллер не в состоянии знать какие данные потребует процессор, сущ. определенная стратегия кэширования по которым определяется нужно ли помещать данные в КЭШ или нет. Все современные процессоры помещают в КЭШ данные к которым хотя бы раз было обращение. Но в КЭШ нельзя поместить все ячейки памяти и КЭШ нужно очищать. Сущ. несколько подходов к замещению данных:

-LRU (Данные к которым долго не обращались)

-FIFO (Первый зашел, первый вышел)

-Случайное замещение

В13.Поиск информации в КЭШе. КЭШ прямого отображения. Ассоциативный КЭШ.

Кэш прямого отображения.

Кэш прямого отображения (direct mapped) наиболее дешевый и простой по организации. Область оперативной памяти разбивается на блоки. На такие же блоки разбивается кэш память. Количество блоков в кэш значительно меньше, чем количество блоков в ОЗУ. Каждый блок основной памяти имеет только одно фиксированное место, на котором он может появиться в кэш-памяти. При записи данных в кэш каждый блок оперативной памяти может претендовать только на определенный блок кэш памяти. Например, на месте первого блока кэш памяти, состоящей из четырех блоков прямого отображения (рис. 1.), может размещаться первый блок ОЗУ, пятый, девятый и т.д. На место второго блока в кэш претендуют блоки 2-ой, 6-ой, 10-ый и т.д. Как видим, на одну и ту же область кэш претендует несколько блоков ОЗУ, что может привести к конфликтам.

Кроме того, даже если конфликты разрешаются схемой управления, то при последовательном обращении к блокам, претендующим на одно и то же место в кэш, происходит постоянная замена блоков и кэш память теряет смысл, т.к. не увеличивает скорость обмена данными между процессором и оперативной памятью.

Ассоциативный кэш Полностью ассоциативный кэш реализуется аппаратно. Поиск информации как и в ассоциативной памяти производится по ключевому слову. Особенность такой организации кэш в том что любой блок оперативной памяти может занимать любое место в кэш памяти. Такой способ адресации не требует внешнего описания памяти. Информация о том, какой именно блок занимает данную строку, и каково состояние строки (действительная или пустая) называется тегом (tag) и хранится в связанной с данной строкой ячейке специальной памяти тегов (tag RAM). Поиск данных производится параллельно во всех блоках кэш. При операции записи или считывания контроллер кэш проверяет нет ли записи в кэш и фиксирует частоту обращения к каждому блоку кэш. Такая реализация требует больших аппаратных затрат. Для персональных компьютеров этот способ реализации кэш слишком дорог.

В14.Контроль и коррекция ошибок. Алгоритм Хемминга

Проверка чётности

Контроль четности или коррекция ошибок (ECC (код исправления ошибок)) используется в основном только в жизненно важных компьютерных системах, где недопустима даже одна ошибка в несколько десятилетий. Проверка четности – довольно простой метод обнаружения ошибок памяти, без возможности восстановления. Каждый байт данных связан с одним битом четности или так называемым паритетным битом. Этот бит устанавливается во время записи, и затем рассчитывается и сравнивается во время чтения. Изменение состояния этого бита говорит о возникшей ошибке. Этот метод ограничен определением изменения состояния одиночного бита в байте. В случае изменения состояния двух битов, возможна ситуация, когда вычисление паритетного бита совпадет с записанным. В этом случае система не определит ошибку, и произойдет экстренная остановка системы. Так как приблизительно 90% всех нерегулярных ошибок происходит именно с одиночным разрядом, проверки четности бывает достаточно для большинства ситуаций. К сожалению необходимость в дополнительных вычислениях паритетного бита требует некоторых затрат процессорного времени, что несколько снижает производительность всей системы.

Код Хемминга – это блочный код, позволяющий исправлять одиночные и фиксировать двойные ошибки, разработанный Ричардом Хеммингом в сороковых годах прошлого столетия.

Идея кодов Хемминга заключается в разбиении данных на блоки фиксированной длины и вводе в эти блоки контрольных бит, дополняющих до четности несколько пересекающихся групп, охватывающих все биты блока.

Алгоритм кодирования Хэмминга - очень популярен и позволяет значительно повысить надежность передачи и хранения информации. Особенно, он выгоден при кодировании больших блоков данных. Существует большое количество различных способов реализации этого алгоритма.

В 15 Накопители на жестких магнитных дисках. Принципы записи.

Накопи́тель на жёстких магни́тных ди́сках или НЖМД (англ. hard (magnetic) disk drive, HDD, HMDD) — запоминающее устройство (устройство хранения информации) произвольного доступа, основанное на принципе магнитной записи. Является основным накопителем данных в большинстве компьютеров.

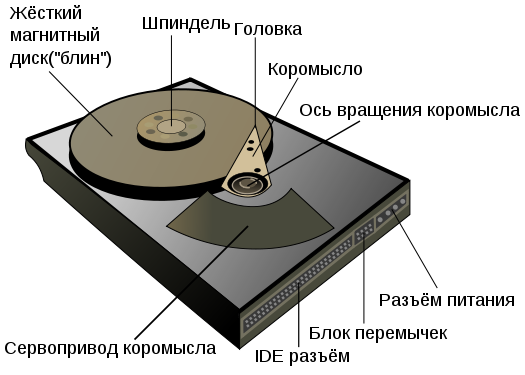

Типовой винчестер состоит из гермоблока и платы электроники. В гермоблоке размещены все механические части: шпиндель с одним или несколькими дисками; двигатель; блок магнитных головок (БМГ) с коммутатором и позиционером; предусилитель сигнала, от которого к позиционеру идет ленточный кабель или набор обычных одножильных проводов (которые, бывает, рвутся). На плате - вся управляющая электроника.

Информация на винчестере, хранится на магнитных дисках (пластинах). Диск -представляет собой пластину с напылением высококачественного ферромагнетика. В качестве материала для самой пластины применяют алюминий, керамику или стекло, а в качестве магнитного слоя наносят окись хрома или тонкопленочное металлическое покрытие. Внутри жесткого диска может быть установлено несколько пластин, посаженных на вал шпиндельного двигателя.

Принцип работы жёстких дисков. Рабочая поверхность диска движется относительно считывающей головки (например, в виде катушки индуктивности с зазором в магнитопроводе). При подаче переменного электрического тока (при записи) на катушку головки возникающее переменное магнитное поле из зазора головки воздействует на ферромагнетик поверхности диска и изменяет направление вектора намагниченности доменов в зависимости от величины сигнала. При считывании перемещение доменов у зазора головки приводит к изменению магнитного потока в магнитопроводе головки, что приводит к возникновению переменного электрического сигнала в катушке из-за эффекта электромагнитной индукции.