- •История развития вычислительной техники.

- •3. Схемы с мягкой и жесткой логикой.

- •Децентрализованный арбитраж.

- •9. Полупроводниковая rom память.

- •10. Оперативная асинхронная память.

- •В11. Оперативная синхронная память.

- •Характеристики sdram

- •16. Способы адресации. Трансляция адресов lba и chs.

- •17. Организация raid – массивов.

- •В18 Логическая структура накопителей на жестких дисках. Mbr.

- •В19 Логическая структура накопителей на жестких дисках. Gpt

История развития вычислительной техники.

Вычислительная техника является важнейшим компонентом процесса вычислений и обработки данных. Первыми приспособлениями для вычислений были, вероятно, всем известные счётные палочки, которые и сегодня используются в начальных классах многих школ для обучения счёту.

Можно рассмотреть следующие этапы:

- ручной этап

(счетные палочки, счеты, логарифмическая линейка)

- механический этап

механический арифмометр,; 1832 г. Английский математик Чарльз Бэббидж (Charles Babbage, 1792-1871) создает сегмент разностной машины, оперирующий шестиразрядными числами и разностями второго порядка. Разностная машина Бэббиджа по идее аналогична калькулятору Мюллера.

Аналитическая машина Бэббиджа состояла из 4 –х частей:

Блок хранения исходных данных, промежуточных данных и резервов.

Блок обработки чисел

Блок управления последовательностью вычислений

Блок ввода исходных данных и печати результата.

- электроно – механический

Совмещение электронных и механических приборов. (электромеханических реле)

- электронный

Использование схем на базе электронно – вакуумных ламп, затем и использование полупроводников.

Особенности архитектуры фон Неймана. Принципы фон Неймана.

«принципы фон Неймана».

Принцип однородности памяти

Программы и данные хранятся в одной и той же памяти. Поэтому ЭВМ не различает, что хранится в данной ячейке памяти — число, текст или команда. Над командами можно выполнять такие же действия, как и над данными.

Принцип адресуемости памяти

Основная память структурно состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка. Отсюда следует возможность давать имена областям памяти, так, чтобы к хранящимся в них значениям можно было бы впоследствии обращаться или менять их в процессе выполнения программы с использованием присвоенных имен.

Принцип последовательного программного управления

Предполагает, что программа состоит из набора команд, которые выполняются процессором автоматически друг за другом в определенной последовательности.

Принцип жесткости архитектуры

Неизменяемость в процессе работы топологии, архитектуры, списка команд.

Принцип двоичного кодирования

3. Схемы с мягкой и жесткой логикой.

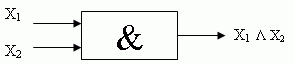

Жесткая логика – это когда для выполнения каждой команды используется своя логическая схема. (пр. Логические схемы конъюнкции, дизъюнкции, отрицания и т. д.)

![]()

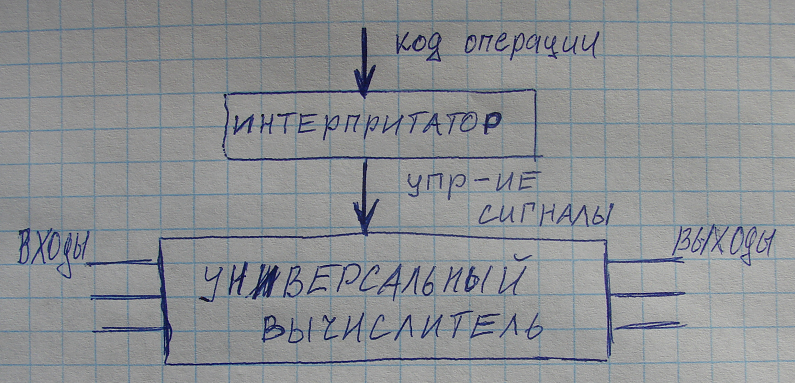

В более сложных ЭВМ применяются схемы с «мягкой логикой» - используется универсальный вычислитель.

Интерпретатор команд – определяет что необходимо сделать.

Универсальный вычислитель(процессор) – должен обмениваться данными с устройствами ввода/вывода и ОЗУ. Для этого он использует свои внутренние устройства памяти.

В процессоре должны иметься два регистра: MAR(memory адрес регистр) и MBR( memory буфер регистр).

4. Основной цикл выполнения команд. Цикл с прерыванием.

Универсальный вычислитель(процессор) – должен обмениваться данными с устройствами ввода/вывода и ОЗУ. Для этого он использует свои внутренние устройства памяти.

В процессоре должны иметься два регистра:

MAR(memory

адрес регистр) и MBR(

memory

буфер регистр).

процессоре должны иметься два регистра:

MAR(memory

адрес регистр) и MBR(

memory

буфер регистр).

MAR – в этом регистре хранится адрес ячейки по которому необходимо обратиться.

MBR – хранит сами данные.

PC – регистр, который содержит адрес следующей выполняемой операции.

IR – регистр, в котором храниться извлеченная из памяти команда.

Извлечение и выполнение команд:

Процессор обращается в ОЗУ, согласно счетчику PC; эта команда копируется в регистр IR; после этого содержимое счетчика PC увеличивается на длинну считанной команды.

Декодирование команд:

Определить код операции (что делать?)

Определяется количество операндов и их адреса в памяти (заполнение MAR)

Заполнение MBR

Исполнение команды.

Проверить результаты выполнения операции.

запись результатов.

Любая команда при обработке проходит несколько этапов. Весь процесс называется – командным процессором.

---------------------------------------------------------------------------------------------------------------------

Во всех современных ЭВМ предусмотрены прерывания. Прерывания существуют:

Программное прерывание. ( могут возникать при выполнении программ, при возникновении внештатных прерываний) .

Аварийные прерывания (перегрев, отключение питания и т. д.)

Прерывание таймера. (Генерируется ОС для ее нужд. Пр. многозадачность)

Прерывания ввода/вывода (системные ресурсы ЭВМ – номера запросов на прерывания, адреса ввода/вывода)

Для того что бы можно было обрабатывать прерывания в основной цикл добавляется дополнительная фаза – фаза прерывания ( процессор проверяет поступили ли прерывания или нет).

Если прерываний не поступало, то процессор завершает текущий цикл и начинает следующий. Если процессор обнаружил прерывание, то запускается процедура обработки прерывания.

5. Виды прерываний. Обработка прерываний.

Во всех современных ЭВМ предусмотрены прерывания. Прерывания существуют:

Программное прерывание. ( могут возникать при выполнении программ, при возникновении внештатных прерываний) .

Аварийные прерывания (перегрев, отключение питания и т. д.)

Прерывание таймера. (Генерируется ОС для ее нужд. Пр. многозадачность)

Прерывания ввода/вывода (системные ресурсы ЭВМ – номера запросов на прерывания, адресса ввода/вывода)

Процесс обработки прерываний:

1.При возникновении прерывания происходит первичное аппаратное распознавание типа прерывания. Если прерывания данного типа в этот момент запрещены, то процессор продолжает поддерживать естественный ход выполнения команд. В противном случае в зависимости от поступившей в процессор информации (уровень прерывания, вектор прерывания или тип условия внутреннего прерывания) происходит автоматический вызов процедуры обработки прерывания, адрес которой находится в специальной таблице операционной системы.

2. Автоматически сохраняется некоторая часть контекста прерванного потока (значение счетчика команд, слова состояния машины, некоторых регистров общего назначения и др.), которая позволит ядру возобновить исполнение потока после обработки прерывания.

3. Одновременно с загрузкой адреса процедуры обработки прерываний в счетчик команд может автоматически выполняться загрузка нового значения слова состояния машины, которое определяет режим работы процессора при обработке прерывания, в том числе работу в привилегированном режиме.

4. Временно запрещаются прерывания данного типа, чтобы не образовалась очередь вложенных друг в друга потоков одной и той же процедуры. Это может производиться с использованием механизма маскирования прерываний.

5. После обработки прерывания ядром операционной системы прерванный контекст восстанавливается, и работа потока возобновляется.

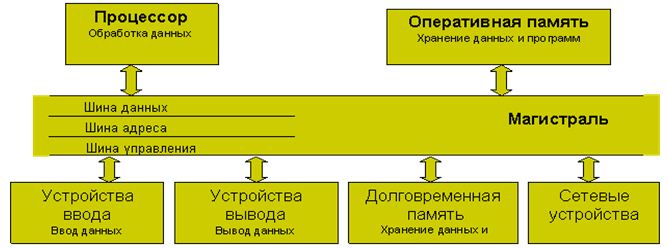

6. Системная магистраль. Структура магистрали. Синхронизация магистрали.

Системная магистраль – служит для физического и логического объединения всех устройств ЭВМ. Системная, шина в состоянии содержать несколько сотен линий.

Совокупность линий шины можно подразделить на три функциональные группы: шину данных, шину адреса и шину управления. К последней обычно относят также линии для подачи питающего напряжения на подключаемые к системной шине модули.

Функционирование системной шины можно описать следующим образом. Если один из модулей хочет передать данные в другой, он должен выполнить два действия: получить в свое распоряжение шину и передать по ней данные. Если какой-то модуль хочет получить данные от другого модуля, он должен получить доступ к шине и с помощью соответствующих линий управления и адреса передать в другой модуль запрос. Далее он должен ожидать, пока модуль, получивший запрос, пошлет данные.

Физически системная шина представляет собой совокупность параллельных электрических проводников. Этими проводниками служат металлические полоски на печатной плате.

------------------------------------------------------------------------------

В синхронных шинах имеется центральный генератор тактовых импульсов (ГТИ), к импульсам которого «привязаны» все события на шине. Тактовые импульсы (ТИ) распространяются по специальной сигнальной линии и представляют собой регулярную последовательность чередующихся единиц и нулей. Один период такой последовательности называется тактовым периодом шины.

7. Арбитраж магистрали.

В реальных системах на роль ведущего вправе одновременно претендовать сразу несколько из подключенных к шине устройств, однако управлять шиной в каждый момент времени может только одно из них. Чтобы исключить конфликты, шина должна предусматривать определенные механизмы арбитража запросов и правила предоставления шины одному из запросивших устройств. Решение обычно принимается на основе приоритетов претендентов.

Два подхода: 1. Централизованный арбитраж 2. Децентрализованный арбитраж.

Централизованный арбитраж

При централизованном арбитраже в системе имеется специальное устройство — центральный арбитр, - ответственное за предоставление доступа к шине только одному из запросивших ведущих. Это устройство, называемое иногда центральным контроллером шины, может быть самостоятельным модулем или частью ЦП.

Наличие на шине только одного арбитра означает, что в централизованной схеме имеется единственная точка отказа. В зависимости от того, каким образом ведущие устройства подключены к центральному арбитрут возможные схемы централизованного арбитража можно подразделить на параллельные и последовательные.