- •Ответы на вопросы к экзамену по схемотехнике.

- •Понятие о логическом элементе. Простые и сложные лэ. Функции, реализуемые лэ.

- •Системы лэ. Понятия функциональной и технической полноты системы лэ.

- •Представление информации в лэ.

- •Параметры лэ.

- •Входная характеристика лэ.

- •Выходная характеристика лэ.

- •Определение нагрузочных способностей элементов по входным и выходным характеристикам.

- •Характеристика передачи лэ. Вид характеристики и требования к ней.

- •Параметры лэ, определяемые с помощью характеристики передачи.

- •Помехоустойчивость лэ. Как определить помехоустойчивость лэ.

- •Диодные лэ. Функции, реализуемые диодными лэ.

- •Дтл элемент с простым инвертором.

- •Дтл элемент со сложным инвертором.

- •Нагрузочная способность дтл элементов со сложным и простым инвертором.

- •Логические элементы ттл. Основное отличие от дтл. Функции, реализуемые на элементах ттл.

- •Лэ ттл с простым инвертором.

- •22. Ттл схема и принцип работы со сложным инвертором

- •Характеристика передачи лэ ттл.

- •Определение основных параметров лэ ттл с помощью характеристики передачи.

- •Буферные элементы, элементы с тремя состояниями на выходе.

- •Основные серии элементов ттл (по справочнику).

- •Лэ ттлш. Основное отличие от ттл.

- •Логические элементы и2л.

- •Реализация логических функций на лэ и2л.

- •Лэ на полевых транзисторах.

- •Лэ на кмоп и кмдп.

- •38. Реализация и-не или-не на кмоп элементах.

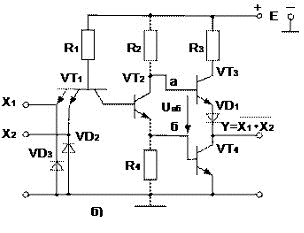

Нагрузочная способность дтл элементов со сложным и простым инвертором.

Логические элементы ттл. Основное отличие от дтл. Функции, реализуемые на элементах ттл.

Транзисторно-транзисторная логика (ТТЛ, TTL) — разновидность цифровых логических микросхем, построенных на основе биполярных транзисторов и резисторов. Название транзисторно-транзисторный возникло из-за того, что транзисторы используются как для выполнения логических функций (например, И, ИЛИ), так и для усиления выходного сигнала (в отличие от резисторно-транзисторной и диодно-транзисторной логики).

Простейший базовый элемент ТТЛ выполняет логическую операцию И-НЕ, в принципе повторяет структуру ДТЛ микросхем и в то же время за счёт использования многоэмиттерного транзистора, объединяет свойства диода и транзисторного усилителя что позволяет увеличить быстродействие, снизить потребляемую мощность и усовершенствовать технологию изготовления микросхемы.

Лэ ттл с простым инвертором.

Принцип работы ТТЛ с простым инвертором: биполярные транзисторы могут работать в режимах: отсечки, нормально активный, инверсно активный и насыщения. В инверсно активном режиме эмиттерный переход закрыт, а коллекторный переход открыт. В инверсном режиме коэффициент усиления транзистора значительно меньше, чем в нормальном режиме, из-за несимметричного конструктивного исполнения переходов база-коллектор и база-эмиттер. При нулевом уровне на любом входе многоэмиттерного транзистора VT1 (на упрощённой схеме — слева) он работает в нормальном режиме и формирует на базе VT2 потенциал близкий к нулю. В этом состоянии неосновные носители из базы VT2 рассасываются не только через коллектор, но и через открытый VT1.

Если ноль подаётся на один из входов VT1, то наблюдается максимальный входной ток I=(E-0,7)/R1. В этом случае через другие эмиттерные переходы может наблюдаться паразитный ток. Если на все входы поступает уровень логической единицы, то VT1 окажется инверсно-включенным, ток R1 течёт через коллектор VT1 в базу VT2, на выходе формируется нуль.

Если резистор R2 не используется, то мы имеем дело с элементом с открытым коллектором, у которого в условном обозначении используется дополнительный символ.

ТТЛ-логика (как и ТТЛШ) является прямым наследником ДТЛ и использует тот же принцип действия. Входной ТТЛ-транзистор (в отличие от обычного) имеет несколько, обычно от 2 до 8, эмиттеров. Эти эмиттеры выполняют роль входных диодов (если сравнивать с ДТЛ).

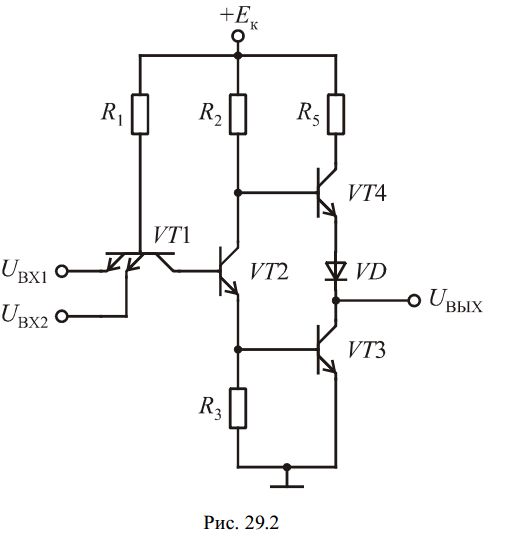

22. Ттл схема и принцип работы со сложным инвертором

Схема ТТЛ со сложным осуществляет логическую операцию И-НЕ. При наличии на входах напряжения лог. «0» многоэмиттерный транзистор VT1 находится в режиме насыщения, а транзистор VT2 закрыт. Следовательно, закрыт и транзистор VT4, поскольку ток через резистор R4 не протекает и напряжение на базе VT4 Uбэ4="0". Транзистор VT3 открыт, так как его база подключена к источнику питания E через резистор R2. Сопротивление резистора R3 невелико, поэтому VT3 работает как эмиттерный повторитель. Через транзистор VT3 и открытый диод VD протекает ток нагрузки логического элемента и выходное напряжение, соответствующее уровню лог. «1», равно напряжению питания за минусом падения напряжения UБЭ.нас, падения напряжения на открытом диоде Uд=UБЭ.нас и небольшого падения напряжения на сопротивлении R2 от тока базы VT2: U¹=E–2UКЭ.нас – R2IБ2 =Un–2UБЭ.нас.

При увеличении напряжения на всех входах потенциал базы VT2 возрастает и при UВХ=U0пор транзистор VT2 открывается, начинает протекать коллекторный ток IK2 через резисторы R2 и R4. В результате базовый ток VT3 уменьшается, падение напряжения на нём увеличивается и выходное напряжение снижается. Пока на резисторе R4 падение напряжения UR4<UБЭ.нас транзистор VT4 закрыт. Когда UВХ=U¹пор=2UБЭ.нас–UКЭ.нас открывается транзистор VT4. Дальнейшее увеличение входного напряжения приводит к насыщению VT2 и VT4 и переходу VT1 в инверсный режим. При этом потенциал точки «а» равен Ua=UБЭ.нас+UКЭ.нас, а точки «б» — Uб=UКЭ.нас, следовательно, Uаб=Uа–Uб=UБЭ.нас. Для отпирания транзистора VT3 и диода VD1 требуется Uаб≥2UБЭ.нас. Так как это условие не выполняется, то VT3 и VD1 оказываются закрытыми и напряжение на входе схемы равно UКЭ.нас=U0

Е сли

хотя бы на одном из входов будет

действовать лог.0, соответствующий

эмиттерный переход будет открыт, и через

него будет протекать ток по цепи от

плюса ИП, через R1, база-эмиттер VT1, общий

провод, минус ИП. В цепи коллектора VT1,

а следовательно, и в цепи базы VT2 ток

будет отсутствовать, VT2 будет находиться

в режиме отсечки, ток через транзистор

VT2, а значит, ток базы VT3 будут близки к

нулю. Транзистор VT3 также будет находиться

в режиме отсечки, и на выходе будет

высокий уровень напряжения логической

единицы. При этом напряжение на коллекторе

VT2 и на базе VT4, будет максимальным, и VT4

будет находиться в полностью открытом

состоянии.

сли

хотя бы на одном из входов будет

действовать лог.0, соответствующий

эмиттерный переход будет открыт, и через

него будет протекать ток по цепи от

плюса ИП, через R1, база-эмиттер VT1, общий

провод, минус ИП. В цепи коллектора VT1,

а следовательно, и в цепи базы VT2 ток

будет отсутствовать, VT2 будет находиться

в режиме отсечки, ток через транзистор

VT2, а значит, ток базы VT3 будут близки к

нулю. Транзистор VT3 также будет находиться

в режиме отсечки, и на выходе будет

высокий уровень напряжения логической

единицы. При этом напряжение на коллекторе

VT2 и на базе VT4, будет максимальным, и VT4

будет находиться в полностью открытом

состоянии.

При подаче на оба входа логических единиц оба эмиттерных перехода закрываются, и ток будет протекать по цепи от плюса ИП, через R1, переход база-коллектор VT1 на базу VT2. Транзистор VT2 перейдёт в режим насыщения. Ток через него, а следовательно, и ток базы VT4 будет максимальным, и транзистор VT3 перейдёт в режим насыщения. На выходе будет низкий уровень логического нуля. При этом напряжение на коллекторе VT2 и на базе VT4 будет близко к нулю и VT4 перейдёт в полностью закрытое состояние. Диод VD1 применяется для более надёжного запирания транзистора VT3.