- •16. Способы определения переполнения при арифметических операциях.

- •Переполнение

- •18. Три концепции реализации мпс.

- •19. Микропроцессор 8080а: структурная схема, назначение выводов.

- •20. Диаграмма переходов для машинного цикла мп 8080а. Формирование сис-темных управляющих сигналов.

- •21. Система команд мп 8080а: группы команд и их характеристика:

- •22. Принципы организации мпс: модульность, магистральный способ обмена информацией, микропрограммное управление.

- •23. Системная шина мпс. Сравнительная характеристика мпс с общей шиной и с изолированной шиной.

- •24. Интерфейс микропроцессора с системной шиной.

20. Диаграмма переходов для машинного цикла мп 8080а. Формирование сис-темных управляющих сигналов.

Число базо¬вых команд МП составляет 78, время выполнения команд для тактовой частоты F=2 МГц лежит в диапазоне 2-9 мкс. Команды МП могут быть одно-, двух- и трехбайт¬ными. Первый байт - код операции. Двух- и трехбайтные команды хранятся в сосед¬них ячейках памяти.

МП имеет четыре режима адре¬сации:

1. Прямая адресация. В этом режиме второй и третий байты команды содержат адрес операнда, причем во втором байте находятся младшие разряды адреса, а в треть-ем - старшие.

2. Регистровая адресация – команда определяет регистр или регистровую пару, в которой находится операнд.

3. Косвенная регистровая адресация – команда определяет регистровую пару, в которой содержится адрес операнда в памяти, причем младшие разряды адреса хранят-ся во втором (младшем) регистре пары, а старшие – в первом (старшем) регистре пары.

4. Непосредственная адресация - команда содержится в себе 8- или 16-разрядный операнд.

Первый байт команды, выбранный из программной памяти, передается по внут-ренней шине данных в РК. Выход РК связан с дешифратором команд ДШК, который определяет тип выполняемой операции. Реализация лю¬бой команды складывается из машинных циклов. Для выборки и выполнения команды может потребоваться от одно-го до пяти машинных циклов. Машинные циклы называются М1, М2, М3, М4 и М5. Длительность машинного цикла варьируется от трёх до пяти тактов или состояний. Такты обозначаются как Т1, Т2, Т3, Т4 и Т5. Длительность каждого такта составляет один период тактового генератора. Имеется три других состояния, которые могут длиться от одного до произвольного числа периодов тактового генератора: это состоя-ния ожидания, захвата и ожида¬ния при останове, управляемые внешними сигналами.

Начало каж¬дого машинного цикла определяется синхросигналом SYNC. Мини-мальная длительность одного состояния Т равняется 0,5 мкс для Fmax=2 МГц.

Машинный цикл М1 всегда является циклом выборки кода операции и продолжается четыре или пять периодов тактового генератора. Машинные циклы М2, М3, М4 и М5 обычно продолжаются три такта.

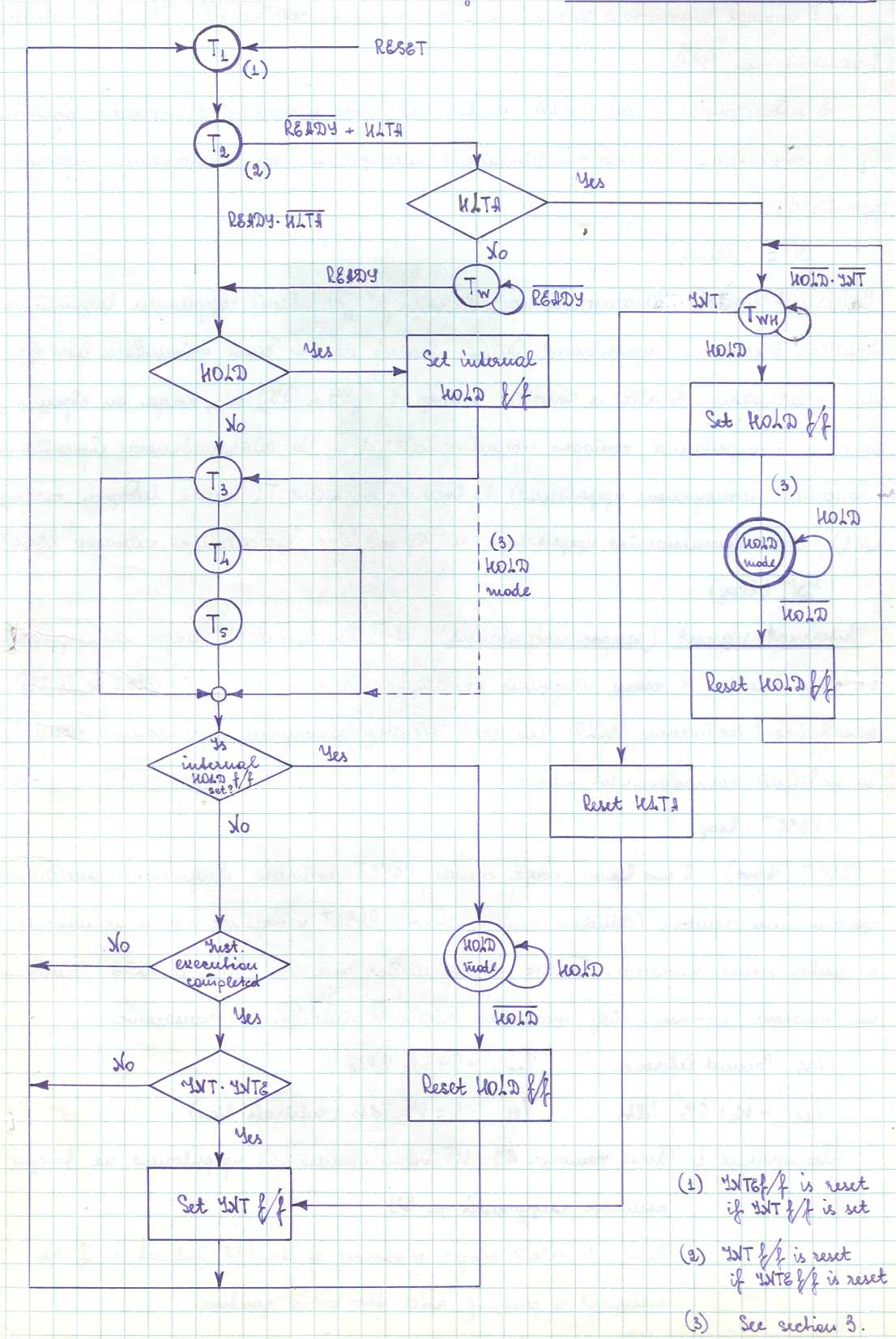

Диаграмма переходов при выполнении машинного цик¬ла в МП Intel 8080A пред-ставлена на рис. 2, на котором используются следующие обозначения TW - состояние ожидания МП; TWH - состояние ожидания МП при выпол¬нении команды останова HLT; Тi - состояние МП, i = 1 - 5.

Такт Т1 идентифицируется синхросигналом SYNC. В течение Т1 на шину адре-са выставляется содержимое счётчика команд, а на шине данных появляется слово со-стояния, определяющее тип выполняемого машинного цикла.

После Т1 всегда следует другое состояние Т2. В состоянии Т2 МП анализирует признак подтвержде¬ния останова HLТА и сигнал готовности READY и соот-ветственно переходит в состояние ТWH или ТW. Если имел место сигнал захвата HOLD, то внутренний триггер захвата устанавливается в состояние 1.

В состоянии Т3 действия определяются типом машинного цикла. В цикле выбор-ки МП интерпретирует код на шине данных как байт КОП, а в циклах чтения из памя-ти, записи в память, ввода и вывода информации осуществля¬ет обмен данными.

Состояния Т4 и Т5 являются необязательными, так как используются для внут-ренних преобразований в МП. Та¬ким образом, МП может переходить в состояние Т1 следующего машинного цикла после Т3, Т4 или Т5.

Рис.

2. Диаграмма переходов при выполнении

машинного цикла

Рис.

2. Диаграмма переходов при выполнении

машинного цикла

В МП Intel 8080A имеется десять типов машинных циклов, которые могут быть при выполнении команды: выборка байта команды, чтение из памяти, запись в память, чтение из стека, запись в стек, ввод, вывод, обработка прерывания, останов, обработка прерыва¬ния при останове. При этом первым машинным циклом всегда является выборка кода операции. Для определения типа машинного цикла в первом состоянии Т1 каждого машинного цикла на шину данных передается 8-разрядный код – слово состояния МП, который запоминается во внешнем регистре-фиксаторе и используется, для формирования системных управляющих сигналов для об¬ращения к памяти, периферийным устройствам. Назначение каждого разряда в слове состояния приведено в таблице 1.

Разряд |

Имя |

Определение |

D0 |

INTA |

признак подтверждения прерывания; используется для считывания в РК команды вызова подпрограммы обработки прерывания RST n |

D1 |

-WO |

признак записи-вывода; указывает, что в текущем машинном цикле будет выполняться запись в память или в порт вывода (при -WO = 0) |

D2 |

STACK |

признак указывает, что на АШ будет установлен адрес стека из указателя стека |

D3 |

HLTA |

признак подтверждает выполнение команды останова HLT |

D4 |

OUT |

признак вывода; указывает, что АШ содержит адрес порта вывода, а шина данных будет содержать данные при -WR = 0 |

D5 |

М1 |

признак указывает, что МП находится в цикле выборки первого байта команды |

D6 |

INP |

признак ввода; указывает, что АШ содержит адрес порта ввода, и входные данные должны быть по шине данных при DBIN = 1 |

D7 |

MEMR |

признак чтения; указывает, что ШД будет использована для чтения данных из памяти |

Таблица 1

Разряд Имя Определение

D0 INTA признак подтверждения прерывания; ис¬пользуется для считывания в РК команды вызова подпрограммы обработки прерывания RST n

D1 -WO признак записи-вывода; указывает, что в текущем машинном цикле будет выпол-няться запись в память или в порт вывода (при -WO = 0)

D2 STACK признак указывает, что на АШ будет установлен адрес стека из указателя стека

D3 HLTA признак подтверждает выполнение коман¬ды останова HLT

D4 OUT признак вывода; указывает, что АШ содержит адрес порта вывода, а шина данных будет содержать данные при -WR = 0

D5 М1 признак указывает, что МП находится в цикле выборки первого байта команды

D6 INP признак ввода; указывает, что АШ содержит адрес порта ввода, и входные данные должны быть по шине данных при DBIN = 1

D7 MEMR признак чтения; указывает, что ШД будет использована для чтения данных из па-мяти

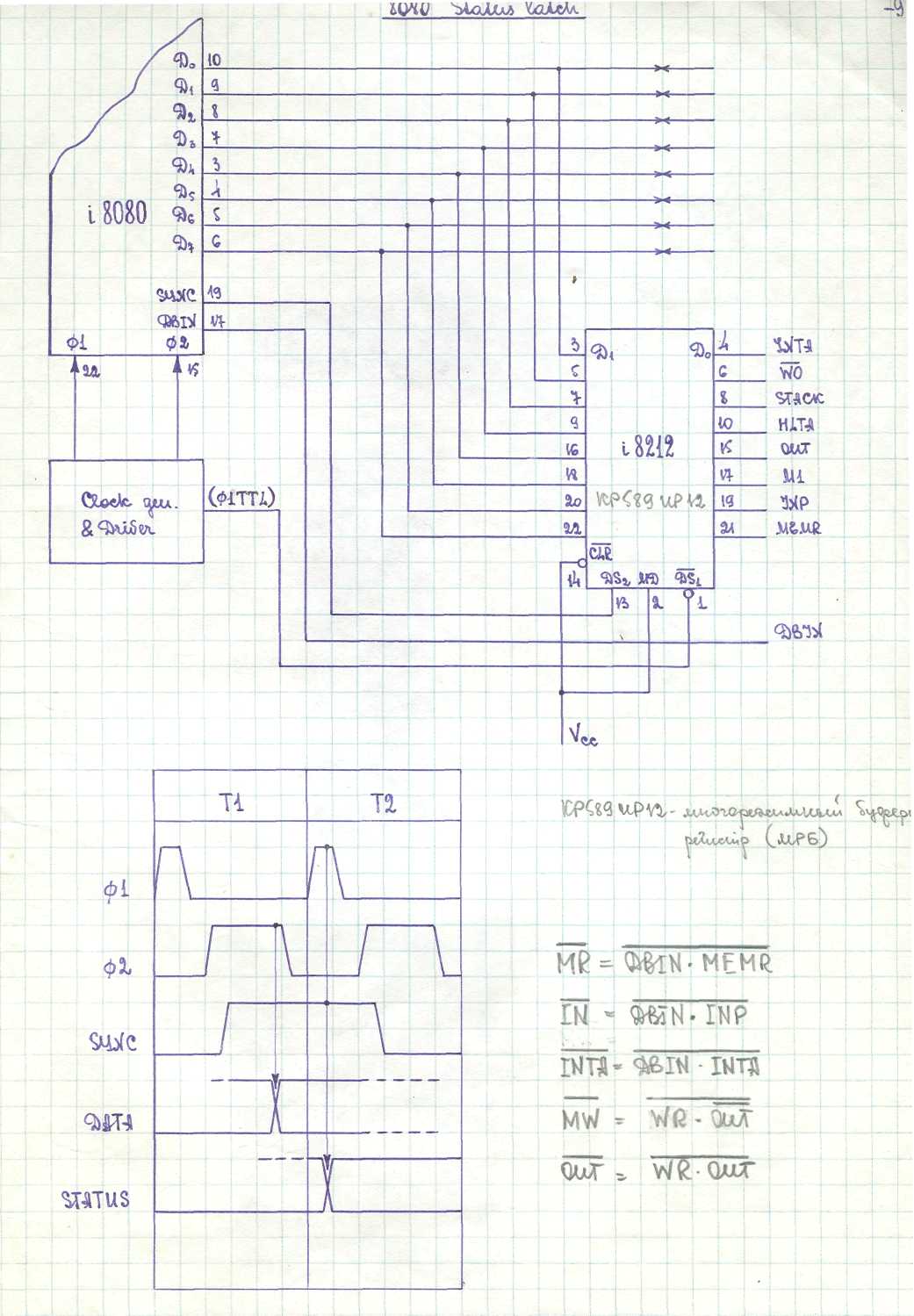

Формирование системных управляющих сигналов.

На¬бор управляющих сигналов, таких как, чтение из памяти (-MR), запись в па-мять (-MW), ввод информации(-IN),вывод информации (-OUT), подтверждение преры-вания -INTA обеспечивает прием и передачу кодов между МП, памятью и периферий-ными устройствами в определенные интервалы времени в соответствии с диаг¬раммой переходов машинного цикла. Данные сигналы не¬посредственно не формируются мик-ропроцессором, для их формирования используются сигналы приёма (DBIN) и записи (-WR) из МП и необходимые признаки из слова состояния:

- МR

=-(DВIN&

MR);

МR

=-(DВIN&

MR);

-IN= -(DВIN&INP);

-INTА = -(DВIN&INTA);

-MW = -(-WR&-OUT);

-OUT=-(-WR&ОUT);¬

Слово состояния загружается в 8-разрядный регистр-фиксатор, на¬пример, 8228, посредством сигнала синхронизации SYNC и тактирующего сигнала Φ2 уровня ТТЛ, формиру¬емого генератором тактовых сигналов, в начале такта Т2.

На рис. 3 показано формирование системных управ¬ляющих сигналов в соответствии с вышеприведёнными вы¬ражениями. Другие признаки слова состояния могут ис¬пользоваться при тестировании МП.

Остановимся

несколько подробнее на обработке

запросов прерывания. Устройст-во,

обслуживаемое МП в режиме прерывания,

инициирует прерывание путем формирования

на входе INT МП сигнала прерывания, который

может возникнуть в любом машинном цикле

команды. Однако, как видно из диаграм¬мы

переходов, текущая команда должна

завершиться, и только после этого МП

переходит к машинному циклу под¬тверждения

прерывания, который имеет ряд отличий

от цикла выборки команды.

Остановимся

несколько подробнее на обработке

запросов прерывания. Устройст-во,

обслуживаемое МП в режиме прерывания,

инициирует прерывание путем формирования

на входе INT МП сигнала прерывания, который

может возникнуть в любом машинном цикле

команды. Однако, как видно из диаграм¬мы

переходов, текущая команда должна

завершиться, и только после этого МП

переходит к машинному циклу под¬тверждения

прерывания, который имеет ряд отличий

от цикла выборки команды.

Во-первых, в слове состояния дополнительно к признаку машинного цикла вы-борки команды M1 содержится признак INTA, подтверждающий, что сигнал прерыва-ния воспринят МП.

Bo-вторых, СК не увеличивается на 1 в данном цикле, так как, увеличенный после выборки предыдущей команды, он должен быть за¬помнен в стековой памяти без изменения.

В-третьих, вместо команды из программной памяти на шину данных передается код, представляющий собой однобайтную команду RST n, n=0-7.

Команда RST n обеспечивает запоминание со¬держимого программного счетчика в стеке, и в СК форми¬руется один из восьми начальных адресов, в которых х¬ранятся первые команды подпрограмм обслуживания прерываний. Если область памяти в 8 байт недостаточна для размещения подпрограммы, что, как правило, имеет место, то путем использования команд перехода ее можно расширить. Таким образом, первые 64 ячейки памяти (0000Н – 003FH) зарезервированы для подпрограмм об¬работки преры-ваний