- •16. Способы определения переполнения при арифметических операциях.

- •Переполнение

- •18. Три концепции реализации мпс.

- •19. Микропроцессор 8080а: структурная схема, назначение выводов.

- •20. Диаграмма переходов для машинного цикла мп 8080а. Формирование сис-темных управляющих сигналов.

- •21. Система команд мп 8080а: группы команд и их характеристика:

- •22. Принципы организации мпс: модульность, магистральный способ обмена информацией, микропрограммное управление.

- •23. Системная шина мпс. Сравнительная характеристика мпс с общей шиной и с изолированной шиной.

- •24. Интерфейс микропроцессора с системной шиной.

16. Способы определения переполнения при арифметических операциях.

Переполнение

Если при выполнении операции сложения получают результат, который выходит за пределы диапазона представляемых чисел, то имеет место переполнение. Сложение двух чисел с разными знаками никогда не приводит к переполнению, чего нельзя сказать о сложении двух чисел с одинаковыми знаками, например,

Существует простое правило, позволяющее выявить наличие переполнения: при сложении переполнение происходит только в том случае, если слагаемые имеют одинаковые знаки, а знак суммы отличается от знака слагаемых. Иногда правило наличия переполнения формулируют, используя понятие переносов, возникающих при выполнении операции сложения: переполнение при сложении происходит в том случае, если значения битов переноса в знаковый разряд и из знакового разряда различны. Внимательное изучение табл. 1.2 показывает, что эти два правила эквивалентны.

Правило наличия переполнения можно также сформулировать, исходя из анализа рис. 1.1: прибавление к какому-либо числу положительного числа приводит к переполнению, если указатель пройдет границу между позициями +7 и −8.

Большинство ЭВМ для обнаружения переполнения имеют встроенные аппаратные средства.

17. Классификация микропроцессорных средств: секционированные МП, однокристальные МП, микропроцессорные комплекты интегральных схем (МПК ИС), однокристальные микроконтроллеры (микроЭВМ).

Секционные МП

Секционный микропроцессор (МП) образуется из нескольких модулей, конструк-тивно реализованных в виде отдельных БИС. К их числу относятся: процессорные сек-ции, содержащие АЛУ и РОН; контроллер последовательности микрокоманд (КПМК); память микрокоманд (ПМК).

МП состоит из двух функциональных блоков: микропрограммного устройства управления (МПУУ), включающего в себя ПМК и КПМК, и операционного устройства (ОУ), построенного из набора секций. Благодаря микропрограммированию и секционированию можно реализовать МП с нужными разрядностью и функциональными возможностями.

Секционные МП позволяют разрабатывать более быстродействующие МПС. Это достигается за счет гибкой адаптации структуры, длины слова и специального набора команд проектируемого МП к классу решаемых задач. Кроме того, иногда только за счет микропрограммирования критичных по времени функций или алгоритма решае-мой задачи можно повысить быстродействие системы в несколько раз по сравнению с реализацией на основе однокристального МП с фиксированной системой команд.

Перечисленные достоинства не даются даром, так как, например, разработка соб-ственной системы команд требует также разработки ПО для моделирования, редакти-рования и загрузки микропрограмм, интерпретирующих систему команд. Кроме того, сам процесс микропрограммирования даже при использовании микроассемблера явля-ется более трудоемким из-за сложных форматов микрокоманд по сравнению с коман-дами, необходимости учета временных диаграмм микрокомандного цикла и изучения других деталей на аппаратном уровне. Однако, несмотря на отмеченные трудности, секционные МП с микропрограммированием представляют мощное средство для по-строения МПС средней и высокой производительности, замены быстродействующих контроллеров, реализованных на основе схем с жесткой логикой, создания спецпро-цессоров для обработки сигналов (быстрое преобразование Фурье, цифровая фильтра-ция), процессоров систем передачи данных и других применений.

Однокристальные МП и их архитектура

МП с фиксированной разрядностью и набором команд конструктивно выполняется в виде одной БИС. Все выполняемые однокристальными МП операции определяются системой команд, которые он может выполнить.

Понятие архитектуры микропроцессора включает в себя структуру МП, систему команд и способы адресации, возможность совмещения выполнения команд во време-ни, наличие дополнительных устройств в составе микропроцессора, принципы и режимы его работы.

Классическое определение структуры процессора: процессор состоит из опера-ционного устройства и устройства управления. Операционное устройство служит для обработки данных и иногда называется арифметико-логическим устройством (АЛУ). Управляющее устройство выполняет функции выборки, декодирования и вычисления адресов операндов и также генерирует последовательности микрокоманд.

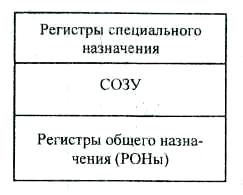

В настоящее время, когда процессор выполняется в виде микропроцессора, тем более как часть микроконтроллера, его структуру лучше представлять так называемой "моделью программиста". Модель программиста позволяет представить его структуру в виде программно доступных ресурсов, не вдаваясь в подробности внутренних связей. Такая модель используется проектировщиками МПС при разработке микропроцессорного устройства. Она является уникальной для каждого типа процессора, но в упрощенном виде может быть представлена следующими блоками (рис. 1).

Рис. 1. Упрощенная модель программиста

СОЗУ - сверхоперативное запоминающее устройство представляет собой набор регистров, находящихся на кристалле процессора (микропроцессора).

Регистры общего назначения (РОНы) - регистры, используемые для хранения, как данных, так и адресов, поэтому обычно представляют собой регистровые пары, которые соответствующие команды рассматривают как один регистр удвоенной длины.

Регистры специального назначения - регистры, за которыми закреплены специ-альные функции; аккумулятор (АСС), программный счетчик или счетчик команд (PC), указатель стека (SP), регистр состояния процессора (PSW) и т.д.

Основные характеристики процессора

К основным характеристикам процессора можно отнести:

• технологию изготовления;

• режимы энергопотребления;

• рабочий диапазон частот;

• цикл шины.

Технология изготовления. Основной причиной улучшения характеристик процессоров является совершенствование производственных процессов и используемых технологий, а не использование новых компьютерных архитектур.

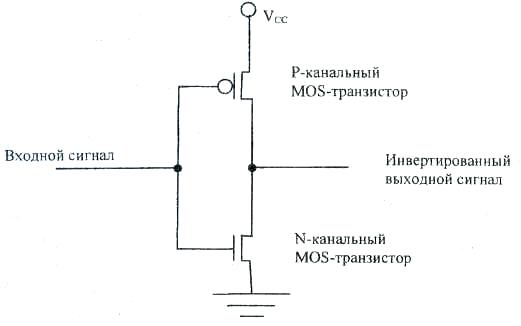

В настоящее время практически все микроконтроллеры выпускаются по CMOS-технологии (Complementary Metal Oxide Semiconductor - транзисторы со структурой Метал-Окисел-Полупроводник с дополняющим типом проводимости: р- и n-канальные). В микросхемах, выпускаемых по этой технологии, совместно используются р-канальные (PMOS) и n-канальные (NMOS) MOS-транзисторы.

Рис. 2. Схема CMOS-инвертора

На рис. 2 дана схема CMOS-инвертора (логического элемента "НЕ"). Когда на вход схемы поступает низкий потенциал, PMOS транзистор открыт, a NMOS - закрыт. При этом на выходе установится высокий потенциал (логическая 1), равный напряже-нию питания Vcc. Если на вход подан высокий потенциал, то PMOS транзистор будет закрыт, a NMOS - открыт, обеспечивая на выходе низкий потенциал "земли" (логический 0).

Когда элемент находится в одном из этих состояний, через транзисторы протекает очень маленький ток (ток утечки). С увеличением частоты переключения элемента возрастает средняя величина протекающего тока, и потребляемая элементом мощность увеличивается. Чтобы сократить энергопотребление, целесообразно эксплуатировать CMOS-микросхемы при минимально возможной частоте переключения. В "спящем" режиме, когда частота переключения снижается до нуля, потребление мощности значительно сокращается, так как переключения элементов не происходит, и ток в схеме не протекает.

Важной характеристикой логических элементов является порог переключения. Для CMOS-элементов значение порога переключения обычно составляет от 1,4В до Vcc/2. Различные логические элементы могут иметь разные пороги переключения. Прежде чем использовать элемент в проектируемом устройстве, необходимо убедиться, что его логические уровни (0 и 1) и порог переключения соответствуют уровням и порогам переключения других элементов устройства.

CMOS-элементы могут непосредственно работать с большинством других типов логических элементов, реализующих положительную логику. Следует только обратить внимание на возможность использования элементов с пониженным напряжением питания, которые имеют более низкие уровни логической 1 (низковольтная логика). В этом случае необходимо, чтобы уровень логической 1 (высокий уровень потенциала) всегда был выше порога переключения.

Режимы энергопотребления. При планировании энергопотребления для различ-ных устройств, использующих процессоры (микропроцессоры, микроконтроллеры), необходимо учитывать, что потребляемая ими мощность зависит от режима функционирования. Имеются три значения мощности, потребляемой процессором в различных рабочих условиях (данные режимы, в основном, характерны для микроконтроллеров). Первое - собственная мощность, необходимая для нормальной работы процессора. Второе - мощность, потребляемая внешними по отношению к нему устройствами. Третье - мощность, потребляемая в "спящем" режиме, когда процессор ожидает наступления внешнего события, переключающего его в рабочий режим. В зависимости от режима работы процессора, реализованное на его основе устройство может при одном и том же ресурсе энергии функционировать в течение нескольких часов или нескольких месяцев.

Собственная мощность - это мощность, которую потребляет процессор, когда к его выводам не подключены внешние устройства. Значение этой мощности зависит, главным образом, от тока, потребляемого при переключении CMOS-элементов, который является функцией скорости работы микроконтроллера. С уменьшением тактовой частоты собственная мощность значительно уменьшается. Очевидно, что дальнейшее снижение собственной мощности возможно при уменьшении напряжения питания. Реализация этой возможности зависит от типа используемого процессора и подключенных к нему устройств. Многие современные микросхемы могут работать при снижении напряжения питания до 2,0 В.

Мощность, потребляемая в режиме ввода/вывода, зависит от того, какую мощность процессор должен затратить на управление работой внешних устройств. Значение этой мощности определяется конкретным вариантом применения микроконтроллера. Если процессор выдает управляющие сигналы непрерывно, даже когда внешние устройства не требуют обслуживания, то данное устройство будет потреблять больший ток, а значит и мощность, чем это необходимо для нормальной работы.

Использование "спящего" режима (режима энергосбережения) может уменьшить потребляемую мощность с уровня в несколько милливатт до микроватт. Различают несколько вариантов "спящего" режима, отличающихся величиной потребляемой мощ-ности, вызванной остановкой тех или иных блоков процессора (СОЗУ, тактового генератора и др.). В этот режим процессор обычно входит после выполнения специальной команды. Если используется вариант с остановкой тактового генератора, то для выхода из данного режима и запуска тактового генератора требуется определенное время, порядка нескольких миллисекунд. Такая задержка может быть существенной для некоторых приложений.

Рабочий диапазон частот. Различают процессоры со статической и динамической структурой.

У процессоров с динамической структурой частота тактового генератора не должна быть ниже определенной технологией частоты, т.е. должна находиться в заданном диапазоне частот (от, минимальной частоты до максимальной).

В настоящее время большинство процессоров способны работать в очень широ-ком диапазоне частот: от нуля до десятков мегагерц (процессоры со статической струк-турой). Это возможно благодаря использованию полностью статической логики. Ши-рокий диапазон возможных рабочих частот позволяет разработчику лучше настроить процессор на выполнение конкретных заданных функций, снизить энергопотребление в соответствующих приложениях.

Однокристальные микропроцессоры можно разделить, в зависимости от особен-ностей их архитектуры, на следующие группы:

• RISC и CISC архитектуры;

• фон неймановской и гарвардской архитектуры;

• аккумуляторной, регистр-регистровой и стековой архитектуры;

• синхронные и асинхронные процессоры.

Процессоры с CISC (Complete Instruction Set Computer) архитектурой характеризуются полным набором команд. Вследствие большого разнообразия команд их формат (длина в байтах) различен.

Процессоры с RISC (Reduce Instruction Set Computer) архитектурой характеризуются сокращенным набором команд одинакового формата, выполняемых за один такт процессора. Выполнение более сложных, но редко встречающихся операций обеспечивают подпрограммы.

Основная идея построения RISC-процессора направлена на то, чтобы команды выполнялись за один машинный такт процессора (цикл шины равен такту генератора процессора). Это достигается за счет сокращения набора команд, введения одинакового формата команд, конвейерной обработки и большого сверхоперативного ОЗУ (ОЗУ на кристалле процессора), использования структуры с раздельными шинами. Сокращение набора команд ведет к упрощению внутренней структуры процессора и благодаря этому - к повышению его быстродействия. Кроме того, значительное упрощение структуры позволяет разместить на кристалле процессора большой объем регистровой памяти; сверхоперативного ОЗУ) и тем самым сократить обращения к оперативной памяти. Применение команд одинакового формата, как правило, большего разрядности шины данных, приводит к структуре с раздельными шинами и к необходимости размещения памяти команд на кристалле процессора. Таким образом, у RISC- процессоров вся память команд находится на кристалле, они выполняют команды за один такт, имеют большое число равноправных регистров (регистр-регистровая архитектура).

CISC-процессоры выполняют большой набор команд с различными видами адресации (непосредственная, индексная и т.д.). Это даёт разработчику возможность выбрать наиболее подходящую команду для выполнения необходимой операции. Формат команд кратен разрядности шины данных, что позволяет использовать память команд как внутреннюю, так и внешнюю. В последнем случае, в зависимости от длины формата, команда будет считываться из памяти команд побайтно (при байтовой разрядности шины данных) за несколько машинных циклов.

Имеется много процессоров, называемых RISC, на самом деле относящихся к CISC. Более того, в некоторых приложениях CISC-процессоры выполняют программ-ный код быстрее, чем это делают RISC-процессоры, или решают такие задачи, которые RISC-процессоры не могут выполнить.

Различают процессоры с архитектурой фон Неймана и с архитектурой Гарвард-ской лаборатории. Для первой архитектуры память программ и память данных нахо-дятся в едином пространстве, и нет никаких признаков, указывающих на тип информа-ции в ячейке памяти. Для второй архитектуры память программ и память данных раз-делены, имеют свои адресные пространства и способы доступа к ним.

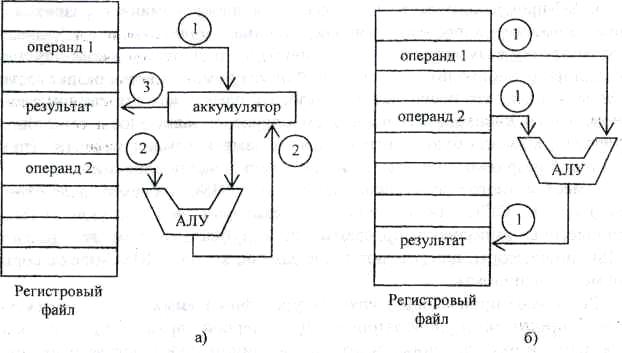

Разделение на аккумуляторную и регистр-регистровую архитектуру связано с равноправностью использования регистров процессора. Возможность равноправного использования всех регистров процессора называется "ортогональностью", или "симметричностью" процессора. Это обеспечивает дополнительную гибкость при выполнении некоторых операций.

В аккумуляторной архитектуре один из регистров специального назначения - аккумулятор - по умолчанию является источником одного из двух операндов и одновременно приемником результата операции, выполняемой в АЛУ. Такой подход позволяет существенно уменьшить формат команды за счет адресации в поле операндов только одного из операндов. Для выполнения, например, операции сложения в процессорах данной архитектуры требуется, кроме собственно команды, по крайней мере, еще две операции пересылки: загрузка первого операнда в аккумулятор и через него в АЛУ, а также пересылка результата операции из аккумулятора по месту назначения после завершения операции. На рис. 3 а схематично показана последовательность выполнения команды в процессоре аккумуляторной архитектуры, а на рис. 3 б – в процессоре регистр-регистровой архитектуры.

Рис. 3. Аккумуляторная архитектура (а) и регистр-регистровая архитектура (б)

Основным отличием регистр-регистровой архитектуры от аккумуляторной является то, что любые ячейки СОЗУ процессора, называемого также регистровым ОЗУ, могут рассматриваться либо как операнды-источники, либо как аккумулятор для приема результата операции. При таком подходе любая из команд процессора может быть трехоперандной и необходимость в дополнительных операциях пересылки данных из аккумулятора и обратно отпадает. Естественно, что регистр-регистровая архитектура требует более сложного формата команды. Наряду с полем кода операции в формате команды будут присутствовать поля адресов операндов-источников и операндов приемников. Регистр-регистровая архитектура является обязательным элементом RISC-процессоров.

У процессоров со стековой организацией нет ни аккумулятора, ни РОНов. В простейшем случае их программно доступные регистры служат для указания адресов вершины стека (указатель стека SP) и следующей команды программы (счетчик команд PC), а также хранения состояний отдельных устройств процессора (регистр состояний PSW). Память МПС со стековой организацией разделяется на две части, одна из которых отводится под моделируемый стек, а другая - под программу и глобальные данные.

Подобная организация позволяет строить программы, в которых используются:

• адресные команды для загрузки операнда из области данных в стек (PUSH) или извлечения операнда из стека (POP);

• безадресные команды, инициирующие извлечение из стека двух слов (или од-ного слова), выполнение над ними действий, указанных кодом операции команды, и загрузка результата в стек.

Подробности:

При составлении программы вычисления арифметических выражений для таких процессоров используют польскую инверсную (бесскобочную) запись выражений. В бесскобочной записи операция записывается не между операндами (X+Y), а после них (XY+), т.е. выражение

3ln(Х+1)А/Х2

переписывают в виде

3Х1+ln*АХ2↑/,

где * и ↑ используются для указания операции умножения и возведения в степень соот-ветственно.

Реализация алгоритма производится в следующем порядке:

1. Записывать в стек символы, начиная с левого, до тех пор, пока не встретится знак операции.

2. Взять два ближайших операнда (с вершины стека), выполнить над ними операцию и поместить результат обратно в стек.

3. Если в стеке осталось одно значение, то осуществить переход на пункт 1. И так до окончания вычисления выражения.

Процессоры со стековой организацией имеют большие преимущества при выполнении сложных вычислений, их команды короче и занимают меньше места в памяти. Такую организацию имеют карманные калькуляторы. Однако быстродействие процессора стековой архитектуры, как правило, ниже, чем у рассмотренных ранее, поскольку единственным "рабочим регистром" при выполнении арифметических операций является вершина стека.

По характеру временной организации работы различают асинхронные (самотактируемые) и синхронные процессоры. Синхронные процессоры - это процессоры, в которых начало и конец выполнения операций задаются устройством управления (время выполнения операций в этом случае не зависит от вида выполняемых команд и величин операндов). Все переключения внутри микросхем привязываются к переднему или заднему фронтам тактового сигнала, благодаря чему узлы МПС работают синхронно. В МПС для этого используется системный тактовый генератор, сигналы от которого поступают во все микросхемы системы.

Асинхронные процессоры – позволяют начало выполнения каждой следующей операции определить по сигналу фактического окончания выполнения предыдущей операции. Для более эффективного использования каждого устройства микропроцессорной системы в состав асинхронно работающих устройств вводят электронные цепи, обеспечивающие автономное функционирование устройств. Закончив работу над какой-либо операцией, устройство вырабатывает сигнал запроса, означающий его готовность к выполнению следующей операции. Термины "асинхронный процессор" и "самотактируемый процессор" – синонимы: процессор, имеющий один или несколько внутренних тактовых генераторов, не требует центрального генератора тактовой частоты и схем, поддерживающих распространение общего внешнего тактового сигнала. Такие процессоры излучают гораздо меньше радиоволн и расходуют меньше энергии по сравнению с синхронными процессорами. При проектировании внутренних блоков асинхронных процессоров не рассматриваются вопросы их синхронизации с другими блоками. Для связи между блоками используется единый протокол: запрос - ответ с квитированием. Когда вычисления не производятся, блоки не потребляют почти ничего, находясь в спящем режиме, но, тем не менее, мгновенно реагируют на запросы. Таким образом, процессом вычислений управляют данные: нет данных - нет вычислительной активности. Понятно, что такие блоки легче интегрировать в так называемые системы на кристалле (SoC), и в итоге их общая производительность выше, чем у синхронных процессоров. Повышение производительности достигается за счет того, что блоку нет необходимости ждать прихода внешнего тактового сигнала, чтобы выполнить свою работу.

Асинхронная система получается более надежной, поскольку ее подсистемы ра-ботают в более широких диапазонах изменений напряжения питания и температуры. Важно, чтобы самотактируемым был не только процессор, но и остальные микросхемы: ОЗУ, контроллеры и т. д. Весь набор таких микросхем и именуется самотактируемой логикой (clockless logic). Термин "нетактируемая логика" может ввести в заблуждение, поэтому следует подчеркнуть, что для работы асинхронных микросхем тактовые сигналы, как правило, нужны, но их источник локален.

Микропроцессорные комплекты интегральных схем

Принцип модульной организации предполагает построение МПС на основе набора модулей. Как для однокристальных, так и для секционированных микропроцессоров создаются дополнительные БИС, такие как, ОЗУ, ПЗУ, ППЗУ, различные интерфейсы, контроллеры ВУ и т.д. Вместе с микропроцессорными БИС определённой серии они образуют микропроцессорный комплект интегральных схем (МПК ИС).

МПК ИС - совокупность конструктивно и электрически совместимых БИС, пред-назначенных для построения МПС с определенным составом и требуемыми характе-ристиками.

Основу МПК ИС составляют микропроцессорные БИС. Обычно эти БИС относятся к ИС одной серии.

Дополнительные БИС могут иметь то же обозначение, что и микропроцессорные БИС, или другой номер серии или даже иной вид корпуса.

Однокристальные микроконтроллеры

Успехи микроэлектроники в повышении степени интеграции микросхем позволили создать в одном кристалле третью разновидность микропроцессорных БИС - однокристальные микроЭВМ, которые чаще называют однокристальными микроконтроллерами. Операционный блок, ОЗУ, ПЗУ, УУ, АЛУ и другие функциональные части этого типа микроЭВМ выполнены в одном кристалле полупроводникового материала. Программа и набор команд, которые выполняются микроконтроллерами, как правило, постоянны и хранятся в собственном ПЗУ.

В настоящее время существует огромное количество разнообразных устройств этого класса, доступных потребителям. Их можно разделить на следующие основные типы:

• встраиваемые 8-разрядные микроконтроллеры;

• 16- и 32-разрядные микроконтроллеры;

• цифровые сигнальные процессоры (DSP).

Встраиваемые микроконтроллеры

Промышленностью выпускается очень широкая номенклатура встраиваемых (embedded) микроконтроллеров. В этих микроконтроллерах все необходимые ресурсы (память, устройства ввода-вывода и т.д.) располагаются на одном кристалле с процес-сорным ядром. Все, что Вам необходимо сделать - это подать питание и тактовые сиг-налы. Встраиваемые микроконтроллеры могут базироваться на существующем микро-процессорном ядре или на процессоре, разработанном специально для данного микро-контроллера. Это означает, что существует большое разнообразие функционирования даже среди устройств, выполняющих одинаковые задачи.

Основное назначение встраиваемых микроконтроллеров - обеспечить с помощью недорогих средств гибкое (программируемое) управление объектами и связь с внешни-ми устройствами. Эти микроконтроллеры не предназначены для реализации комплекса сложных функций, но они способны обеспечить эффективное управление во многих областях применения.

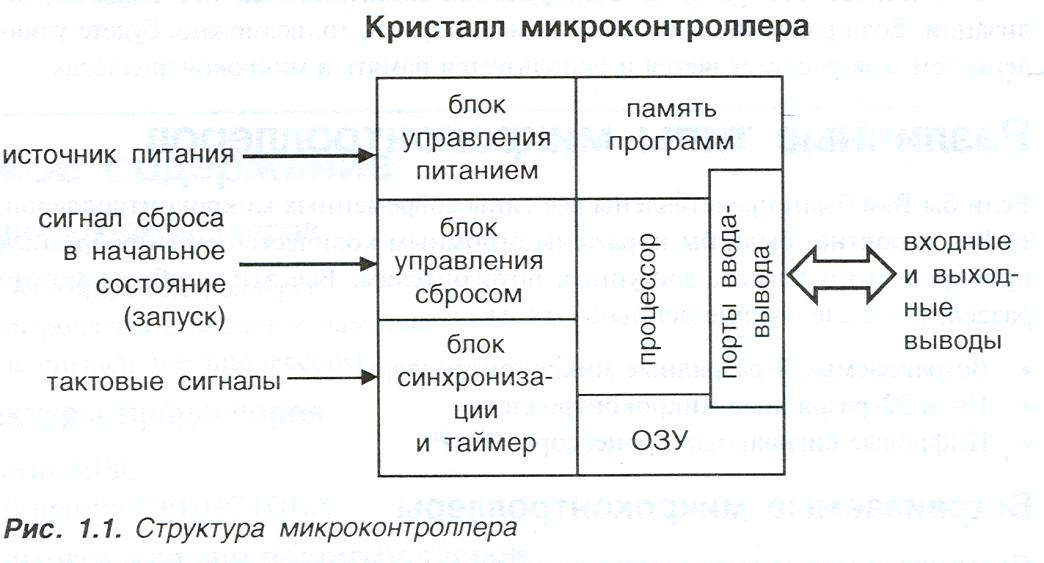

Встраиваемые микроконтроллеры содержат значительное число вспомогатель-ных устройств, благодаря чему обеспечивается их включение в реализуемую систему с использованием минимального количества дополнительных компонентов. В состав этих микроконтроллеров обычно входят:

• схема начального запуска процессора (Reset);

• генератор тактовых импульсов;

• центральный процессор;

• память программ (E(E)P)ROM и программный интерфейс;

• память данных RAM;

• средства ввода-вывода данных;

• таймеры, фиксирующие число командных циклов.

Общая структура микроконтроллера показана на рис. 1.1. Эта структура дает представление о том, как микроконтроллер связывается с внешним миром.

Рис. 4. Структура микроконтроллера

Более сложные встраиваемые микроконтроллеры могут дополнительно реализо-вать следующие возможности:

• встроенный монитор/отладчик программ;

• внутренние средства программирования памяти программ (ROM);

• обработка прерываний от различных источников;

• аналоговый ввод-вывод;

• последовательный ввод-вывод (синхронный и асинхронный);

• параллельный ввод-вывод (включая интерфейс с компьютером);

• подключение внешней памяти (микропроцессорный режим).

Все эти возможности значительно увеличивают гибкость применения микрокон-троллеров и делают более простым процесс разработки систем на их основе. Следует заметить, что для реализации этих возможностей в большинстве случаев требуется расширение функций внешних выводов.

Раньше микроконтроллеры изготавливались по биполярной или NMOS техноло-гии. Все современные микроконтроллеры производятся с помощью CMOS технологии, которая позволяет значительно уменьшить размер кристалла и рассеиваемую мощ-ность.

Типичные значения максимальной частоты тактовых сигналов составляют для различных микроконтроллеров 10 - 20 МГц. Главным фактором, ограничивающим их скорость, является время доступа к памяти, применяемой в микроконтроллерах. Одна-ко для типичных применений это ограничение не является существенным.