- •1. Полупроводниковые выпрямители: классификация, основные параметры.

- •2. Электрические фильтры.

- •3. Стабилизаторы напряжения.

- •Линейный стабилизатор

- •Параллельный параметрический стабилизатор на стабилитроне

- •Стабилизаторы переменного напряжения Феррорезонансные стабилизаторы

- •Современные стабилизаторы

- •4. Тиристоры: классификация, основные параметры.

- •5. Принципы управления тиристорными преобразователями

- •6. Регулятор переменного напряжения на тиристорах.

- •7. Выпрямитель на тиристорах.

- •8. Классификация и основные характеристики тиристорных усилителей.

- •9. Анализ работы однокаскадных усилителей.

- •10. Многокаскадные усилители.

- •11. Усилители напряжения, повторители.

- •12. Усилители постоянного тока. Дрейф нуля.

- •13. Дифференциальные каскады.

- •14. Операционный усилитель (оу). Основные характеристики.

- •15. Обратные связи в оу. Их влияние на параметры и характеристики усилителя.

- •Классификация обратных связей в усилителях

- •Влияние отрицательной обратной связи на основные характеристики усилителя

- •16. Основные типы усилителей на базе оу.

- •17. Импульсные сигналы. Области применения. Основные характеристики.

- •18. Формирователи импульсных сигналов. Электронные ключи.

- •19. Автогенераторы. Мультивибраторы.

- •20. Триггер Шмитта.

- •21. Анализ и синтез цифровых систем. Основные законы алгебры логики.

- •22. Основные электронные устройства логики.

- •23. Общие сведения о цифровых электронных устройствах.

- •25. Полусумматоры, сумматоры.

- •26. Шифраторы, дешифраторы.

- •27. Мультиплексоры, демультиплексоры.

- •28. Регистры.

- •29. Счетчики.

- •30. Элементы памяти.

- •31. Аналого-цифровые и цифро-аналоговые преобразователи.

- •32. Порт.

- •33. Микропроцессор (мп).

- •34. Микроконтроллер в схеме контроля и управления техпроцессом.

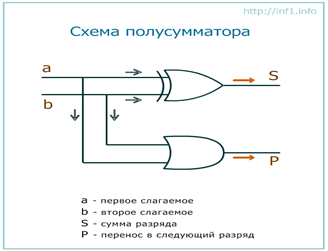

25. Полусумматоры, сумматоры.

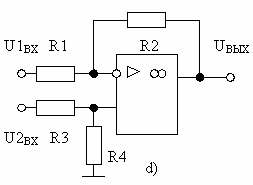

Ко входам операционного усилителя могут быть подключены несколько

резисторов. В этом случае выходное напряжение будет суммироваться по входным напряжениям с учетом знака и коэффициента масштабирования. Такие усилители называютя сумматорами (рисунок 54). Ко входам операционного усилителя могут быть подключены несколько резисторов. В этом случае выходное напряжение будет суммироваться по входным напряжениям с учетом знака и коэффициента масштабирования. Такие усилители называются сумматорами (рисунок 54).

Рисунок – схема сумматора

Полусумматор — логическая схема, имеющая два входа и два выхода (двухразрядный сумматор, бинарный сумматор). Полусумматор используется для построения двоичных сумматоров. Полусумматор позволяет вычислять сумму A+B, где A и B — это разряды двоичного числа, при этом результатом будут два бита S и C, где S — это бит суммы по модулю 2, а C — бит переноса. Однако, как можно заметить, для построения схемы двоичного сумматора (трёхразрядный сумматор, тринарный сумматор) необходимо иметь элемент, который суммирует три бита A, B и C, где C — бит переноса из предыдущего разряда, таким элементом является полный двоичный сумматор, трёхступенчатая разновидность которого состоит из двух полусумматоров и логического элемента 2ИЛИ.

26. Шифраторы, дешифраторы.

Шифратор (кодер) —логическое устройство, выполняющее логическую функцию (операцию) — преобразование позиционного n-разрядного кода в m-разрядный двоичный, троичный или k-ичный код. Двоичный шифратор выполняет логическую функцию преобразования унитарного n-ичного однозначного кода в двоичный. При подаче сигнала на один из n входов (обязательно на один, не более) на выходе появляется двоичный код номера активного входа.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением n=2m:

где

n— число входов,

m— число выходных двоичных разрядов.

Троичный шифратор выполняет логическую функцию преобразования унарно n-ичного однозначного (одноединичного или однонулевого) кода в троичный. При подаче сигнала («1» в одноединичном коде или «0» в однонулевом коде) на один из n входов на выходе появляется троичный код номера активного входа.

Число входов и выходов в полном троичном шифраторе связано соотношением: n=3m, где

n— число входов,

m— число выходных троичных разрядов.

Число входов и выходов в полном k-ичном шифраторе связано соотношением: n=km, где

n— число входов,

m— число выходных k-ичных разрядов,

k— основание системы счисления.

Приоритетный шифратор отличается от шифратора наличием дополнительной логической схемы выделения активного уровня старшего входа для обеспечения условия работоспособности шифратора (только один уровень на входе активный). Уровни сигналов на остальных входах схемой игнорируются.

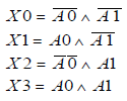

Дешифратором (декодером) называют комбинационное устройство, предназначенное для распознавания различных кодовых комбинаций сигналов на его входах. В простейшем случае каждой кодовой комбинации на входах соответствует активный уровень сигнала только на одном из выходов дешифратора. Такой дешифратор может применяться, напримep, для управления работой нескольких исполнительных механизмов. Тогда для включения одного из них на входы дешифратора достаточно подать присвоенный этому механизму цифровой код. В более общем случае каждой определенной комбинации на т входах дешифратора соответствует n-элементный код на его выходах. Такие дешифраторы иногда называют преобразователями кодов, Они широко используются в вычислительной технике, а также в приборах с цифровой индикацией, например, для управления индикаторами на светоизлучающих диодах. Поскольку десятичные цифры (от 0 до 9) представляются 4-разрядным двоичным кодом, а стилизованные изображения всех десятичных цифр в известных типах светодиодных индикаторов чаще всего составляют из семи светящихся сегментов, такой дешифратор должен иметь 4 входа, 7 выходов и распознавать первые десять из 16 возможных входных кодовых комбинаций. Условное обозначение микросхем дешифраторов на корпусе ИС после номера ее серии имеет буквы ИД. Дешифратор один из n – комбинационная схема, обеспечивающая формирование для n-входовой схемы активного сигнала только на одном из его выходов. Максимальное количество выходов в дешифраторе может быть равным 2n. Уравнения истинности для выходов дешифратора:

.

.

Принцип построения дешифратора

Демультиплексором называют комбинационное устройство с несколькими выходами и управляющими входами, коммутирующие сигнал на единственном информационном входе на один из выходов в соответствии с цифровым кодом на управляющих входах. При циклическом переборе на управляющих входах всех возможных кодовых комбинаций демультиплексор выполняет преобразование последовательного двоичного кода на его информационном входе в параллельный код, который возникает на выходах по окончании полного цикла этого перебора.