- •1)Основные классы интегральных схем и их разновидности. Эсл схемы.

- •2) Основные классы интегральных схем и их разновидности. Кмоп схемы.

- •1. Аналоговые микросхемы — входные и выходные сигналы изменяются по закону непрерывной функции в диапазоне от положительного до отрицательного напряжения питания.

- •3)Основные классы интегральных схем и их разновидности. Ттл схемы.

- •1. Аналоговые микросхемы — входные и выходные сигналы изменяются по закону непрерывной функции в диапазоне от положительного до отрицательного напряжения питания.

- •3. Аналого-цифровые микросхемы совмещают оба.

- •4)Основные классы интегральных схем и их разновидности. И2л схемы.

- •1. Аналоговые микросхемы — входные и выходные сигналы изменяются по закону непрерывной функции в диапазоне от положительного до отрицательного напряжения питания.

- •3. Аналого-цифровые микросхемы совмещают оба.

- •5)Использование схем с тристабильными выходами в цифровых устройствах.

- •6)Комбинационные цифровые устройства. Сумматоры и полусумматоры.

- •7)Комбинационные цифровые устройства. Пороговые схемы.

- •9)Комбинационные цифровые устройства. Мультиплексоры и демультиплексоры.

- •11)Комбинационные цифровые устройства. Дешифратор.

- •12)Комбинационные цифровые устройства. Цифровые компараторы.

- •13)Устройства последовательного типа. Триггеры. Классификация по функциональному признаку и по способу записи информации в триггер.

- •14)Rs триггер и их разновидности. Реализация. Режим работы.

- •15)D-триггеры. Реализация. Режим работы.

- •16)Jk-триггер. Реализация. Режим работы.

- •17)Триггеры с внутренней задержкой.

- •18)Триггеры. Классификация триггеров. Счетный режим работы триггеров. Использование триггеров при построении регулярных цифровых устройств.

- •19)Классификация регистров. Регистры памяти.

- •20)Регистры сдвига.

- •21)Универсальные ригистры.

- •22)Статические озу.

- •23)Счетчики. Классификация. Суммирующие двоичные счетчики. Их реализация.

- •24)Двоичные вычитающие и реверсивные счетчики.

- •25)Счетчики с произвольным коэффициентом счета. Их реализация.

- •26)Устройства для аналого-цифрового преобразования электрических сигналов в сау.

- •27)Классификация ацп. Ацп с двойным интегрированием.

- •28)Ацп с накоплением.

- •29)АЦп сравнения. Ацп поразрядного кодирования.

- •30)Параллельные ацп.

- •31)Последовательно-Параллельные ацп.

- •Параметры цап

- •34)Микропроцессоры. Структура, организация и функционирование микропроцессорных систем.

- •35)Существующая классификация основных типов однокристальных микроконтроллеров, используемых в системах управления и контроля.

- •37)Организация памяти микропроцессорных систем. Виды памяти.

- •38)Понятие системы команд. Виды команд. Формат команд. Коп. Операнд.

- •39)Способы адресации, используемые в мп и мк.

- •40)Архитектурные методы повышения производительности микроконтроллеров.

- •41,48)Виды обмена информацией между мпс и периферийными устройствами.

- •43)Запросы на прерывание. Порядок обслуживание прерываний и тд.

- •45)Структура микропроцессора Кр580вм80а

- •46) Алгоритм управления циклом выполнения команд управляющего автомата мп к580.

- •47)Risc микроконтроллеры. Особенности их архитектуры и функционирования.

- •50)8Ми разрядные периферийные микроконтроллеры pic.

- •51)8Ми разрядные универсальные однокристальные микроконтроллеры Intel mcs-51.

- •52)8Ми разрядные универсальные однокристальные микроконтроллеры семейства avr/

- •54)16 Разрядные универсальные микроконтроллеры семейства Сиеменс.

- •55)32 Разрядные микроконтроллеры.

- •56)Контроллеры цифровой обработки сигналов. Dsp процессоры.

- •57)Программируемые логические интегральные схемы.

1)Основные классы интегральных схем и их разновидности. Эсл схемы.

Интегральная схема — микроэлектронное устройство — электронная схема произвольной сложности , изготовленная на полупроводниковой пластине или плёнке и помещённая в неразборный корпус, или без такового. Схемы бывают –логические системотехнические (триггеры, компораторы, итп), принцип.электрич (конденс. ,транзист, резист,итп).Классифицируются от степени интеграции. (малая интегральная схема (МИС) — до 100 элем в кристалле, (СИС -1000)(БИС-10000) (СБИС-1млн) (УБИС-1млрд) (ГБИС более 1млрд).

Делятся по виду обраб сигн (анал, цифр, анал-цифр)

1. Аналоговые микросхемы — входные и выходные сигналы изменяются по закону непрерывной функции в диапазоне от положительного до отрицательного напряжения питания.

2. Цифровые микросхемы — входные и выходные сигналы могут иметь два значения: логический ноль или логическая единица, каждому из которых соответствует определённый диапазон напряжения. (меньшнее энерго потреб из-за примен импульс сигн. Транзист либо закрыт(0) либо прописк ток (1). 2,5-5в или 0-0,5 – высокая помехоустоичивость)

3. Аналого-цифровые микросхемы совмещают оба.

Эмиттрено связная логика - это семейство цифровых интегральных микросхем на основе дифференциальных транзисторных каскадов. ЭСЛ является самой быстродействующей из всех типов логики, построенной на биполярных транзисторах. Это объясняется тем, что транзисторы в ЭСЛ работают в линейном режиме, не переходя в режим насыщения, выход из которого замедлен.

Различные варианты элементов ЭСЛ реализуются на основе простейшей логической схемы – переключателя тока

2) Основные классы интегральных схем и их разновидности. Кмоп схемы.

Интегральная схема — микроэлектронное устройство — электронная схема произвольной сложности , изготовленная на полупроводниковой пластине или плёнке и помещённая в неразборный корпус, или без такового. Схемы бывают –логические (Логич инверторы или-не и-не итп), системотехнические (триггеры, компораторы, итп), принцип.электрич (конденс.,транзист,резист,итп).

Классифицируются от степени интеграции. (малая интегральная схема (МИС) — до 100 элем в кристалле, (СИС -1000)(БИС-10000) (СБИС-1млн) (УБИС-1млрд) (ГБИС более 1млрд).

Делятся по виду обраб сигн (анал, цифр, анал-цифр)

1. Аналоговые микросхемы — входные и выходные сигналы изменяются по закону непрерывной функции в диапазоне от положительного до отрицательного напряжения питания.

2. Цифровые микросхемы — входные и выходные сигналы могут иметь два значения: логический ноль или логическая единица, каждому из которых соответствует определённый диапазон напряжения. (меньшнее энерго потреб из-за примен импульс сигн. Транзист либо закрыт(0) либо прописк ток (1). 2,5-5в или 0-0,5 – высокая помехоустоичивость)

3. Аналого-цифровые микросхемы совмещают оба.

КМОП (комплементарная логика на транзисторах металл-оксид-полупроводник) В технологии КМОП используются полевые транзисторы с изолированным затвором с каналами разной проводимости. Отличительной особенностью является очень малое энергопотребление в статическом режиме, наличие как n-, так и p-канальных полевых транзисторов (обладают более высоким быстродействием и меньшим энергопотреблением), более сложным технологическим процессом изготовления.

Типы КМОП-схем: полностью комплементарные, домино, буферные и гибридные.

Структура ПКМОП-схемы состоят из двух каскадов: p-каскада и n-каскада. Любой вход разветвляется и управляет затворами двух транзисторов p и n. При низком напряжении на входе p-транзистор открыт, а n-транзистор закрыт и на выходе имеется высокое напряжение. В этой схеме, если она исправна, один из транзисторов всегда закрыт, и ток от источника питания на землю отсутствует.

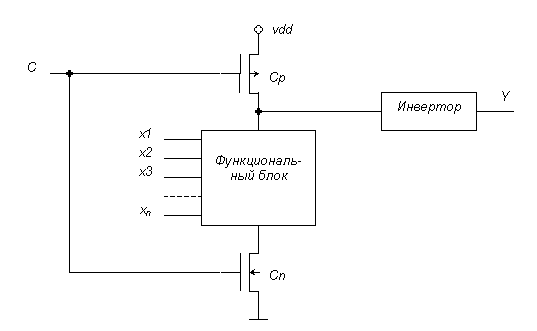

Структура КМОП-схемы типа домино относится к категории динамических схем. p-каскад состоит из одного p-транзистора, управляемого сигналом тактирования. n-каскад реализует заданную функцию на n-транзисторах, причем n-каскад подсоединяется к земле через управляемый n-транзистор. Когда сигнал тактирования равен 0, на выходе схемы устанавливается 0. Когда сигнал тактирования равен 1, на выходе устанавливается значение, определяемое n-каскадом. Если при этом существует активизированный путь между выходом и землей, то на выходе устанавливается 1. Если такого пути нет, то на выходе сохраняется значение 0 за счет заряда паразитной емкости на входе инвертора.