- •«Пермский национальный исследовательский политехнический университет»

- •Цель работы

- •Индивидуальное задание

- •1.Теоретические сведения

- •Основные команды языка Ассемблер

- •Команды пересылки.

- •1) Пересылка данных

- •2) Пересылка адресов

- •4) Пересылка в стек и из стека

- •Арифметические операции.

- •1) Команды счёта

- •2) Арифметические операции над двоичными кодами.

- •3) Команда сравнения:

- •Команды корректировки.

- •Команды логических операций.

- •1) Поразрядные логические операции:

- •2) Команды сдвига

- •Команды передачи управления.

- •Команды организации цикла.

- •Команды вызова процедур и возврата из них.

- •Команды прерываний и возврата из них.

- •Функции ввода/вывода dos.

- •2.Расчетно-графическая часть

- •Листинг программы:

- •Библиографический список

Министерство образования и науки Российской Федерации

Федеральное государственное бюджетное образовательное учреждение

высшего профессионального образования

«Пермский национальный исследовательский политехнический университет»

Кафедра Автоматизации технологических процессов и производств

Отчет по лабораторной работе № 8 |

Знакомство с языком ассемблера и работой отладчика Turbo Debuggеr |

(название лабораторной работы)

|

|

Выполнил |

||

студент гр. |

КСК-11 |

|

|

Махалов В.А |

|

(подпись) |

(Ф.И.О.) |

|

|

||

Проверил Преподаватель |

||

|

Сташков С.И. |

|

(подпись) |

(Ф.И.О.) |

|

Пермь 2013

Цель работы

Научиться анализировать ход выполнения программы на языке Ассемблера при помощи отладчика TurboDebugger.

Индивидуальное задание

Напишите программу, которая пересылает информацию из области с начальным адресом LIST и конечным адресом LIST+20 в область с соответствующими адресами BLK и BLK+20.

1.Теоретические сведения

Turbo Assembler (TASM) — программный пакет компании Borland, предназначенный для разработки программ на языке ассемблера для архитектуры x86. Кроме того, TASM может работать совместно с трансляторами с языков высокого уровня фирмы Borland, такими как Turbo C и Turbo Pascal. Как и прочие программные пакеты серии Turbo, Турбо Ассемблер больше не поддерживается.

TASM до сих пор используется для обучения программированию на ассемблере под архитектуру x86. Многие находят его очень удобным и продолжают его использовать, расширяя набором дополнительных макросов.

Пакет TASM поставляется вместе с компоновщиком Turbo Linker и порождает код, который можно отлаживать с помощью Turbo Debugger.

По умолчанию TASM работает в режиме совместимости с другим распространённым ассемблером — Microsoft Macro Assembler, то есть TASM умеет транслировать исходники, разработанные под MASM. Кроме того, TASM имеет режим IDEAL, улучшающий синтаксис языка и расширяющий его функциональные возможности.

Компоновка

Компоновка программы создает готовую для работы программу, которая называется также исполняемой программой или загрузочным модулем. При этом решаются две основные задачи:

если в программе используются функции, например, sin, exp и т.д., соответствующие им программные модули выбираются из библиотеки подпрограмм соответствующей системы программирования и вставляются в объектный модуль;

объектный модуль преобразуется в соответствии с реальными адресами основной памяти, куда будет размещаться программа для выполнения.

Трансляция

Процесс преобразования программы, написанной на одном языке программирования, в программу на другом языке.

Как правило, трансляция — это создание программы в машинных кодах, которую можно выполнять. Трансляция обеспечивает включение библиотечных подпрограмм, модулей, процедур в итоговую программу на машинном языке.

Различают два вида трансляции:

компиляцию, при которой результат получается в виде готовой программы, выполняемой независимо от исходного текста программы;

интерпретацию, при которой трансляция и выполнение программы происходит покомандно.

Отладка — этап разработки компьютерной программы, на котором обнаруживают, локализуют и устраняют ошибки. Чтобы понять, где возникла ошибка, приходится :

узнавать текущие значения переменных;

и выяснять, по какому пути выполнялась программа.

Существуют две взаимодополняющие технологии отладки.

Использование отладчиков — программ, которые включают в себя пользовательский интерфейс для пошагового выполнения программы: оператор за оператором, функция за функцией, с остановками на некоторых строках исходного кода или при достижении определённого условия.

Вывод текущего состояния программы с помощью расположенных в критических точках программы операторов вывода — на экран, принтер, громкоговоритель или в файл. Вывод отладочных сведений в файл называется журналированием.

Количество ошибок в программах заранее неизвестно, поэтому заранее неизвестна продолжительность отладки. Лучшим средством для сокращения отладки являются структурные методы проектирования программ с использованием структурного псевдокода или языков структурного программирования.

Отладка — это часто тяжёлая и утомительная задача. Способности программиста к отладке — это, по-видимому, важнейший фактор в обнаружении источника проблемы, но сложность отладки сильно зависит от используемого языка программирования и инструментов, в частности, отладчиков. Отладчик представляет из себя программный инструмент, позволяющий программисту наблюдать за выполнением исследуемой программы, останавливать и перезапускать её, прогонять в замедленном темпе, изменять значения в памяти и даже, в некоторых случаях, возвращать назад по времени.

Псевдооператоры

Псевдооператоры управляют работой Ассемблера, а не микропроцессо-ра. С помощью псевдооператоров можно определять сегменты и процедуры (т.е.подпрограммы), давать имена командам и элементам данных,резервировать рабочие области памяти и выполнять множество других важных задач.

Таблица 1- Псевдооператоры и директивы

Псевдооператор |

Формат и Функция |

||

1 |

2 |

||

Определения данных DB |

[имя] DB выражение [,…….] определяет переменную или присваивает ячейке памяти начальное значение. Резервирует 1 или более байт (при наличии запятых) |

||

DW |

[имя] DW выражение [,…….] аналогично предыдущему резервирует двухбайтовые слова |

||

DD |

[имя] DD выражение [,…….] Резервирует 4-х байтовые двойные слова |

||

|

|

||

Псевдооператор |

Формат и Функция |

||

1 |

2 |

||

Определения сегмента или процедуры SEGMENT |

Имя_cer SEGMENT [тип_выравнивания (подгонки)] [тип_связи] [‘класс’] . . . . Имя_cer ENDS Определяет границы сегмента программы. Обязательно содержит начало описания Имя_cer SEGMENT и окончание описания Имя_cer ENDS |

||

ASSUME |

ASSUME регистр_cer: Имя_cer [,…….] Или ASSUME регистр_cer: NOTHING Cообщает Ассемблеру, какой регистр сегмента связан с соответствующим сегментом программы. Оператор ASSUME регистр_cer: NOTHING отменяет действие всех предыдущих операторов ASSUME для данного регистра |

||

PROC |

Имя PROC [NEAR] или Имя PROC FAR . . . . . . . . RET имя ENDP Присваивает имя последовательности операторов. Должно иметь начало PROC и окончание ENDP |

||

Управление трансляцией END |

END [метка точки входа] Отмечает конец исходной программы |

||

Внешние ссылки PUBLIC |

PUBLIC идентификатор Делает определенный ранее идентификатордоступным другим модулям программы, которые впоследствии должны быть присоединены к данному модулю |

||

EXTERN |

EXTERN имя: тип [, ….] Указывает, что имя определено в другом модуле программы |

||

INCLUDE |

INCLUDE файл вставляет содержимое указанного файла в текущий файл исходной программы |

||

|

Архитектура микропроцессора 8086 |

|

|

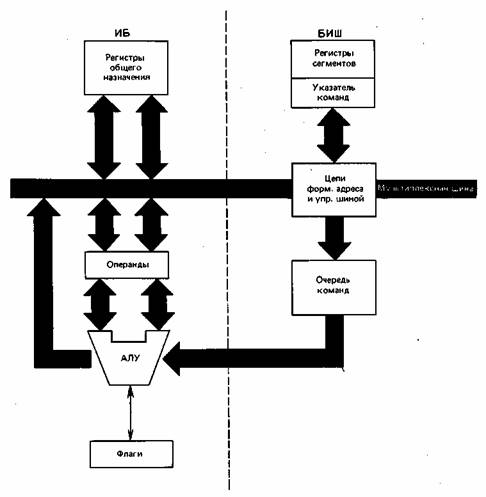

В упрощенном виде последовательность событий, происходящих в микропроцессоре при выполнении какой-либо программы, могла бы быть представлена следующим образом: 1) Выборка очередной команды из памяти. 2) Чтение операнда (если это требуется в соответствии с командой). 3) Исполнение команды. 4) Запись результата (если этого требует исполняемая команда). В рамках ранее существовавших архитектур ЦП эти шаги выполнялись последовательно или с единственным перекрытием цикла выборки шины. Архитектура же процессора 8086 такова, что те же самые шаги распределяются. между различными внутренними блоками обработки данных. При этом исполнение команд возлагается на исполнительный блок (ИБ), а выборку команд, чтение операндов и запись результатов осуществляет блок интерфейса шины (БИШ); это распределение функций отображено на(Рисунок 1). Оба указанных блока работают независимо, и в большинстве случаев происходит интенсивное совмещение операций выборки команд и выполнения очередной команды. И Б исполняет команды, которые уже предварительно выбраны из ОЗУ посредством БИШ, и поэтому общее время выборки команд существенно сокращается. Шестнадцатиразрядное арифметико-логическое устройство (АЛУ), входящее в аппаратные средства И Б, следит за флажками состояния и управляющими флажками ЦП, манипулирует регистрами общего назначения (РОН) и выполняет различные действия над операндами команд. Для быстрого осуществления внутренних пересылок регистры ИБ и линии данных сделаны 16-разрядными. Исполнительный блок не имеет соединения с системной шиной, а адресованные ему команды получает из очереди, обслуживаемой БИШ. Всякий раз, когда некоторая команда требует обращения к памяти или определенному УВВ, исполнительный блок формирует запрос к БИШ на получение или запоминание данных. Хотя при этом ИБ манипулирует только 16-разрядными адресами, БИШ способен выполнять переадресацию и обеспечивать таким образом доступ ИБ ко всему мегабайтному пространству адресов. Все операции взаимодействия с шиной ИБ выполняет при посредничестве БИШ; пересылка данных между ЦП и памятью или внешними устройствами реализуется по требованию ИБ. Тогда, когда ИБ занят выполнением команд, БИШ выбирает из памяти очередные команды и помещает их во внутреннее ЗУПВ, в массив, называемый очередью потока команд. Микропроцессор 8086 позволяет хранить в такой очереди до 6 байт команд одновременно, благодаря чему в большинстве случаев БИШ обеспечивает загрузку ИБ предварительно выбранными командами без занятия системной шины. Почти в любых обстоятельствах очередь потока команд содержит хотя бы один командный байт, и поэтому ИБ не простаивает в ожидании выборки очередной команды из памяти. Очередь образуется из команд, которые в ЗУ непосредственно примыкают к исполняемой в данный момент, т.е. располагаются в ячейках с большими адресами. Если вычислительный процесс протекает последовательно, команды соответствуют логике работы программы. При появлении команды передачи управления в другую ячейку БИШ формирует очередь заново после пересылки ИБ новой команды. В ИБ имеется восемь 16-разрядных регистров, объединенных в две группы по четыре регистра в каждой. Первую группу составляют регистры данных (Н и L), а вторую - регистры указателей и индексные (Р и I). Любой регистр данных может использоваться как два 8-разрядных регистра или один 16-разрядный. Все остальные регистры ЦП всегда рассматриваются как 16-разрядные устройства. Регистров указателей два: указатель стека (УС), содержащий текущий адрес стека, и указатель базы (УБ), который обычно используется при обращении процессора 8086 к памяти. Пара индексных регистров индекс - регистр источника (ИИ) и индекс-регистр результата (ИР)] участвуют в операциях индексной адресации. Все перечисленные восемь регистров могут использоваться как единый блок, называемый накопительным регистром или аккумулятором. БИШ содержит четыре 16-разрядных регистра адреса сегмента и один 16-разрядный указатель команд (УК), аналогичный счетчику команд в микропроцессорах 8080 и 8085. Все пространство памяти микропроцессора 8086 емкостью 1М байт разделено на сегменты по 64К байт. Обеспечивается прямой доступ ЦП сразу к четырем таким сегментам, базовые адреса которых содержатся в регистрах адреса сегмента (PC). Первый из сегментных регистров называется регистром программного сегмента (ПС). Он указывает на текущий сегмент программ, из которого производится выборка команд. Действительный адрес команды в памяти вычисляется путем сложения содержимого регистра ПС с содержимым УК. Второй регистр - регистр стекового сегмента (СС) определяет текущий стековый сегмент, в котором должны выполняться операции над стеком. Действительный адрес стека получается прибавлением содержимого регистра СС к содержимому УС исполнительного блока. Третий регистр - регистр информационного сегмента (ИС) указывает сегмент памяти, в котором в данный момент хранятся переменные выполняемой программы. Наконец, регистром добавочного сегмента (ДС) указывается текущий дополнительный сегмент памяти (четвертый блок емкостью 64К), в котором обычно хранятся данные. Все сегментные регистры доступны для программ и могут участвовать в их выполнении.

Рисунок 1-Структура МП i8086 |