- •1.Основные определения?

- •2.Структура микропроцессорных систем управления?

- •3.Структура микропроцессорного контроллера?

- •6.Режимы работы микропроцессорной системы?

- •Программный обмен информацией:

- •Обмен с использованием прерываний:

- •Режим прямого доступа к памяти:

- •7.Типы микропроцессорных систем?

- •8.Шины мпс?

- •9.Циклы программного обмена?

- •2)Цикл записи.

- •10.Циклы обмена по прерыванием?

- •11.Циклы обмена в режиме пдп?

- •12.Архитектура пк?

- •13.Функции устройств магистрали?

- •19.Команды пересылки данных?

- •20.Арифметические команды?

- •21.Логические команды?

- •22.Команды циклического сдвига?

- •23.Команды передачи управления?

- •24.Команды обращения к стеку?

- •25.Команды обслуживания?

- •26.Структура микропроцессора?

- •27.Алгорифм функционирования микропроцессора?

- •28.Архитектура однокристального микропроцессора k580bm80a?

- •29.Интерфейс мпс (определение, типы, решаемые задачи)?

- •30.Интерфейс с изолированными шинами ?

- •31.Интерфейс с совмещенными адресными шинами?

- •32.Структурная схема интерфейса?

- •33.Интерфейс клавиатуры?

- •34.Интерфейс многоразрядного индикатора?

- •35.Интерфейс модуля памяти?

- •1 Интерфейс модуля памяти с несколькими микросхемами пзу.

- •2 Интерфейс модуля памяти с озу и пзу.

- •37.Процессорное ядро мк?

- •1 Способ

- •2 Способ

- •38.Память программ и внешняя память мк?

- •39.Память данных мк. Регистры мк. Стек мк?

- •40.Основные режимы работы мк?

- •41.Аппратные средства обеспечения надежной работы мк?

- •42. Модули последовательного ввода/вывода мк?

- •43.Модули аналогового ввода/вывода мк?

- •44.Состав и назначение семейств pic – контроллеров?

- •45.Основные характеристики мк подгруппы pic16f8x?

- •46.Структурная схема мк подгруппы pic16f8x?

- •47.Организация памяти pic – контроллеров?

- •48. Способы адресации и организация прерываний в pic – контроллерах?

- •49. Специальные функции мк серии pic?

- •50. Система команд мк подгруппы pic 16f8x?

27.Алгорифм функционирования микропроцессора?

Работа МП начинается с момента его начальной установки которая обеспечивается через ШУ управляющего сигнала сброс поэтому сигнал в счетчик команд записывается в адрес ячейки памяти которая выставляет на ША системы.

Для выполнения 1-ой команды содержащей в младшей ячейки памяти МП через ШУ посылает сигнал чтения и код команды через ШД поступает в регистр команд.

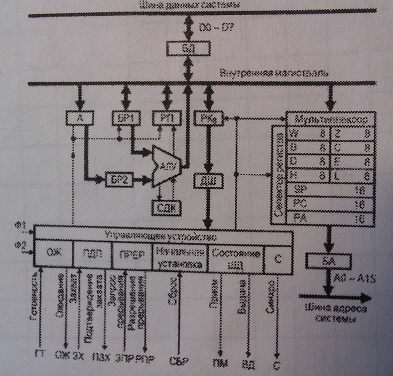

28.Архитектура однокристального микропроцессора k580bm80a?

Операционная часть МП построена на базе 8-и разрядного АЛУ с входам которого подключены буферы регистры.

Второй буфер регистр (БР2) выполняет функцию регистра накопителя.

Регистры w и z программно недоступны и предназначены для хранения некоторых данных при выполнении операции.

Указатель стека и счетчик команд являются 16-разрядными регистрами и предназначены для хранения адресов ячеек памяти при обращении к памяти в качестве адреса могут использоваться содержимое любой регистровой пары блока регистров общего назначения.

Содержимое счетчика команд инфильтрируется после выбора содержимого любой ячейки памяти с формулируемой счетчика команд адреса очередной разрядности регистр адреса и выдается на ША через буфер адреса. Результаты выполняемой операции сохраняется в аккумуляторе и только через него возможен обмен данных с внеш. устройствами.

Регистр признаков предназначен для хранения флагов результатов операции выполняемой в АЛУ.

Управляемая часть МП содержится 8-ми разрядный регистр команд дешифратор команд и управления устр-во.

Управляющее устр-во вырабатывает 3 группы сигналов для реализации работы и режимов МП режим начальной установки ожидание прямого доступа и прерывание.

Сигналом, определяющим состояние ШД относятся:

С выходом сигнала высокого уровня стажирующий на ШД слово состояние.

МП-выходных сигналов высокого уровня подтверждает готовность МП к приему данных.

ВЮ. Выходной сигнал низкого уровня сообщает о том что МП выдал инфу на ШД

К сигналам, определяющим рабочий цикл МП относится:

ГТ - входной сигнал высокого уровня сообщает МП о готовности Вн устр-вами к обмену данных.

ОМ. Выходной сигнал высокого уровня подтверждает переход МП в режим ожидания.

ВХ входной сигнал высокого уровня обеспечивает процесс отслеживать ПМ от ШД.

ПЗХ-выходной сигнал высокого уровня подтверждает отключение МП от ШД.

СБР - выходной сигнал низкого уровня обеспечивает начальную установку МП

К сигналам управления прерывания МП относится:

ЗПР-выходной сигнал высокого уровня запрещающий чтение кода операции очередной команды выполняемой программы и подготавливающий МП к выполнению программы обработки прерывания.

РПР- выходной сигнал высокого уровня подтверждает переход МП в режим прерывания.

29.Интерфейс мпс (определение, типы, решаемые задачи)?

Интерфейс - унифицированное средство объединение различных устройств в единую систему.

Интерфейс выполняет 2 задачи

В своей аппаратной части интерфейс должен обеспечить электронное соединение различных Вн устройств с различными электрическими и конструктивными параметрами, а также с ед. системой шин контроллеров при этом учитывается следующие параметры. Кол-во линий связи, уровни, мощность эл сигналов, длина и помеха защищенность линии связи.

Интерфейс должен обеспечит гибкое программное управление всеми подключенными вн.устрйствами.

По назначению:

Внутренние и внешние

Внутренние объединяет большие интегральные микросхемы средством управления в/вв. модули памяти.

Внешние обеспечивает соединение шин МК с ВН устройствами.