- •Архитектура простой микро – эвм, структура простейшей памяти, состав команд.

- •Структура элементарного микропроцессора.

- •Функционирование микро – эвм: выполнение операции сложения.

- •Функционирование микро – эвм: действия на требования прерывания внешнего устройства.

- •Функционирование микро – эвм: использование регистра адреса/данных.

- •Функционирование микро – эвм: использование указателя стека.

- •И нтерфейс с озу.

- •Основные элементы интерфейса портов ввода/вывода.

- •Интерфейс с реальными портами ввода/вывода.

- •Синхронизация прерыванием передачи данных в устройства ввода/вывода.

- •Шины. Основные понятия.

- •Синхронизация шины.

- •Арбитраж шины.

- •Разновидности шин.

- •Разновидности озу.

- •Типы динамической памяти (fpm, edo, bedo, sdram)

- •Разновидности пзу(Постоянная память—rom, from, eprom).

- •Принципы кэширования.

- •Кэширование в процессорах старших поколений.

- •Архитектура микропроцессора intel 8086.

- •Микропроцессор intel 8086: регистры общего назначения, указатель команд, регистр флагов.

- •Внутренние регистры Регистры данных

- •Регистры сегментов

- •Регистры указателей и индексов

- •Указатель команд

- •Сегментация памяти в процессорах intel 8086.

- •Адресация

- •Способы адресации.

- •Режимы для указания адресов переходов.

- •Адресация портов ввода-вывода.

- •Принципы ввода/вывода, ввод/вывод по прерываниям.

- •Блоковые передачи и прямой доступ к памяти.

- •Регистры сегментов. Шесть 16-разрядных регистров содержат значения селекторов сегментов, которые указывают на текущие адресуемые сегменты памяти. Ниже перечислены эти регистры.

- •Режимы работы 32-разрядных процессоров семейства intel.

- •Основные понятия защищенного режима работы.

- •Основные понятия защищенного режима

- •Селекторы и дескрипторы.

- •Многозадачность. Переключение задач.

- •Страничное управление памятью в процессорах Pentium.

- •Страничное управление памятью в процессорах p6.

- •Режим виртуального 8086 (v86 и ev86).

- •Распределение памяти пк.

- •Стандартная память. Верхняя память (uma). Дополнительная память. Стандартная память — Conventional Memory

- •Верхняя память - uma

- •Дополнительная память — Extended и Expanded Memory

- •Основные характеристики озу.

- •Достоверность хранения данных.

- •Процессоры intel 486: пакетный режим передачи данных.

- •Процессоры intel 486: буферы отложенной записи.

- •Процессоры пятого поколения фирмы intel. Основные отличия по сравнению с предыдущими поколениями.

- •Процессоры Pentium

- •Технология mmx. Технология 3dnow!

- •Процессоры 6-го поколения фирмы intel. Основные особенности. Двойная независимая шина.

- •Обзор процессоров шестого поколения

- •Двойная независимая шина

- •Архитектурные принципы построения процессоров.

- •1.Технология cisc

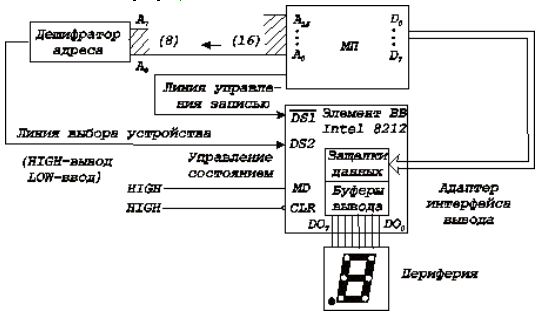

Интерфейс с реальными портами ввода/вывода.

Разработчики выпускают порты ВВ в виде ИС. Тому пример — 8-разрядный элемент ВВ Intel 8212. Интегральная схема Intel 8212 может быть использована как адаптер порта ввода или вывода.

На рис.32 приведен МП, подобный типовому, имеющий интерфейсом с семисегментным индикатором элемент Intel 8212. Этот индикатор является периферией. На схеме МП имеет изолированный ВВ. Отметим, что в этом случае выходная линия выбора устройства полностью декодируется по восьми адресным линиям младших разрядов (A0-A7). Имеется также выход управления записью (при изолированном ВВ можно только использовать команды IN и OUT).

На

рис.32 ИС 8212 используется в порте вывода,

что можно установить, заметив, что на

входе управления состоянием MD

установлен

Н-уровень. Линии шины данных подсоединены

к восьми входным линиям DI0-DI7

элемента ВВ 8212, чьи выходные линии

DO0-DO7

подсоединены к входам индикатора.

Элемент Intel

8212 имеет восемь защелок данных и выходные

буферы. Два входа выбора

![]() ,

DS2

являются

управляющими для элемента 8212, используемого

в рассматриваемом способе ВВ. Когда

активизируется

L-сигналом,

а DS2—Н-сигналом,

данные, поступающие с шины захватятся

з

,

DS2

являются

управляющими для элемента 8212, используемого

в рассматриваемом способе ВВ. Когда

активизируется

L-сигналом,

а DS2—Н-сигналом,

данные, поступающие с шины захватятся

з ащелками

данных и появятся на выходных выводах

DO0-DO7,

активизируя сегменты индикатора.

ащелками

данных и появятся на выходных выводах

DO0-DO7,

активизируя сегменты индикатора.

На рис.33 приведена временная диаграмма работы порта Intel 8212 в состоянии вывода. Отметим, что как только активизируются входы сигналов управления и DS2, выходные данные захватываются в порте ВВ и располагаются на выходных выводах. В состоянии вывода выходные буферы постоянно разрешены, следовательно, захваченные данные появляются даже после того, как линии управления и DS2 возвращаются в состояние сброса.

Синхронизация прерыванием передачи данных в устройства ввода/вывода.

До сих пор предполагалось, что когда программа указывала МП ввести данные в порт, они уже имелись в наличии и, были расположены в строго определенном месте. Однако не всегда это так, потому что периферия (например, клавишное устройство) имеет различное с МП быстродействие. В этом случае имеется несколько способов решения проблемы. К ним относятся методы опросов и прерываний. Опрос называется еще программируемым ВВ. Это наиболее простой метод синхронизации, и используется он в небольших специализированных устройствах. Основной идеей опроса является ввести и (или) вывести данные последовательно, используя в программе цикл опроса.

Предположим очень простую систему с одним только коммутатором, на входе и единственным индикатором на выходе. Можно было бы предусмотреть предельно простой цикл опроса, в котором сначала считывалось бы состояние коммутатора, и затем оно записывалось бы в выходной индикатор. В таком случае МП опрашивал бы вход и. одновременно воздействовал на выход через каждые несколько микросекунд.

В более общем случае в цикле можно опрашивать одно или несколько УВВ. Микропроцессор опрашивает первое устройство — нужно ли ему обслуживание, и если да, устанавливает индикатор состояния, т.е. устройство получает требуемое обслуживание. В противном случае (индикатор состояния не устанавливается) МП продолжает опрос.

Представленная на рис.34 система снабжена линией требования прерывания, чтобы дать знать МП о готовности данных для передачи в ЦП. Вспомним, что типовой МП имеет только один ввод требования прерывания (INTR). Активизированный Н-сигналом МП выполняет текущую команду, передает на хранение в стек содержимое аккумулятора, регистра и счетчика команд и ветвится в подпрограмму обслуживания прерывания. Затем МП возвращается в основную программу. В рассматриваемом примере подпрограмма обслуживания прерывания могла бы быть простой, вводящей и помещающей данные, поступающие с клавишного устройства.

Прерывание информирует МП о том, что УВВ готово и надо действовать. Реализует эту операцию специальная подпрограмма обслуживания прерывания. Если несколько устройств вызывают прерывание МП, линии вызова прерывания подвергаются операциям ИЛИ, и МП в таком случае необходимо определить ответственное за прерывание УВВ. Этот процесс выбора относится к способу опроса и составляет схему опроса-прерывания, В таком случае каждому порту ВВ соответствует одно состояние, код которого указывает МП — готов ли порт ввести или вывести данные.

Существуют МП, снабженные несколькими входами прерывания и командами признания или непризнания по крайней мере некоторого числа этих входов. Многие МП снабжены векторным прерыванием, когда МП знает устройство, вызвавшее прерывание, и ветвится на подпрограмму обслуживания соответствующего прерывания. Многие МП снабжены также устройствами определения приоритета обслуживания (аппаратно или программно) в случае двух одновременных прерываний (арбитраж приоритета прерывания). Эта система решает, согласиться ли с приоритетом обслуживания одного из прерываний, она обычно содержится в специальной ИС (например, устройство Intel 8259).

Преимущество опроса над процедурой прерывания состоит в том, что первый требует меньше аппаратных средств и, находясь под программным контролем, является синхронным. Недостатком является потребность в очень развитых программах, занимающих время МП в случае большого числа устройств опроса, и необходимость довольно значительного промежутка времени для ответа на один запрос.

Преимуществом прерывания над опросом является быстродействие ответа, лучшее использование МП и потребность во много раз меньших программных средств. Недостаток состоит в том, что функционирование МП асинхронно и требует сложного аппаратного интерфейса.