- •Архитектура простой микро – эвм, структура простейшей памяти, состав команд.

- •Структура элементарного микропроцессора.

- •Функционирование микро – эвм: выполнение операции сложения.

- •Функционирование микро – эвм: действия на требования прерывания внешнего устройства.

- •Функционирование микро – эвм: использование регистра адреса/данных.

- •Функционирование микро – эвм: использование указателя стека.

- •И нтерфейс с озу.

- •Основные элементы интерфейса портов ввода/вывода.

- •Интерфейс с реальными портами ввода/вывода.

- •Синхронизация прерыванием передачи данных в устройства ввода/вывода.

- •Шины. Основные понятия.

- •Синхронизация шины.

- •Арбитраж шины.

- •Разновидности шин.

- •Разновидности озу.

- •Типы динамической памяти (fpm, edo, bedo, sdram)

- •Разновидности пзу(Постоянная память—rom, from, eprom).

- •Принципы кэширования.

- •Кэширование в процессорах старших поколений.

- •Архитектура микропроцессора intel 8086.

- •Микропроцессор intel 8086: регистры общего назначения, указатель команд, регистр флагов.

- •Внутренние регистры Регистры данных

- •Регистры сегментов

- •Регистры указателей и индексов

- •Указатель команд

- •Сегментация памяти в процессорах intel 8086.

- •Адресация

- •Способы адресации.

- •Режимы для указания адресов переходов.

- •Адресация портов ввода-вывода.

- •Принципы ввода/вывода, ввод/вывод по прерываниям.

- •Блоковые передачи и прямой доступ к памяти.

- •Регистры сегментов. Шесть 16-разрядных регистров содержат значения селекторов сегментов, которые указывают на текущие адресуемые сегменты памяти. Ниже перечислены эти регистры.

- •Режимы работы 32-разрядных процессоров семейства intel.

- •Основные понятия защищенного режима работы.

- •Основные понятия защищенного режима

- •Селекторы и дескрипторы.

- •Многозадачность. Переключение задач.

- •Страничное управление памятью в процессорах Pentium.

- •Страничное управление памятью в процессорах p6.

- •Режим виртуального 8086 (v86 и ev86).

- •Распределение памяти пк.

- •Стандартная память. Верхняя память (uma). Дополнительная память. Стандартная память — Conventional Memory

- •Верхняя память - uma

- •Дополнительная память — Extended и Expanded Memory

- •Основные характеристики озу.

- •Достоверность хранения данных.

- •Процессоры intel 486: пакетный режим передачи данных.

- •Процессоры intel 486: буферы отложенной записи.

- •Процессоры пятого поколения фирмы intel. Основные отличия по сравнению с предыдущими поколениями.

- •Процессоры Pentium

- •Технология mmx. Технология 3dnow!

- •Процессоры 6-го поколения фирмы intel. Основные особенности. Двойная независимая шина.

- •Обзор процессоров шестого поколения

- •Двойная независимая шина

- •Архитектурные принципы построения процессоров.

- •1.Технология cisc

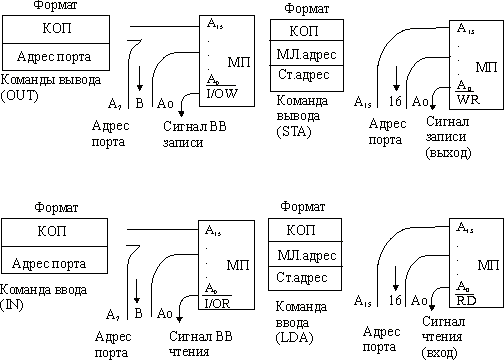

Основные элементы интерфейса портов ввода/вывода.

Операция ввода или вывода включает в себя передачу данных из (или) требуемой периферии. Микропроцессор является ядром всех операций. Ввод соответствует потоку данных в МП, вывод—из МП. Ячейки, куда данные входят или выходят, называются обычно портами ввода или вывода.

М П

использует команды IN

или OUT

для передачи данных посредством портов

ВВ. Реализация этих команд показана на

рис.29.

Мнемониками являются IN

и OUT

для вводов и выводов соответственно.

Рис.29 дает форматы и КОП этих команд,

которые соответствуют номеру периферии

или адресу порта. Адрес порта (1 байт)

позволяет выбрать один из 256 (28)

портов и адрес передается восемью

адресными линиями младших разрядов

(A0-A7).

П

использует команды IN

или OUT

для передачи данных посредством портов

ВВ. Реализация этих команд показана на

рис.29.

Мнемониками являются IN

и OUT

для вводов и выводов соответственно.

Рис.29 дает форматы и КОП этих команд,

которые соответствуют номеру периферии

или адресу порта. Адрес порта (1 байт)

позволяет выбрать один из 256 (28)

портов и адрес передается восемью

адресными линиями младших разрядов

(A0-A7).

На

рис.29 представлены также два дополнительных

выхода сигналов управления. При операции

OUT

используется особый сигнал ВВ

Запись, т.е.![]() .

В случае операции IN—BB

считывание,

т.е.

.

В случае операции IN—BB

считывание,

т.е.![]() .

Это два L-активных сигнала. Использование

специального управления, такого, как

и

,

соответствует изолированному

ВВ

или вводу/выводу

через аккумулятор.

.

Это два L-активных сигнала. Использование

специального управления, такого, как

и

,

соответствует изолированному

ВВ

или вводу/выводу

через аккумулятор.

Передача данных, выполняемая на основе команд IN и OUT, классифицируется как программно-контролируемый ВВ, т.е. ею управляют команды программы. Передача данных может быть вызвана периферией, выдающей сообщение типа «Я готова выдать (или принять) данные». Чтобы вовлечь МП, периферия использует прерывания (вспомним, что когда МП получает запрос на прерывание, он завершает выполнение текущей команды, затем ветвится на подпрограмму обслуживания прерывания, эта подпрограмма может содержать или не содержать операции ВВ).

Программно-управляемый ВВ может быть выполнен двумя способами: первый — изолированный ВВ (рис.29) выполняется посредством команд IN и OUT; по второму — положение входов и выходов определяется как адреса обычной памяти. Второй способ ВВ реализуется по принципу доступа в память, и тогда используются обычные команды. Обратимся к рис.29, где используют команду прямого размещения содержимого аккумулятора STA при выводе данных в порт вывода; на том же рисунке тот же тип команды использован затем и для ввода данных (команда LDA). Мы видим здесь, что адресные линии должны быть декодированы и служат для выбора адреса порта ввода или порта вывода.

Используются также обычные сигналы управления и . Т.о., для ввода и вывода данных по принципу доступа в память могут быть использованы все команды обращения.

Последний способ, очевидно, наиболее распространен и может быть применим в любом МП. Метод изолированного ВВ применим только в МП, снабженных как командами IN и OUT, так и специальными выводами управления ВВ при записи и считывании.

Обычно под выводом подразумевают вывод на периферию. Однако на практике выводы попадают не сразу на периферию, а в устройство памяти, где помещаются данные для периферии.

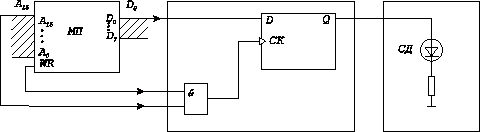

На рис.30 введены адаптеры интерфейса ввода и вывода, которые являются устройствами памяти, и которые обладают всеми их свойствами.

Н а

рис.30 изображен интерфейс МП с периферией.

Отметим, что в качестве индикатора

выхода здесь стоит фотодиод, а адаптер

интерфейса вывода содержит D-триггер.

Предположим, что МП выполняет команду

прямого размещения содержимого

аккумулятора (A)

=0000 0001. Если предположить также адрес

8000Н, то линия A15

будет

находиться в Н-активном состоянии и

активизирует нижний вход элемента И.

Некоторое время спустя Н-активный сигнал

появляется на линии D0

шины данных. Сигнал управления записью

переходит

к L-уровню

и активизирует элемент И, который

запирает 1 в D-триггере.

На выходе D-триггера

Н-сигналом зажигается фотодиод (или

индикатор бита). В качестве примера на

рис.30 показан процесс индикации

единственного бита данных.

а

рис.30 изображен интерфейс МП с периферией.

Отметим, что в качестве индикатора

выхода здесь стоит фотодиод, а адаптер

интерфейса вывода содержит D-триггер.

Предположим, что МП выполняет команду

прямого размещения содержимого

аккумулятора (A)

=0000 0001. Если предположить также адрес

8000Н, то линия A15

будет

находиться в Н-активном состоянии и

активизирует нижний вход элемента И.

Некоторое время спустя Н-активный сигнал

появляется на линии D0

шины данных. Сигнал управления записью

переходит

к L-уровню

и активизирует элемент И, который

запирает 1 в D-триггере.

На выходе D-триггера

Н-сигналом зажигается фотодиод (или

индикатор бита). В качестве примера на

рис.30 показан процесс индикации

единственного бита данных.

На рис.31 используется способ ВВ по принципу доступа в память. Обычно несколько адресных линий декодируются одним адресным дешифратором для того, чтобы активизировать линию выбора устройства. На рис.31 приведена расширенная система ввода одного отдельного бита. Здесь параллельные данные объемом 8 бит вводятся с клавишного устройства. Управление считыванием и простая адресация те же, что и в предыдущем примере.

О рганизация

ВВ по принципу

доступа в память

используется очень распространенными

микропроцессорами, такими, как Motorola

6800 и МОП-технологии 6502. Изолированный

ВВ

(иногда называемый канальным ВВ данных)

используется таким семейством

микропроцессоров, как Intel

8080/8085 и Zilog

80.

рганизация

ВВ по принципу

доступа в память

используется очень распространенными

микропроцессорами, такими, как Motorola

6800 и МОП-технологии 6502. Изолированный

ВВ

(иногда называемый канальным ВВ данных)

используется таким семейством

микропроцессоров, как Intel

8080/8085 и Zilog

80.