- •Архитектура простой микро – эвм, структура простейшей памяти, состав команд.

- •Структура элементарного микропроцессора.

- •Функционирование микро – эвм: выполнение операции сложения.

- •Функционирование микро – эвм: действия на требования прерывания внешнего устройства.

- •Функционирование микро – эвм: использование регистра адреса/данных.

- •Функционирование микро – эвм: использование указателя стека.

- •И нтерфейс с озу.

- •Основные элементы интерфейса портов ввода/вывода.

- •Интерфейс с реальными портами ввода/вывода.

- •Синхронизация прерыванием передачи данных в устройства ввода/вывода.

- •Шины. Основные понятия.

- •Синхронизация шины.

- •Арбитраж шины.

- •Разновидности шин.

- •Разновидности озу.

- •Типы динамической памяти (fpm, edo, bedo, sdram)

- •Разновидности пзу(Постоянная память—rom, from, eprom).

- •Принципы кэширования.

- •Кэширование в процессорах старших поколений.

- •Архитектура микропроцессора intel 8086.

- •Микропроцессор intel 8086: регистры общего назначения, указатель команд, регистр флагов.

- •Внутренние регистры Регистры данных

- •Регистры сегментов

- •Регистры указателей и индексов

- •Указатель команд

- •Сегментация памяти в процессорах intel 8086.

- •Адресация

- •Способы адресации.

- •Режимы для указания адресов переходов.

- •Адресация портов ввода-вывода.

- •Принципы ввода/вывода, ввод/вывод по прерываниям.

- •Блоковые передачи и прямой доступ к памяти.

- •Регистры сегментов. Шесть 16-разрядных регистров содержат значения селекторов сегментов, которые указывают на текущие адресуемые сегменты памяти. Ниже перечислены эти регистры.

- •Режимы работы 32-разрядных процессоров семейства intel.

- •Основные понятия защищенного режима работы.

- •Основные понятия защищенного режима

- •Селекторы и дескрипторы.

- •Многозадачность. Переключение задач.

- •Страничное управление памятью в процессорах Pentium.

- •Страничное управление памятью в процессорах p6.

- •Режим виртуального 8086 (v86 и ev86).

- •Распределение памяти пк.

- •Стандартная память. Верхняя память (uma). Дополнительная память. Стандартная память — Conventional Memory

- •Верхняя память - uma

- •Дополнительная память — Extended и Expanded Memory

- •Основные характеристики озу.

- •Достоверность хранения данных.

- •Процессоры intel 486: пакетный режим передачи данных.

- •Процессоры intel 486: буферы отложенной записи.

- •Процессоры пятого поколения фирмы intel. Основные отличия по сравнению с предыдущими поколениями.

- •Процессоры Pentium

- •Технология mmx. Технология 3dnow!

- •Процессоры 6-го поколения фирмы intel. Основные особенности. Двойная независимая шина.

- •Обзор процессоров шестого поколения

- •Двойная независимая шина

- •Архитектурные принципы построения процессоров.

- •1.Технология cisc

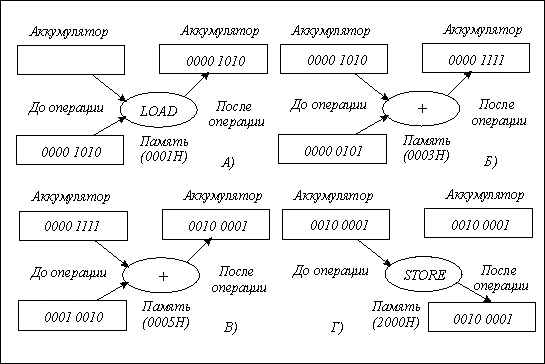

Функционирование микро – эвм: выполнение операции сложения.

Пусть требуется выполнить простую операцию сложения трех чисел, например 10+5+18=3310. Короткая и простая микропрограмма выполнения этой операции могла бы быть записана в следующей последовательности.

Команда 1: загрузить (LOAD) первое число (1010) в ЦП.

Команда 2: сложить (ADD) второе число (510) с первым.

Команда 3 сложить (ADD) третье число (1810) с двумя предыдущими.

Команда 4: поместить (STORE) сумму (3310) в ячейку памяти 2000Н.

После загрузки в память программы эти команды могли бы извлекаться из нее как команды памяти, показанной на рис.9. Заметим, что первая команда программы начинается с адреса 0000Н. Эта команда (LOAD число 0AН) использует 2 байт памяти. Первый байт памяти содержит оперативную часть команды, другой — операнд. Код операции LOAD для микропроцессора, используемого в этом примере, будет 86Н (1000 01102). Операнд 0AН (0000 10102) является первым числом, подлежащим загрузке в аккумулятор микропроцессора.

Предположим, что программа размещена в блоке ОЗУ микро-ЭВМ. В таком случае рис.10 иллюстрирует каждую операцию программы (LOAD, ADD, ADD, STORE).

О перация

загрузки (LOAD) первой команды подробно

приведена на рис.10, и показывает, что

содержимое ячейки памяти 0001Н загружено

в аккумулятор, который содержит после

этого 0000 10102

—первое слагаемое число. В результате

операции загрузки стирается предыдущее

и записывается новое содержимое

аккумулятора. Вторая команда, операция

ADD,

детализирована на рис.10. Содержимое

ячейки памяти 0003Н (0000 01012)

складывается с содержимым аккумулятора

0000 10102,

что дает сумму 0000 11П2,

помещаемую в аккумулятор, и мы можем

заметить, что содержимое аккумулятора

изменяется при операции ADD.

перация

загрузки (LOAD) первой команды подробно

приведена на рис.10, и показывает, что

содержимое ячейки памяти 0001Н загружено

в аккумулятор, который содержит после

этого 0000 10102

—первое слагаемое число. В результате

операции загрузки стирается предыдущее

и записывается новое содержимое

аккумулятора. Вторая команда, операция

ADD,

детализирована на рис.10. Содержимое

ячейки памяти 0003Н (0000 01012)

складывается с содержимым аккумулятора

0000 10102,

что дает сумму 0000 11П2,

помещаемую в аккумулятор, и мы можем

заметить, что содержимое аккумулятора

изменяется при операции ADD.

На рис.10 показана вторая операция ADD (команда 3); содержимое аккумулятора — сумма 0000 11112 сложена с содержимым ячейки памяти 0005Н, т. е. выполняется операция 0000 1111+0001 0010=0010 0001. Окончательно 0010 0001 появляется в аккумуляторе после второй операции АОО.

Операция STORE (РАЗМЕСТИТЬ) по команде 4 представлена на рис.10. Содержимое аккумулятора (001000012) передано и размещено в ячейке памяти по адресу 2000Н. Заметим, так как это важно, что ячейки памяти данных были идентифицированы в памяти программы двумя раздельными байтами (0007Н и 0008Н). Ячейка памяти программы 0006Н содержит КОП B7Н прямой команды STORE (см. рис.9).

Рассмотрим извлечение, декодирование и выполнение команды LOAD по адресам 000H и 0001H в программе. Рис.11 иллюстрирует процедуру выполнения центральным процессором этой специальной операции.

Рассмотрим

сверху слева направо последовательность

действий на рис.11: счетчик команд прежде

всего устанавливает адрес первого этапа

программы. После этого 16-разрядный адрес

передается в адресный регистр, затем

на адресную шину и в память программы.

Для активизации памяти программы ЦП

выдает сигнал считывания программы (1

на линии R/![]() ),

в то время как дешифратор адресов

(который не входит в состав ЦП) активизирует

выбор кристалла

),

в то время как дешифратор адресов

(который не входит в состав ЦП) активизирует

выбор кристалла

![]() нулем. Затем счетчик команд инкрементируется

до 0001H,

ячейка памяти программы 0000H

становится доступной и ее содержимое

считывается на шину данных. Код операции

(86H)

команды LOAD

передается в регистр ЦП. Этап извлечения

КОП команды LOAD

завершен.

нулем. Затем счетчик команд инкрементируется

до 0001H,

ячейка памяти программы 0000H

становится доступной и ее содержимое

считывается на шину данных. Код операции

(86H)

команды LOAD

передается в регистр ЦП. Этап извлечения

КОП команды LOAD

завершен.

Затем КОП (86H), содержащийся в регистре команды ЦП, интерпретируется дешифратором команд. В данном случае ЦП определяет, идет ли речь о команде LOAD непосредственно, что означает загрузку им содержимого памяти, адрес которой следует непосредственно за КОП, в аккумулятор. Содержимое счетчика команд (0001H) передается в адресный регистр, на адресную шину и в память. ЦП выдает импульс HIGH считывания на вход R/ памяти. Импульс LOW поступает на вход памяти, что активизирует память. В третьей строке (снизу) на рис.10 счетчик команд инкрементируется до 0002H, что подготавливает его к извлечению последующей команды. Ячейка памяти 0001H становится доступной, и ее содержимое (0AH) поступает на шину данных, затем передается в аккумулятор. В ходе этапа извлечения КОП всегда помещается в регистр команд.