- •Архитектура простой микро – эвм, структура простейшей памяти, состав команд.

- •Структура элементарного микропроцессора.

- •Функционирование микро – эвм: выполнение операции сложения.

- •Функционирование микро – эвм: действия на требования прерывания внешнего устройства.

- •Функционирование микро – эвм: использование регистра адреса/данных.

- •Функционирование микро – эвм: использование указателя стека.

- •И нтерфейс с озу.

- •Основные элементы интерфейса портов ввода/вывода.

- •Интерфейс с реальными портами ввода/вывода.

- •Синхронизация прерыванием передачи данных в устройства ввода/вывода.

- •Шины. Основные понятия.

- •Синхронизация шины.

- •Арбитраж шины.

- •Разновидности шин.

- •Разновидности озу.

- •Типы динамической памяти (fpm, edo, bedo, sdram)

- •Разновидности пзу(Постоянная память—rom, from, eprom).

- •Принципы кэширования.

- •Кэширование в процессорах старших поколений.

- •Архитектура микропроцессора intel 8086.

- •Микропроцессор intel 8086: регистры общего назначения, указатель команд, регистр флагов.

- •Внутренние регистры Регистры данных

- •Регистры сегментов

- •Регистры указателей и индексов

- •Указатель команд

- •Сегментация памяти в процессорах intel 8086.

- •Адресация

- •Способы адресации.

- •Режимы для указания адресов переходов.

- •Адресация портов ввода-вывода.

- •Принципы ввода/вывода, ввод/вывод по прерываниям.

- •Блоковые передачи и прямой доступ к памяти.

- •Регистры сегментов. Шесть 16-разрядных регистров содержат значения селекторов сегментов, которые указывают на текущие адресуемые сегменты памяти. Ниже перечислены эти регистры.

- •Режимы работы 32-разрядных процессоров семейства intel.

- •Основные понятия защищенного режима работы.

- •Основные понятия защищенного режима

- •Селекторы и дескрипторы.

- •Многозадачность. Переключение задач.

- •Страничное управление памятью в процессорах Pentium.

- •Страничное управление памятью в процессорах p6.

- •Режим виртуального 8086 (v86 и ev86).

- •Распределение памяти пк.

- •Стандартная память. Верхняя память (uma). Дополнительная память. Стандартная память — Conventional Memory

- •Верхняя память - uma

- •Дополнительная память — Extended и Expanded Memory

- •Основные характеристики озу.

- •Достоверность хранения данных.

- •Процессоры intel 486: пакетный режим передачи данных.

- •Процессоры intel 486: буферы отложенной записи.

- •Процессоры пятого поколения фирмы intel. Основные отличия по сравнению с предыдущими поколениями.

- •Процессоры Pentium

- •Технология mmx. Технология 3dnow!

- •Процессоры 6-го поколения фирмы intel. Основные особенности. Двойная независимая шина.

- •Обзор процессоров шестого поколения

- •Двойная независимая шина

- •Архитектурные принципы построения процессоров.

- •1.Технология cisc

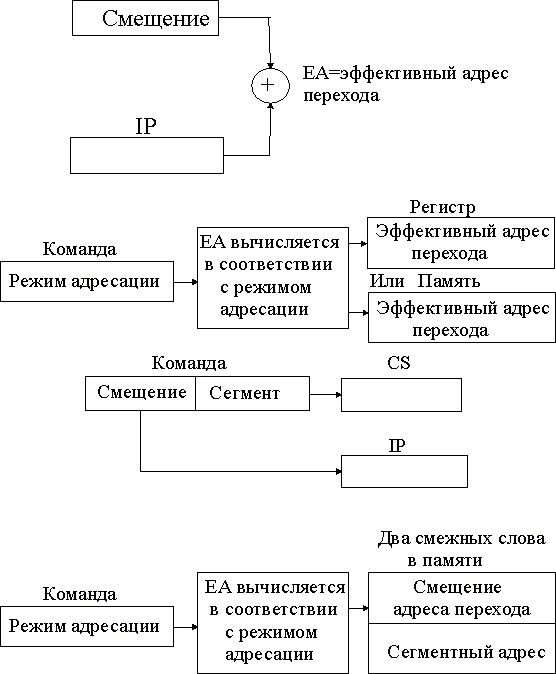

Режимы для указания адресов переходов.

Режимы для указания адресов перехода графически определены на рис.7. Рассмотрим их подробнее.

В нутрисегментный

прямой.

Эффективный адрес перехода равен сумме

8-или 16-битного смещения и текущего

содержимого IP.

Когда смещение имеет длину 8 бит, этот

режим называется коротким переходом.

Внутрисегментную прямую адресацию в

большинстве книг называют относительной

адресацией, так как смещение вычисляется

"относительно'' IP.

Этот режим допустим в условных и

безусловных переходах, но в команде

условного перехода может быть только

смещение длиной 8 бит.

нутрисегментный

прямой.

Эффективный адрес перехода равен сумме

8-или 16-битного смещения и текущего

содержимого IP.

Когда смещение имеет длину 8 бит, этот

режим называется коротким переходом.

Внутрисегментную прямую адресацию в

большинстве книг называют относительной

адресацией, так как смещение вычисляется

"относительно'' IP.

Этот режим допустим в условных и

безусловных переходах, но в команде

условного перехода может быть только

смещение длиной 8 бит.

Внутрисегментный косвенный. Эффективный адрес перехода есть содержимое регистра или ячейки памяти, которые указываются в любом режиме (кроме непосредственного) адресации данных. Содержимое IP заменяется эффективным адресом перехода. Данный режим допустим только в командах безусловного перехода.

Межсегментный прямой. Заменяет содержимое IP одной частью команды, а содержимое CS — другой частью команды. Назначение данного режима адресации - обеспечить переход из одного сегмента кода в другой.

Межсегментный косвенный. Заменяет содержимое IP и CS содержимым двух смежных слов из памяти, которые определяются в любом режиме адресации данных кроме непосредственного и регистрового.

Отметим, что физический адрес перехода равен сумме нового содержимого IP и содержимого CS, умноженного на 1610. Межсегментный переход может быть только безусловным.

Для иллюстрации косвенного перехода с некоторыми режимами адресации данных предположим, что (ВХ) = 1256, (SI) = 528F, смещение = 20A1. Тогда при прямой адресации эффективный адрес перехода равен 20А1 + (DS) * 1610. При регистровой косвенной адресации (с участием регистра ВХ) эффективный адрес перехода 1256 + 20А1 + (DS) * 1610. Наконец, в базовой индексной адресации (с участием регистров ВХ и SI) эффективный адрес перехода 1256 + 528F + (DS) * 1610.

Адресация портов ввода-вывода.

В дополнение к области памяти объемом в 1 Мбайт микропроцессор 8088 может адресоваться к внешним устройствам через 65 536 (64 К) портов ввода-вывода. Он имеет специальные команды ввода-вывода, которые позволяют Вам иметь непосредственный доступ к первым 256 портам (от 0 до 255). Другие команды позволяют Вам получить косвенный доступ к порту с помощью занесения идентифицирующего его номера (от 0 до 65 535) в регистр данных. Подобно ячейкам памяти любой порт может быть 8- или 16-битовым.

Эта область не явл. сегментируемой, может выполняться как отдельно, так и вместе со всей памятью. Во 2-ом случае объем памяти уменьшается, но обеспечивается дополнительная гибкость, т.к. все рассм. виды адресации могут обеспечить доступ к этой области. Каждый байт в обл. в/в м/б назначен в кач-ве адреса однозначно определяемого порта. Регистр AL исп. для передачи байта, а AX для передачи слова при адресации портов в/в. Сущ. команды-in (ввести из порта) и out (вывести в порт). Если номер порта превышает 255, то для его хранения исп. рег. DX

Принципы ввода/вывода, ввод/вывод по прерываниям.

Передачу данных в (из) порт (а) можно осуществить двумя способами. Первый способ — выполнить команду, которая передает один байт или одно слово, второй — выполнить последовательность команд, которая заставляет специальную компоненту, связанную с интерфейсом, передать совокупность байт или слов в (из) указанный (ого) блок (а) ячеек памяти. Второй способ называется блоковой передачей или прямым доступом к памяти (ПДП), а специальная компонента называется контроллером ПДП. Байт или слово передаются между портом и ЦП, а блоковые передачи осуществляются непосредственно в (из) память (и).

Программный ввод-вывод и ввод-вывод по прерываниям опираются на передачи байт и слов; данные от памяти к портам и наоборот передаются через регистр ЦП. Например, если необходимо ввести слово из порта в ячейку памяти, его приходится вначале ввести в регистр ЦП, а затем переслать в ячейку памяти. Чтобы передать блок байт или слов из периферийного устройства в память, программа должна последовательно вводить байты или слова в ЦП, а затем помещать их в смежные ячейки памяти. Эти операции реализуются программным циклом. Блоковым вводом управляют интерфейс и контроллер ПДП так, что каждые байт или слово по мере их появления передаются из порта непосредственно в память. Для инициирования передачи программа должна только выдать необходимые приказы в интерфейс и контроллер. Аналогичным образом интерфейс и его контроллер ПДП могут воспринимать последовательные байты или слова из памяти и передавать их во внешнее устройство.

Возникают два вопроса: как система узнает, когда интерфейс имеет данные или готов принимать данные, и какой интерфейс обслуживать первым, когда одновременно требуют внимания несколько интерфейсов. При программном вводе-выводе программа определяет требующие обслуживания интерфейсы, проверяя биты "готовность" в их регистрах состояния. Программная проверка разрядов или сигналов готовности называется опросом (полингом). При вводе-выводе по прерываниям интерфейс посылает в ЦП внешнее прерывание, когда он имеет данные для ввода или готов воспринимать их, а сама операция ввода-вывода реализуется процедурой прерывания.

В операции ПДП интерфейс запрашивает использование шины, выдавая сигнал по линии управления, и осуществляет необходимую передачу без помощи ЦП.

Когда обслуживания запрашивают несколько интерфейсов, порядок удовлетворения запросов зависит от встроенного в систему механизма приоритетов. Известны несколько способов назначения интерфейсам приоритетов; некоторые из них реализуются программно, другие — аппаратно, а третьи являются комбинацией первых двух. Хотя механизм приоритетов может варьироваться в зависимости от вида ввода-вывода, необходим метод однозначного разрешения возникающих конфликтов.

Хотя программный ввод-вывод оказывается весьма простым, он связан со значительными потерями времени на ожидание активного состояния готовности. Если человек печатает на терминале со скоростью 10 символов в секунду, а для ввода каждого символа компьютеру требуется всего 10 мкс, то примерно

![]() времени

расходуется впустую. Это допустимо,

если в процессе ввода не требуется

выполнять другую обработку, но если эту

обработку задерживать нельзя, приходится

искать другой подход.

времени

расходуется впустую. Это допустимо,

если в процессе ввода не требуется

выполнять другую обработку, но если эту

обработку задерживать нельзя, приходится

искать другой подход.

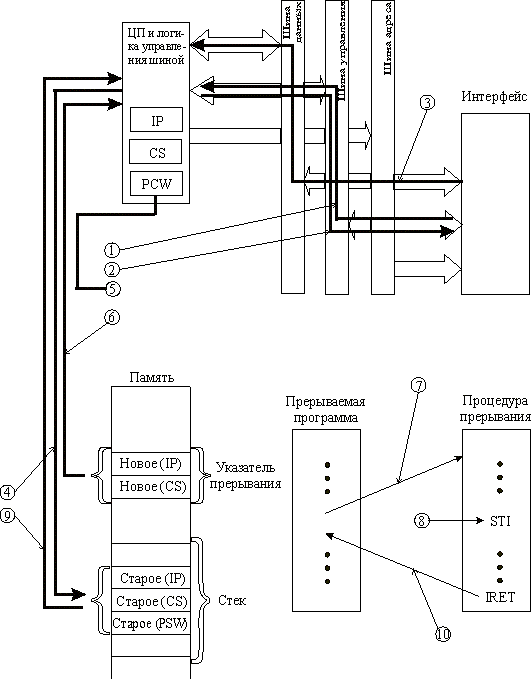

До того как в микропроцессоре 8086 может начаться последовательность прерывания, он должен завершить текущую команду.

После распознавания прерывания микропроцессор 8086 реализует такую последовательность прерывания:

1. Определить тип N.

2. Включить в стек текущее содержимое PSW, CS и IP (именно в таком порядке).

3. Сбросить флажки IF и TF.

4. Передать содержимое ячейки памяти 4*N в IP, а содержимое 4*N + 2 в СS.

Таким образом, прерывание заставляет микропроцессор приостановить "нормальное выполнение программы и перейти к ячейке, адресуемой двойным словом, находящимся по адресу, равному учетверенному типу прерывания (т. е. указателю прерывания). Управление можно возвратить в точку возникновения прерывания командой IRET, находящейся в конце процедуры прерывания.

Ранее

говорилось, что имеются два класса

прерываний: внутренние и внешние. Внешние

прерывания вызывает сигнал, подаваемый

на входы INT и NMI микропроцессора.

Прерывание, инициируемое сигналом на

входе NMI, называется немаскируемым: оно

вызывает прерывание типа 2 независимо

от состояния флажка IP. Сигналы немаскируемых

прерываний обычно формируют схемы,

фиксирующие катастрофические события,

например отказ питания, внешние события

или импульсы таймера, которые должны

обрабатываться немедленно. Прерывание

на входе INT маскируется флажком IF: если

IF = = 0, прерывание не распознается. Когда

IF = 1 и возникает маскируемое прерывание,

ЦП через выход

![]() возвращает в интерфейс устройства

сигнал подтверждения и инициирует

последовательность прерывания. Сигнал

подтверждения заставляет интерфейс

выдать в ЦП (по шине адреса) байт, который

определяет тип прерывания и, следовательно,

адрес указателя прерывания. Указатель,

в свою очередь, дает начальный адрес

процедуры прерывания. Полный процесс

обслуживания прерывания представлен

на рис.9, где номерами обозначены следующие

действия:

возвращает в интерфейс устройства

сигнал подтверждения и инициирует

последовательность прерывания. Сигнал

подтверждения заставляет интерфейс

выдать в ЦП (по шине адреса) байт, который

определяет тип прерывания и, следовательно,

адрес указателя прерывания. Указатель,

в свою очередь, дает начальный адрес

процедуры прерывания. Полный процесс

обслуживания прерывания представлен

на рис.9, где номерами обозначены следующие

действия:

1 —

интерфейс посылает сигнал прерывания;

—

интерфейс посылает сигнал прерывания;

2—после завершения текущей команды возвращается подтверждение;

3— в ЦП передается тип N;

4— текущее содержимое PSW, CS и IP включается в стек;

5— флажки IF и TF сбрасываются;

6— в IP загружается содержимое 4*N, а в CS – содержимое 4*N+2;

7— начинается процедура прерывания;

8— прерывания разрешены;

9— команда IRET осуществляет извлечение из стека IP, CS и PSW;

10 — производится возврат в прерванную программу.

Хотя для интерфейсов в системе на базе микропроцессора 8086 имеются многочисленные типы внешних прерываний и редко требуется назначать интерфейсам один и тот же тип прерывания, это можно сделать и для учета приоритетов применить опрос. Введя в начале процедуры прерывания программу, можно установить приоритеты интерфейсам в том порядке, в котором они опрашиваются программой.

Простым аппаратным решением введения приоритетов является приоритетная цепочка. В каждом интерфейсе предусматривается логическая схема и прохождение сигнала подтверждения через эти схемы показано на рис.10. Более подробно логическая схема приоритетной цепочки представлена на рис.11. Если интерфейс выдал запрос, активный сигнал заставляет выдать в интерфейс активный сигнал подтверждения прерывания, а передача в следующий интерфейс блокируется. Когда же запрос интерфейса отсутствует, сигналу разрешается проходить через схему приоритетной цепочки. Следовательно, по мере прохождения сигнала по цепочке ближайший к ЦП запрашивающий интерфейс "перехватывает" сигнал подтверждения, выдает тип и завершает последовательность прерывания; после обслуживания запрос снимается. Более удаленные по цепочке интерфейсы, сделавшие запросы, не получают сигнала подтверждения и сохраняют свои запросы. После того как команда STI разрешает прерывания или команда IRET восстанавливает PSW с IF = 1, ЦП распознает другие запросы и выдает новый сигнал . К этому времени интерфейс, запрос которого обслуживался, снимает свой запрос и не препятствует прохождению сигнала . Т.о. приоритет интерфейса определяется его положением в цепочке: чем ближе интерфейс к ЦП, тем выше его приоритет.

Более гибкий аппаратно-программный механизм приоритетов реализуется программируемой схемой управления приоритетными прерываниями, которая входит в логику управления шиной. Общий вид такой схемы и место ее в системе показаны на рис.12. Линии INTR и подключаются только к схеме управления, а не к интерфейсам. Линии запросов прерываний от интерфейсов подаются в схему управления и не объединяются. Схема управления содержит логику, необходимую для назначения приоритетов поступающим запросам. Например, наибольший приоритет можно назначить IR0, следующий — IR1 и т. д. Когда запрос прерывания распознается приоритетной логикой как имеющий наибольший приоритет, три младших бита в регистре типа устанавливаются на номер линии с запросом, устанавливается бит в регистре обслуживания и выдается прерывание в ЦП. Если IF =1, ЦП возвращает сигнал подтверждения и схема управления выдает в ЦП тип прерывания. Все запросы с меньшими приоритетами блокируются до тех пор, пока не будет сброшен бит в регистре обслуживания (это обычно реализует процедура прерывания). Следовательно, когда команда STI повторно разрешает прерывания, запросы с более высоким приоритетом могут прервать текущую процедуру прерывания, тогда как запросы с меньшими приоритетами остаются заблокированными до сброса установленного бита в регистре обслуживания. Теперь процедура прерывания может управлять восприятием запросов с меньшими приоритетами. Чтобы программа могла сбрасывать биты в регистре обслуживания, он должен быть программируемым, т. е. должен иметь адрес порта ввода-вывода, делающий регистр доступным командам IN и OUT. Кроме встроенных приоритетов, предусмотрен однобайтный регистр маски, позволяющий маскировать отдельные запросы. Бит n в этом регистре маскирует вход IRn. Предполагается, что этот регистр также программируемый.

Младшие три бита регистра типа прерывания определяются запросом, выбранным приоритетной логикой. Если сделать регистр программируемым, появляется возможность инициализировать пять старших бит при включении системы.

Во многих микропроцессорных семействах имеются микросхемы управления приоритетными прерываниями. Для работы с микропроцессорами 8086/8088 предлагается программируемый контроллер прерываний 8259А фирмы Intel. Он аналогичен схеме, показанной на рис.12, но имеет больше возможностей.