- •9. Пассивные фвч, фнч

- •10.Фнч,фвч 1-го порядка

- •1 3 Дифторы

- •15 Генер-ры сунус-ных колебании на оу с мостом вина

- •14 Генер-ры сиг-лов

- •19.Таймеры(опр,классификация)

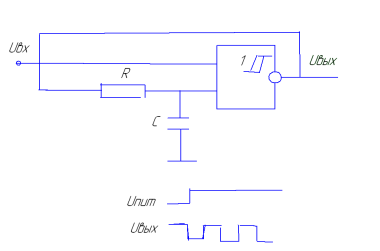

- •17.Мультивибратор (схема,временная диаграмма работы,формулы).

- •20.Структурные схемы однотактного и многотактного таймера(схемы,принцип работы)

- •21 Одновибратор на однотактном таймере кр1006ви1

- •22.Мультивибратор на основе интегрального таймера к1006 ви1.

- •23.Базовые понятия цифровой электроники

- •24.Выводы цифровых микросхем.

- •29.Инвертор

- •32.Исключающее или

- •30.Повторители и буферы

30.Повторители и буферы

П

и Б отлич-ся от инверторов тем, что они

не инвер-ют с-ал(существ. И инвертир Б.)

Обл-ть применен:1. Увелич нагруз сп-ти

с-ла,т.е. позвол подать с-лы на мн-во

вх-ов, для эт. Использ-ся Б с повыш вх

током.2.Бол-во Б им. вых ОК или 3С, что

позвол использ их для получ двунаправлен

линий или мультиплексирование сигн.

Под двунаправл лин. понимают такие

л(провода) с-лы по кот м. рапростр в 2х

противопол напр-ях. В отлич от

однонаправллиний, котор. Идут от одного

вых. К одному или неск вх-ам, к 2направ

лин. М. подключ одновр неск. Вх и неск.

Вых. Мультиплексир-ем наз-ся передача

разных с-ов по одним и тем же лин в разные

мом врем.Осн цель мульт- сокращ общего

ч-ла соедин линий.2направ л. всегда явл

мультип, а мультиплексир. Л. мб как

1направ, так и 2направл.В любом случае к

ней подкл. Неск-ко вых, 1 из которых в

данный момент врем наход в активн

сост-ии, а остальн вх переводятся в

пассивное сост-ие. МС с выходом

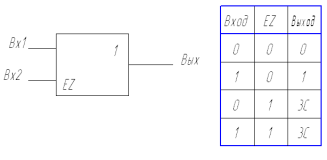

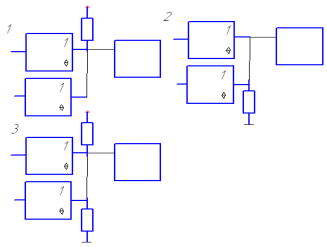

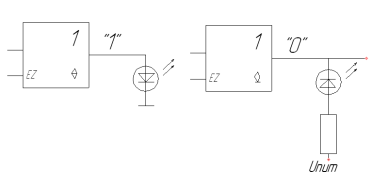

3С(лп8,11;ап5,6,14) Эти МС им управл вх EZ,

OE-назв

входа. Как правило с-ал на управл. Вх мб

любым: лог 0(активн.Сост МС), либо лог 1(

перевод в 3С сост) Б м.б. 1направл. И

2направл. С ин-ей с-ла, без инв-ии, с управл

всеми вх одновр, или с управл-ем группами

вх-ов и почти для всех МС активн

сост-ие-отриц ур-нь с-ла на вх упр-ия

Прост 1направБ без ин-ии-ЛП8(4 Б с вых 3С

и разд упр-ем) Из

табл. Видно, что когда управ с-ал на вхде

EZ=0,

то на вых МС с-ал будет опр-ся вых сиг-ом,

а если на управ вх EZ

сигнал лог 1, то вне зав-ти от вх с-ла на

вых МС б 3 сост-ие(пассивное) Эту МС

также м. испол-ть для замещения Б с вых

ОК для этого на вх МС под. лог 0, а вх с-ал

подают на вх упр-ия , при 0 на вх будет 0

на вых, а при 1 на вх на выходе буд 3С.Когда

необх обр-ть группы сиг-ов(напр, с-ал

под. на многоразряд вх), то в этом случ

необх примен Б с группов управ-ем,т.е.

Б, имеющ 1 вх с разреш EZ

на несколько выходов.Пример МС ЛП 11-6 Б,

раздел. На 2 гр., состоящ. Из 4х и 2х Б и

имеющ. Каждый свой вх управ. Приведём

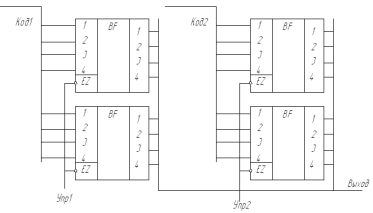

пример мультиплекс. 2х 8-разрядных кодов

с пом-ю 2х МС КП5

Из

табл. Видно, что когда управ с-ал на вхде

EZ=0,

то на вых МС с-ал будет опр-ся вых сиг-ом,

а если на управ вх EZ

сигнал лог 1, то вне зав-ти от вх с-ла на

вых МС б 3 сост-ие(пассивное) Эту МС

также м. испол-ть для замещения Б с вых

ОК для этого на вх МС под. лог 0, а вх с-ал

подают на вх упр-ия , при 0 на вх будет 0

на вых, а при 1 на вх на выходе буд 3С.Когда

необх обр-ть группы сиг-ов(напр, с-ал

под. на многоразряд вх), то в этом случ

необх примен Б с группов управ-ем,т.е.

Б, имеющ 1 вх с разреш EZ

на несколько выходов.Пример МС ЛП 11-6 Б,

раздел. На 2 гр., состоящ. Из 4х и 2х Б и

имеющ. Каждый свой вх управ. Приведём

пример мультиплекс. 2х 8-разрядных кодов

с пом-ю 2х МС КП5 Одноимен

выв обеих МС объедин м/у собой, пропускание

на вых кажд из 2х вх кодов разреш своим

сигналом управления(упр1, упр2) причём

при работе такой сх д.б. исключ момент

прихода этих 2х сигн-ов одновр, для того

чтобы исключ конфликты. Если лог 0 на

вх упр 1, код 1 перед-ся на вых, при лог 0

на вх управлен 2 код 2 перед на вых. Нельзя,

чтобы одновр упр1 и упр2 были бы 0, в таком

случ возник конфликт в работе. 2направл.

Б в отлич от 1направл.м. передав с-л в

обоих направ-ях. В зав-ти от спец. Управл

с-ла, вх м. станов вых, а вых вх. В таких

Б им. вх упр-ия 3им состEZ,

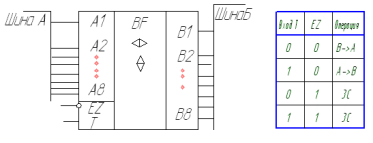

кот м. подключ как вх, так и вых. Приведем

МС 2направл. Б АП6, она м. передав с-лы м/у

2мя шинами А и Б в обоих напр-ях.

Одноимен

выв обеих МС объедин м/у собой, пропускание

на вых кажд из 2х вх кодов разреш своим

сигналом управления(упр1, упр2) причём

при работе такой сх д.б. исключ момент

прихода этих 2х сигн-ов одновр, для того

чтобы исключ конфликты. Если лог 0 на

вх упр 1, код 1 перед-ся на вых, при лог 0

на вх управлен 2 код 2 перед на вых. Нельзя,

чтобы одновр упр1 и упр2 были бы 0, в таком

случ возник конфликт в работе. 2направл.

Б в отлич от 1направл.м. передав с-л в

обоих направ-ях. В зав-ти от спец. Управл

с-ла, вх м. станов вых, а вых вх. В таких

Б им. вх упр-ия 3им состEZ,

кот м. подключ как вх, так и вых. Приведем

МС 2направл. Б АП6, она м. передав с-лы м/у

2мя шинами А и Б в обоих напр-ях. Из

табл. Видно, что на вх EZ

д. присутс ур-нь лог 0 и если на вх упр-я

Т лог 0, то с-ал с вых передаётся на вх, а

если на Т лог 1, то с-ал перед со вх на

вых., если на вх EZ

лог 1, то вне зав-сти от сигн на вх управленя

Т, то на вых будет всегда 3С. 2направлен.

Передачу также м. сделать на основе

однонапр буферов.

Из

табл. Видно, что на вх EZ

д. присутс ур-нь лог 0 и если на вх упр-я

Т лог 0, то с-ал с вых передаётся на вх, а

если на Т лог 1, то с-ал перед со вх на

вых., если на вх EZ

лог 1, то вне зав-сти от сигн на вх управленя

Т, то на вых будет всегда 3С. 2направлен.

Передачу также м. сделать на основе

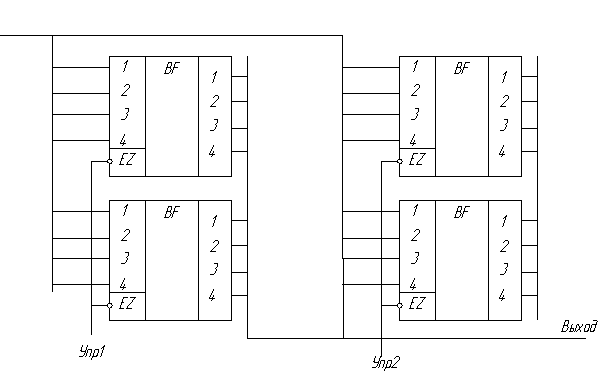

однонапр буферов. При

лог 0 на вх упр1 с-лы из шиныА перед-ся в

шинуБ, а при лог0 на вх упр2 с-лы из шиныБ

перед в шинуА

При

лог 0 на вх упр1 с-лы из шиныА перед-ся в

шинуБ, а при лог0 на вх упр2 с-лы из шиныБ

перед в шинуА

Одновр подача лог 0 на вх упр-я 1 и 2 запрещ, т.к. состоян. вых. Будет неопредел.При лог1 на вх упр-я 1 и 2 шины А и Б будут отключены др от др и нах-ся в сост 3С.Времен. Пар-ры Б вкл помимо задержки с-ла от инф вх до инф вых, включ такой пар-р, как задержка перехода в 3С. Вел-на этих задержек(задержка вкл 3C) и задержка выхода из 3С обычно в2р >, чем tзад перехиз лог 0 в лог 1 и из лог 1 в лог 0.Отключ вых Б 3С или ОК требует применен нагруз рез-ов, в противном случ вх подключ к вых нах в 3ем сост оказыв подвешен. И в рез-те м. происх. сбои при работе сх.

Подключ.

нагруз р-ра к вых ОК произв-ся стандартным

сп-ом, а для вых 3с состояния м.б. использслед

сх подключ нагрузочн. Рез-ов. Для

1 в 3 на вход послед сх. Б.пост.ур-нь лог

1.Для 2 в 3С-лог 0.Для 3 в 3С-лог1

Для

1 в 3 на вход послед сх. Б.пост.ур-нь лог

1.Для 2 в 3С-лог 0.Для 3 в 3С-лог1

Обл-ть

применения Б связ. с использ-ем их в

сист-ах индикации, т.к они имеют большие

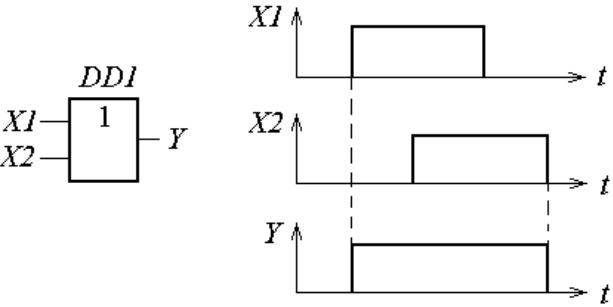

вых токи. 32.Исключающее

ИЛИПод

функцией Искл ИЛИ понимается сл: 1 на

вых появл тогда, к только на 1 вх присут

1. Если 1иц на вх-ах 2 или >, или если на

всех вх 0, то на вых будет 0. Все вх эл-ов

Искл ИЛИ равноправны, однако ни 1 из вх

не м. заблок другие вх, установив вы с-ал

в уровень 1 или 0.

32.Исключающее

ИЛИПод

функцией Искл ИЛИ понимается сл: 1 на

вых появл тогда, к только на 1 вх присут

1. Если 1иц на вх-ах 2 или >, или если на

всех вх 0, то на вых будет 0. Все вх эл-ов

Искл ИЛИ равноправны, однако ни 1 из вх

не м. заблок другие вх, установив вы с-ал

в уровень 1 или 0.

Исключающее или-не

С т.з матем, элемент Искл ИЛИ выполн опер-ию так назыв суммир по mod2. Поэтому их также принято называть сумматорами по mod2. Основное применение эл-ов Искл ИЛИ сост в срав-нии 2вх с-ов. Т.е., к на вх прих 2 1цы или 2 0(с-лы совпад), на вых формир 0.Также э-нт м. примен в смешивании 2х с-ов

Но при проектир необх. Учитыв, что задержка выполн ф-ии у Эл-та искл или примерно в 1,5 раза >, чем у прост.ЛЭ И, И-НЕ, ИЛИ, ИЛИ-НЕ.Также необх предусм ситуацию, чтобы коды измен бы одновремен, для этого необх также ввод. синхрониз стробирующ имп-ом.

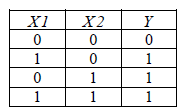

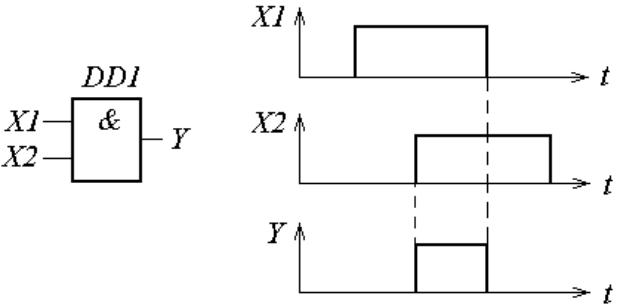

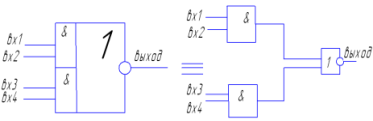

31.Элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ

ИЛИ При осущ опер-ии лог слож ф-ия = 1, когда хотя бы на 1 из вх 1 из перемен прин знач лог1

.

И

При логическом умножении функция = 1

только в том единст случае, когда на

всех его вх присутст 1цы.

И

При логическом умножении функция = 1

только в том единст случае, когда на

всех его вх присутст 1цы.

И-НЕ,

ИЛИ-не![]() Всё

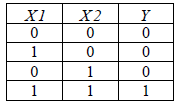

вышесказ. справедливо для с-ов полож.лог.

В случае отриц.логики при нулевых вх и

вых с-ах эл-т И выполняет ф-ию ИЛИ, а Эл-т

ИЛИ выполняет ф-ию И. Это всегда след

учитыв при проектир уст-ва, т.к. совместно

Мб использ положит и отриц логики.Все

вышеперечисл Эл-ты м.б использ в сх

повторит-ей и инв-ов, для этого неогбх

объединить вх(1 сп-б) или (2 сп-б) на

неиспольз вывподать с-лы необх ур-ня.

Второй сп-б предпочт, тк объединение

вх-ов сниж быстродейст и увел вхо

ток.

Всё

вышесказ. справедливо для с-ов полож.лог.

В случае отриц.логики при нулевых вх и

вых с-ах эл-т И выполняет ф-ию ИЛИ, а Эл-т

ИЛИ выполняет ф-ию И. Это всегда след

учитыв при проектир уст-ва, т.к. совместно

Мб использ положит и отриц логики.Все

вышеперечисл Эл-ты м.б использ в сх

повторит-ей и инв-ов, для этого неогбх

объединить вх(1 сп-б) или (2 сп-б) на

неиспольз вывподать с-лы необх ур-ня.

Второй сп-б предпочт, тк объединение

вх-ов сниж быстродейст и увел вхо

ток. Также

по ф-ии И объед-ся вх-ы более слож МС,

т.е. эта ф-ия выполн только тогда, когда

на все объединён входы по ф-ии И поступ

с-лы нужной полярности, при этом необх

учитывать, что на прям вх необх-мо

подавать лог 1, если если на инв-ые вх

для выполн лог ф-ии необход подать лог

0. Выше были рассмотр эл-ты, в котор с-лы

измен-ся неодновр-, а при одновр- измен

с-ов вых с-ал на некотор пром-ки t

м стать нестабил и неопредел для исключ

этого использ спец сигнал стробирования.

Также

по ф-ии И объед-ся вх-ы более слож МС,

т.е. эта ф-ия выполн только тогда, когда

на все объединён входы по ф-ии И поступ

с-лы нужной полярности, при этом необх

учитывать, что на прям вх необх-мо

подавать лог 1, если если на инв-ые вх

для выполн лог ф-ии необход подать лог

0. Выше были рассмотр эл-ты, в котор с-лы

измен-ся неодновр-, а при одновр- измен

с-ов вых с-ал на некотор пром-ки t

м стать нестабил и неопредел для исключ

этого использ спец сигнал стробирования.

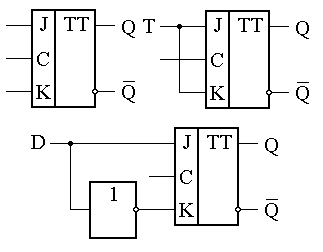

40.Триггеры устр-во,имеющее два устойчивых состояния и способные скачком переходить из одн. Уст.сост.в др. под действием управляющих сигн. и любое сост. сохран.сколь угодно долго после снятия управляющ.напряж-я.Поэт. тригеры способны хранить 1 бит информации лог 0 или лог1.реализ-ся они с пом ЛЭ И-НЕ или ИЛИ-НЕ.по способу записи информ. Т делятс яна синхронные и ассинхронные.ассинхронные это триггеры способные переходить из одн.уст-го сост. в др. под действ.управляющ.сигн.в ассинхронном тригере изменение его устойч.сост.мен-ся непосредств. Потенциалом управляющ.сигн.у ассинхронного Т кроме информационных вх-в есть вход синхронизац.и реагиров. Такой Т будетреагир. на вх-ые информ.сигн.только в определ.момент времени котор.задается с пом вх-го сигн.синхрониз.По функцион-му призн делятся на RS,JK,D,T типы.

33.

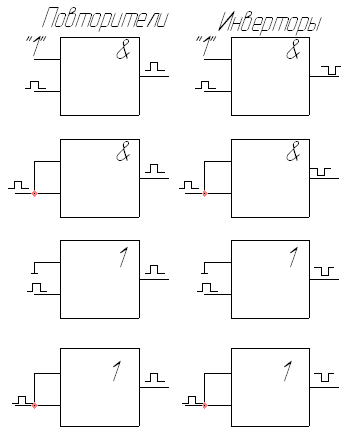

Сложные

ЛЭ.Помимо

простых эл-ов в некотор. серии МС входят

сложные эл-ты,кот-ые предст.собой

комбинацию из простых эл-ов т.е.

в корпусе МС содерж. 2 эл-та кажд. из

кот-ых представляет комбинац. Из 2-х

эл-ов 2И и одного лог. эл-та 2ИЛИ-НЕ, по

эт. же принципу строятся др. МС сложн.

серий.Отлич-ся они м/у собой кол-вом

выводов входн. Эл-та И. Триггер

шмидта-специфич.

Эл-т спец-но предназнач-ый для работы с

входн. аналог. сигналами.Он преобразует

аналог. сигнал в цифровой и предназнач.

для восстановл. формы сигнала пришедших

с линии связи,т.к. при подаче сигналов

искажаются фронты сигн.(станов. пологими)

в рез-те кот-ых форма сигнала мож. Стать

т.е.

в корпусе МС содерж. 2 эл-та кажд. из

кот-ых представляет комбинац. Из 2-х

эл-ов 2И и одного лог. эл-та 2ИЛИ-НЕ, по

эт. же принципу строятся др. МС сложн.

серий.Отлич-ся они м/у собой кол-вом

выводов входн. Эл-та И. Триггер

шмидта-специфич.

Эл-т спец-но предназнач-ый для работы с

входн. аналог. сигналами.Он преобразует

аналог. сигнал в цифровой и предназнач.

для восстановл. формы сигнала пришедших

с линии связи,т.к. при подаче сигналов

искажаются фронты сигн.(станов. пологими)

в рез-те кот-ых форма сигнала мож. Стать

![]() и

поэтому для восстановл. прямоуг. ф-мы

сигн. примен. триг.шм.

и

поэтому для восстановл. прямоуг. ф-мы

сигн. примен. триг.шм. 1гр.

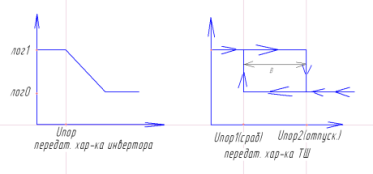

В случ. обычн. инвертора при входном

напряж. ниже порог.знач. выходного сигн.

будет в лог.1 а в случ. если вх. напр. выше

порогов. Знач., то вых. сигн. будет в лог.0

и не имеет знач. возраст.или убыв.

2гр В случ.

триг.Шм. с инверсией имеет принципиальн.

Знач-е возраст. Или убыв. Сигнал.При

возраст. Вх. сигн. от 0 до Uпит

порог срабатыв. Буд. Опред-ся напряж

Uпор1

(Uср.)

а при уменьш. Сигнала от Uпит

до 0 порог срабатыв. будет опр-ся Uпор2

(Uотпуск.)

причем Uпор1

всегда >Uпор2

β-ширина

петли гистер.Наличие гистер. Приводит

к тому, что любые шумы и помехи амплит.

Uпор1-Uпор2

отсекаются и любые фронты даже полосов.

Сигнала преобраз-ся в крутые фронты.Главн.

условием чтобы амплит. Вх. сигнала была

бы>чем Uпор1

1гр.

В случ. обычн. инвертора при входном

напряж. ниже порог.знач. выходного сигн.

будет в лог.1 а в случ. если вх. напр. выше

порогов. Знач., то вых. сигн. будет в лог.0

и не имеет знач. возраст.или убыв.

2гр В случ.

триг.Шм. с инверсией имеет принципиальн.

Знач-е возраст. Или убыв. Сигнал.При

возраст. Вх. сигн. от 0 до Uпит

порог срабатыв. Буд. Опред-ся напряж

Uпор1

(Uср.)

а при уменьш. Сигнала от Uпит

до 0 порог срабатыв. будет опр-ся Uпор2

(Uотпуск.)

причем Uпор1

всегда >Uпор2

β-ширина

петли гистер.Наличие гистер. Приводит

к тому, что любые шумы и помехи амплит.

Uпор1-Uпор2

отсекаются и любые фронты даже полосов.

Сигнала преобраз-ся в крутые фронты.Главн.

условием чтобы амплит. Вх. сигнала была

бы>чем Uпор1

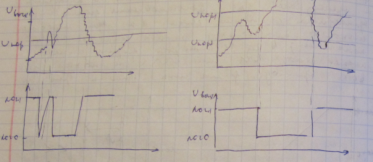

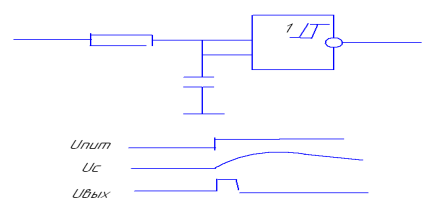

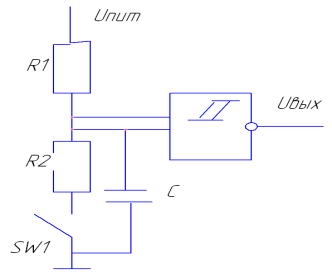

Вторым

примен. Тр.Шм. явл. Формиров. Сигн. начальн.

Сброса при включ. Напр.пит. для схемы.Необх.

этого обусловлено тем,что при включ.

Uпит

у сложн. МС имеющ. Внутр. Память выходн.

Сигнал м. приним. Любое знач.,а для

правильн. Работы схемы необх. Обнулить

все эти эл-тф и для формиров-ия сигнала

начальн. Сброса к тр.шм. подключ.

RC-цепочка.

Вторым

примен. Тр.Шм. явл. Формиров. Сигн. начальн.

Сброса при включ. Напр.пит. для схемы.Необх.

этого обусловлено тем,что при включ.

Uпит

у сложн. МС имеющ. Внутр. Память выходн.

Сигнал м. приним. Любое знач.,а для

правильн. Работы схемы необх. Обнулить

все эти эл-тф и для формиров-ия сигнала

начальн. Сброса к тр.шм. подключ.

RC-цепочка. На

Тр.Шм можно также построить ген-ор

прямоуг. напряж-ий.

На

Тр.Шм можно также построить ген-ор

прямоуг. напряж-ий. Uвх

под лог.1, емкость нач-ет заряж-ся и

разряж. И на вых. схемы

Uвх

под лог.1, емкость нач-ет заряж-ся и

разряж. И на вых. схемы![]() Подавление

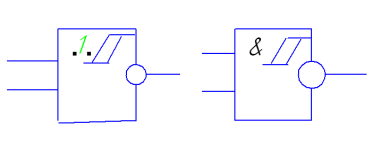

дребезга контакта люб.мех. контакт

(кнопка, переключатель) не замык. и не

размык. Сразу, люб. Замык-е сопров-ся

неск-ми замык-ми контактов,кот-ые приводят

в свою очередь к появл. Поразитных

имп-ов,кот-ые мог. Сказыв. На дальнейш.

Работе сх., поэтому для исключ-я дребезга

использ. След.сх.

Подавление

дребезга контакта люб.мех. контакт

(кнопка, переключатель) не замык. и не

размык. Сразу, люб. Замык-е сопров-ся

неск-ми замык-ми контактов,кот-ые приводят

в свою очередь к появл. Поразитных

имп-ов,кот-ые мог. Сказыв. На дальнейш.

Работе сх., поэтому для исключ-я дребезга

использ. След.сх. Т.к.

конденс.заряж. довольно медл.,в рез-те

этого кор-ие имп-сы подавл-ся и не проходят

на вых.ТШ Номинал R1

обычн. берется в 6-7 раз > ном. R2

для того,чтобы переключ-ль SW1

в замкнут. Сост. давал бы на вых. ТШ

лог.0,номиналы сопротивл.берутся от

сотен Ом о неск. кОм.Емкость кажд.м.б.

выбрана в шир.диап. и завис. От длит-ти

дребезга контактов конкретн.устр-ва

Т.к.

конденс.заряж. довольно медл.,в рез-те

этого кор-ие имп-сы подавл-ся и не проходят

на вых.ТШ Номинал R1

обычн. берется в 6-7 раз > ном. R2

для того,чтобы переключ-ль SW1

в замкнут. Сост. давал бы на вых. ТШ

лог.0,номиналы сопротивл.берутся от

сотен Ом о неск. кОм.Емкость кажд.м.б.

выбрана в шир.диап. и завис. От длит-ти

дребезга контактов конкретн.устр-ва

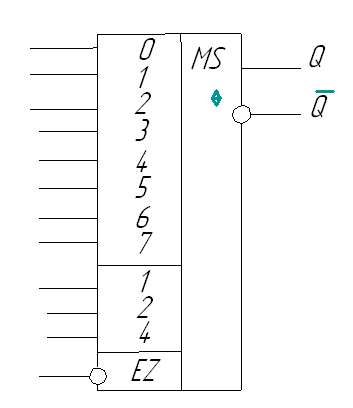

36.Мультиплексоры.Предназнач.

дляпоочередн.передачи на 1 выход одного

или неск.имп-оввых-ых сигн-в,в схемах МП

обознач-ся MS,в

отеч.спрвочн. КПКол-во мультиплексируемых

входов наз.кол-ом каналов мультиплексора,а

кол-во выходов наз.ч-ом разрядов

МП.Напр.,2хканальн.4хразрядн.МП имеет 4

выхода на кажд. из кот-ых мож.передаваться

1 из 2-х входн.сигналов.Ч-ло каналов МП

входящ. В станд. Серии м.б. от 2-х 16-ти а

ч-ло разрядов от 1 до 4 причем > каналов

им. МП тем < у него разрядов.Управление

работой МП (выбор N

канала)осущ-ся с пом-ю вх-го кода адреса

например для 4хканальн.МП необходим

2хразрядн адресный код,разряды кода

обознач-ся цифрами 1 2 4 8 или А0-А3,МП быв.с

вых. 2S,OK

и 3S.

Выходы м.б. как прямыми,так и инверсными.МП

с выв. 3S

позвол. Получить двунаправл. И

мультиплексиров. Линии нек.МС МП имеют

выход разреш-ия/запрета S. К

одному вых. может подключ.неск.ист-ов.вх-ых

сигн.Другими примерами использ. МП

явл-ся передача данных от неск. Источников

сигнала по 1 общему каналу с раздел.по

времени ;использ-ся в ПЗУ;преобразован.

Параллельного кода в последоват-й;использ-ся

как ДШ и как Регистры

К

одному вых. может подключ.неск.ист-ов.вх-ых

сигн.Другими примерами использ. МП

явл-ся передача данных от неск. Источников

сигнала по 1 общему каналу с раздел.по

времени ;использ-ся в ПЗУ;преобразован.

Параллельного кода в последоват-й;использ-ся

как ДШ и как Регистры

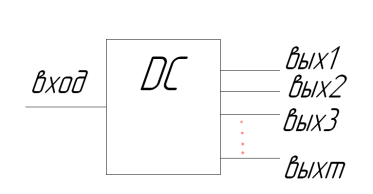

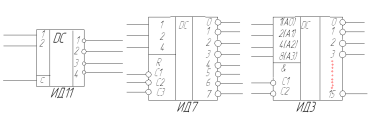

34.Дешифратор.Преобраз.двоичн.код

в сигн. на одном выходе,т.е. дешифрует

код.Кол-во вых.сигн. дешифр.=кол-ву

возможн.сост-й вых-го кода,т.е. ![]() где

n-разрядность

вх-го двоичн.кода.

где

n-разрядность

вх-го двоичн.кода. На

вых.дешифр. всегда присутствует только

1 сигнал,причем N

этого сигн.однозн.опр-ся вх-ым кодом.На

чертежах МС Деш. Обознач. DC

от англ. Decoder,в

отечетсв. Справочн. МС Д обознач-ся букв.

ИТ. Различ. полные и неполные Деш.В полном

Деш. (n-m)

m=

,

где n-ч-ло

входов, а m-число

вых-в Деш.В неполных Деш. m<

.

Исп-ся неполные Деш.,напр. для преобраз.

Двоичн. Кода в двоично-десятичн., а также

в светодиодн.индикации. Примером

неполного Деш. мож. Явл-ся МС ИД1 на

4хразр. Вх-ой код и 10 вых-ов 4-10.Стандартн.

серии Деш. входят МС на 2хразрядн.вх-ой

код и 4 выхода (2-4 на 3хразрядн.Вх-ой код

и 8 вых-ов (3-8))и 4хразр. Входн. Код и 16 вых.

(4-16)

На

вых.дешифр. всегда присутствует только

1 сигнал,причем N

этого сигн.однозн.опр-ся вх-ым кодом.На

чертежах МС Деш. Обознач. DC

от англ. Decoder,в

отечетсв. Справочн. МС Д обознач-ся букв.

ИТ. Различ. полные и неполные Деш.В полном

Деш. (n-m)

m=

,

где n-ч-ло

входов, а m-число

вых-в Деш.В неполных Деш. m<

.

Исп-ся неполные Деш.,напр. для преобраз.

Двоичн. Кода в двоично-десятичн., а также

в светодиодн.индикации. Примером

неполного Деш. мож. Явл-ся МС ИД1 на

4хразр. Вх-ой код и 10 вых-ов 4-10.Стандартн.

серии Деш. входят МС на 2хразрядн.вх-ой

код и 4 выхода (2-4 на 3хразрядн.Вх-ой код

и 8 вых-ов (3-8))и 4хразр. Входн. Код и 16 вых.

(4-16) Различ-ся

входами управл-ия (разреш-ия и запрета)

входн. Сигналов,а также выходами:мож.иметь

2S

илиОК (нужен нагруз. Рез-ор к Uпит)

Вых.сигналы Деш. имеют отрицат.

Полярность,вход на кот. Поступ. Входной

двоичный код назыв. Адресным. А0-А3-где,1или

АО-младш.разряд,8или А3-старш.разряд. Для

примера рассмотр. МС Деш. ИД 7(3-8),где

n=3,m=8.

Различ-ся

входами управл-ия (разреш-ия и запрета)

входн. Сигналов,а также выходами:мож.иметь

2S

илиОК (нужен нагруз. Рез-ор к Uпит)

Вых.сигналы Деш. имеют отрицат.

Полярность,вход на кот. Поступ. Входной

двоичный код назыв. Адресным. А0-А3-где,1или

АО-младш.разряд,8или А3-старш.разряд. Для

примера рассмотр. МС Деш. ИД 7(3-8),где

n=3,m=8. МС

Деш. имеет 3 вывода,объед. По ф-ции И

C1,C2,C3

входов разреш-ния,причем они имеют

указанную на рис. Полярность, т.е. для

работы Деш-ра C1=1,C2=C3=0

Первые 3 строки табл. Соот-ют запрету

вых.сигн.Разреш-ия выхода буд.если сигн.

C1=1

а C2=C3=0

в табл. Х обознач.безразл.сост. данного

входа (неважно о или 1 там, номер

активн.выхода,на кот-ом формир-ся нулевой

сигн. опр-ся кодом на адресных входах

1,2,4 причем 1-младш.разряд,4-старший.Примен.

Деш. для дешифриров. Вх-ых кодов,при этом

выводы С исключ-ют,как управляющ. Или

стробирующ., также Деш. м.б. использован

при выборе как.-то необх-го кода (появл.

0 на вых.буд. означать приход необх.кода)также

Деш может примен-ся для перекоммутации

1 вх. сигн. на неск. Выходов, при этом Деш.

буд. Явл. Демультиплексором. Также Деш.

мож. Использов-ся для формиров-ния адреса

устр-ва при обмене м/у ними и микропроц.

Для Деш. как и для др. цифр.МС критична

ситуац.одноврем. измен. (или почти

одноврем.)вх-ых сигн., напр. если стробы

пост-но разреш. Работу Деш. то в

мом.измен.вх-го кода на вых-ах Деш могут

появ-ся паразитн.коротк.имп-сы,это м.б.

связано с неодноврем. Измен. Входн.кода

из-за нелов-ва МС из-за задержек

распростр.сигнала по линиям,а также

из-за задерж.сигн. самой МС.Для исключ.

Паразитн.сигн. на вых-де Деш. необх-мо

использ-ть синхрониз-ю,с пом-ю

строб-сигнала.При этом строб-сигнал

д.начаться после текущ.измен.вх.кода и

закан-ся до след-го измен. Вх.кодаНеобх.

учитыв.,что задержка распр.сигнала Деш

почти в 2 раза > чем у прост.ЛЭ.

МС

Деш. имеет 3 вывода,объед. По ф-ции И

C1,C2,C3

входов разреш-ния,причем они имеют

указанную на рис. Полярность, т.е. для

работы Деш-ра C1=1,C2=C3=0

Первые 3 строки табл. Соот-ют запрету

вых.сигн.Разреш-ия выхода буд.если сигн.

C1=1

а C2=C3=0

в табл. Х обознач.безразл.сост. данного

входа (неважно о или 1 там, номер

активн.выхода,на кот-ом формир-ся нулевой

сигн. опр-ся кодом на адресных входах

1,2,4 причем 1-младш.разряд,4-старший.Примен.

Деш. для дешифриров. Вх-ых кодов,при этом

выводы С исключ-ют,как управляющ. Или

стробирующ., также Деш. м.б. использован

при выборе как.-то необх-го кода (появл.

0 на вых.буд. означать приход необх.кода)также

Деш может примен-ся для перекоммутации

1 вх. сигн. на неск. Выходов, при этом Деш.

буд. Явл. Демультиплексором. Также Деш.

мож. Использов-ся для формиров-ния адреса

устр-ва при обмене м/у ними и микропроц.

Для Деш. как и для др. цифр.МС критична

ситуац.одноврем. измен. (или почти

одноврем.)вх-ых сигн., напр. если стробы

пост-но разреш. Работу Деш. то в

мом.измен.вх-го кода на вых-ах Деш могут

появ-ся паразитн.коротк.имп-сы,это м.б.

связано с неодноврем. Измен. Входн.кода

из-за нелов-ва МС из-за задержек

распростр.сигнала по линиям,а также

из-за задерж.сигн. самой МС.Для исключ.

Паразитн.сигн. на вых-де Деш. необх-мо

использ-ть синхрониз-ю,с пом-ю

строб-сигнала.При этом строб-сигнал

д.начаться после текущ.измен.вх.кода и

закан-ся до след-го измен. Вх.кодаНеобх.

учитыв.,что задержка распр.сигнала Деш

почти в 2 раза > чем у прост.ЛЭ.

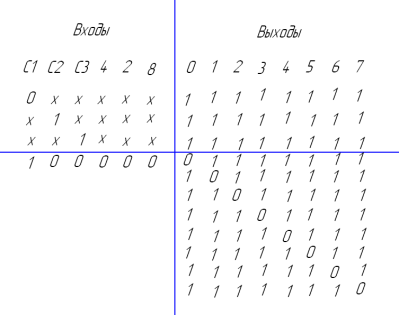

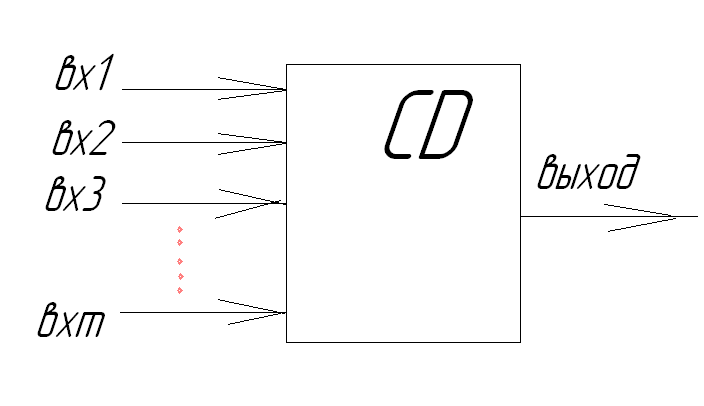

35.Шифратор.

Шифр.

Преобр. Номер вх. сигнала в выходн.сигнальн.

код,т.е. шифрует вх.код.Кол-во вх-ых сигн.

шифр.=кол-ву возм. Сост-ий выходн.двоичного

кода,т.е.

,где

n-разрядн.

Двоичного кода. При

поступл. Сигнала на 1 из вх-в Шифр.на его

вых-ах формир.код соотв. номеру этого

выхода.Шифрирование-сп-б сжатия вх-ых

данных за счет преобр-ия m-разрядн.кода

в n-разрядн.двоичн.код.Обознач.

в схемах CD(coder)в

отеч-ых справ.МС обознач.Шифр. выполняет

ф-ию обратную Дешифр.Полный Шифр. Имеет

m=

входов и n

выходов,м.б. неполные Шифр.,когда

m<

также

Шифр. М.б. неприоритетный (если разреш.подача

только 1 акт.сигнала) или приоритетн.(если

доп-ся подача одновременно нескольких

актиын.сигн. на вход).

При

поступл. Сигнала на 1 из вх-в Шифр.на его

вых-ах формир.код соотв. номеру этого

выхода.Шифрирование-сп-б сжатия вх-ых

данных за счет преобр-ия m-разрядн.кода

в n-разрядн.двоичн.код.Обознач.

в схемах CD(coder)в

отеч-ых справ.МС обознач.Шифр. выполняет

ф-ию обратную Дешифр.Полный Шифр. Имеет

m=

входов и n

выходов,м.б. неполные Шифр.,когда

m<

также

Шифр. М.б. неприоритетный (если разреш.подача

только 1 акт.сигнала) или приоритетн.(если

доп-ся подача одновременно нескольких

актиын.сигн. на вход). (ТАБЛИЦАААААААА)

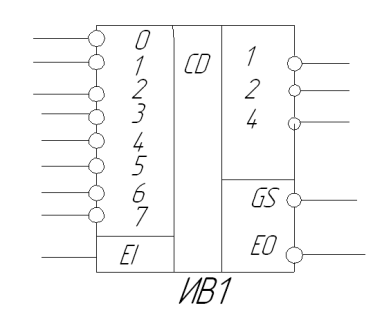

Шифр. 8-3 у отеч. МС все входы и вых.

Инверсные т.е. активн.сигн.нулевые.Эта

МС имеет вход разреш-ия EI

,выход GS-вых.

признака прихода любого вх-го сигн.,вых.

EO-вых.

переноса,кот-ый позвол. Объедин.

Неск.Шифрат. для увелич. Их разрядн-ти;из

табл. Видно,то на вых-ах 1,2,4 формир-ся

инверсн.двоичн.код,номера вх-ой В случае

поступл. На вход одновр. Неск-их вх-ых

акт.сигналов, на вых-де формир. вых-ой

код,соотв. входу с наиб-м номером,т.е.

старшие входы имеют приоритет перед

младшими и такой шифр. Наз.преоритетным.При

отсутствии вх-ых сигн. (2 строка табл.)

на вых. формир-ся код 111,единичн. Сигнал

на вх. EI

запрещает работу шифрат. (1 стр. табл.) и

все входы уст. В 1.На вых. GS

фрмир-ся нулевой сигнал при приходе

любого вх.сигн.,что позвол. Отличить

ситуацию прихода нулевого вх.сигн.от

ситуации отсутств.вх. сигналов.Вывод

EO

уст-ся активным (нулевым при отсутств.

Входных сигн.,но при разреш-ии на входе

EI

одноврем.им почти одноврем.измен. на

входе шифрат. Приводят к появл.периода

неопредел-ти на его выходах)В это время

выходн.код Шифрат. Мож. Принимать вых-ое

знач-ия,не соотв. вх-му сигналу, поэт. В

тех случаях,когда вх.сигн. мож.приходить

одновременно необх.синхрон.вых.кода с

пом-ю разрешающ.сигн.EI

кот-ый стан-ся активн.только тогда,когда

сост. неопр-ти вх.кодов закончились.Задержка

распростран.сигн.от входа до вых. Шифрат.

Почти в 2 раза >чем у ЛЭ станд.примен.

Шифрат-сокращ.кол-ва лин-ых сигналов.Например

выше привед. Шифрат.сворачив.8 сигн.в

3Также Шифрат примен-ся для ввода данных

в цифр.устр-ва с пом-ю клавиатуры

(ТАБЛИЦАААААААА)

Шифр. 8-3 у отеч. МС все входы и вых.

Инверсные т.е. активн.сигн.нулевые.Эта

МС имеет вход разреш-ия EI

,выход GS-вых.

признака прихода любого вх-го сигн.,вых.

EO-вых.

переноса,кот-ый позвол. Объедин.

Неск.Шифрат. для увелич. Их разрядн-ти;из

табл. Видно,то на вых-ах 1,2,4 формир-ся

инверсн.двоичн.код,номера вх-ой В случае

поступл. На вход одновр. Неск-их вх-ых

акт.сигналов, на вых-де формир. вых-ой

код,соотв. входу с наиб-м номером,т.е.

старшие входы имеют приоритет перед

младшими и такой шифр. Наз.преоритетным.При

отсутствии вх-ых сигн. (2 строка табл.)

на вых. формир-ся код 111,единичн. Сигнал

на вх. EI

запрещает работу шифрат. (1 стр. табл.) и

все входы уст. В 1.На вых. GS

фрмир-ся нулевой сигнал при приходе

любого вх.сигн.,что позвол. Отличить

ситуацию прихода нулевого вх.сигн.от

ситуации отсутств.вх. сигналов.Вывод

EO

уст-ся активным (нулевым при отсутств.

Входных сигн.,но при разреш-ии на входе

EI

одноврем.им почти одноврем.измен. на

входе шифрат. Приводят к появл.периода

неопредел-ти на его выходах)В это время

выходн.код Шифрат. Мож. Принимать вых-ое

знач-ия,не соотв. вх-му сигналу, поэт. В

тех случаях,когда вх.сигн. мож.приходить

одновременно необх.синхрон.вых.кода с

пом-ю разрешающ.сигн.EI

кот-ый стан-ся активн.только тогда,когда

сост. неопр-ти вх.кодов закончились.Задержка

распростран.сигн.от входа до вых. Шифрат.

Почти в 2 раза >чем у ЛЭ станд.примен.

Шифрат-сокращ.кол-ва лин-ых сигналов.Например

выше привед. Шифрат.сворачив.8 сигн.в

3Также Шифрат примен-ся для ввода данных

в цифр.устр-ва с пом-ю клавиатуры

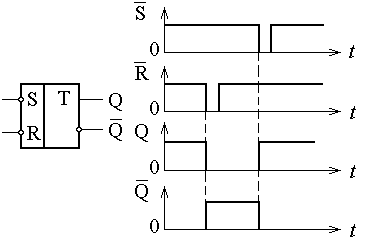

41. Асинхронным наз. триггер, кот. Перех-т из одного устойч. состояния в др. при воздействии управляющих сигналов.

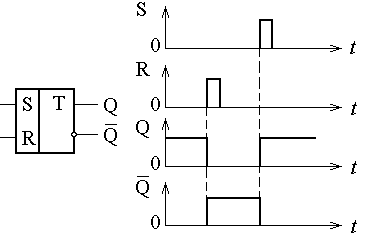

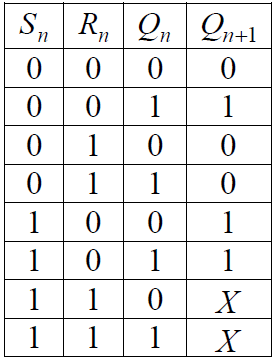

RS-триггер

с прямыми входами. Такой

триггер реализуется на двух универс-х

логич-х эл-тах ИЛИ

– НЕ.

Триггер

имеет два выхода (прямой и инверсный) и

два

Триггер

имеет два выхода (прямой и инверсный) и

два

входа. Вход, подача сиг-ла на кот.переводит триггер в

сост-е Q=1, наз. S-входом. Вход, подача сиг-ла на кот.переводит триггер в состояние Q=0, наз. R-входом. При наличии на входах ур-ней лог.0 (S=0, R=0) на вых. Q может быть либо уровень лог.1, либо лог.0. Если то Q=1, то на инверсном вых. будет Q =0. Это сост-е триггера явл. устойчивым. В таком сост-и подача сиг-ла лог.1 на S-вход не изменяет сост-е триггера. Подача же сиг-ла лог.1 на R-вход переведет триггер в другое устойч. сост-е (Q=0, Qинв =1), в кот.он будет оставаться и после оконч-я входного сиг-ла. При отсутствии вх. сиг-лов триггер сохраняет свое исходное сост-е. Особо следует рассмотреть случай одноврем. воздейст-я входных сигналов S=R=1. При таком сочет-и вх. сиг-лов на обоих вых. будет лог.0, что противоречит логике функционирования триггера. Такое сочетание вх. сиг-в явл. запрещенным.

RS-триггер

с инверсными входами.

Такой тр-р

реализ-ся на двух универс-х лог-х эл-тахИ

– НЕ. Он также имеет два вх. и два вых.

Режим хран-я

инф-и обеспеч-ся, когда на обоих вх. ур-ни

лог.1.

Перекл-е

тр-ра из одного устойч. сост-я в др.

осущ-ся путем подачи на тот или иной вх.

ур-ня лог.0. В таком триггере также имеется

запрещ. комбинация входных сигналов, а

именно S=R=0.

Перекл-е

тр-ра из одного устойч. сост-я в др.

осущ-ся путем подачи на тот или иной вх.

ур-ня лог.0. В таком триггере также имеется

запрещ. комбинация входных сигналов, а

именно S=R=0.

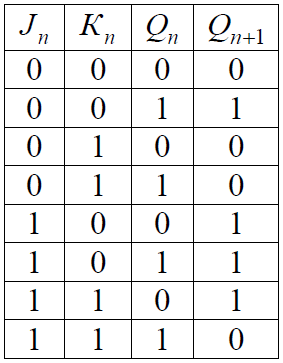

42. Триггеры JK-типа называют универсальными. JK-триггер обычно выполняется синхронным и двухступенчатым. Структурная схема JК-триггера включает в себя два RS-триггера с 10

инверсными

входами и четыре логических элементаИ

– НЕ. JK-триггер

состоит из основного RS-триггера,

в который записывается проходящая

информация, и вспомогательного RS-

триггера, в который переписывается

информация из основного триггера.

JK-триггер

функционирует как RS-триггер,

но в нем устранена неопределенность,

возникающая у RS-триггера,

когда R=S=1,

т.е. в таком триггере нет запрещенных

комбинаций входных сигналов.

Данная

сх. JK-тр-а

перех. в др. устойч-е сост-е не в момент

подачи сиг-ла, а после его окончания.

Подача сиг-ла на вх. J устанав-ет тр-р в

сост-е Q= 1, а сиг-л, поданный на вх. К ,

переводит тр-р в сост-е Q= 0.

Одноврем. подача сиг-лов лог.1

на

входы J

и

К,

при любом исх. Сост-и тр-ра приведет к

тому, что JK-тр-р

перек-ся в др. устой. сост-е.

Данная

сх. JK-тр-а

перех. в др. устойч-е сост-е не в момент

подачи сиг-ла, а после его окончания.

Подача сиг-ла на вх. J устанав-ет тр-р в

сост-е Q= 1, а сиг-л, поданный на вх. К ,

переводит тр-р в сост-е Q= 0.

Одноврем. подача сиг-лов лог.1

на

входы J

и

К,

при любом исх. Сост-и тр-ра приведет к

тому, что JK-тр-р

перек-ся в др. устой. сост-е.

43. Тр-ры, работающие с исп-ем синхр-щих сиг-в, наз. синхронными или тактируемыми. Синхронный RS-триггер сост. из асинхронного RS-триггера с инверс. Вх. и двух логич. эл-товИ - НЕ, обесп-х синхр. режим работы.

Буквой

C обознач. Вх. тактовых импульсов. При

наличии вх. сиг-ла ( S = 1 или R= 1) перекл-е

тр-ра происх. только при подаче тактового

имп-са C = 1, т.к. только при этом усл-и на

одном из вх. асинхр-го тр-ра возникает

сиг-л лог.0. Синхр-й

Буквой

C обознач. Вх. тактовых импульсов. При

наличии вх. сиг-ла ( S = 1 или R= 1) перекл-е

тр-ра происх. только при подаче тактового

имп-са C = 1, т.к. только при этом усл-и на

одном из вх. асинхр-го тр-ра возникает

сиг-л лог.0. Синхр-й

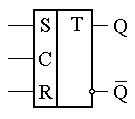

RS-тр-р имеет запрещ-ю комбинацию вх. сиг-в. На временной диаграмме моменты времени, когда имеются имп-сы синхр-и. Так в момент времени t1 схема находится в нулевом сост-и, кот. не изменяется при подаче лог.1 на вход S . Перекл-е в единичное сост-е происх. в момент времени t2 по фронту сиг-ла синхр-и C . В момент времени t3 схема не перекл-ся в единичное сост-е, т.к.она уже в нем находится, а сиг-лы на вх. S и R остались без изменения к моменту появл-я тактового имп-са на вх. синхр-и C . В момент времени t4 сиг-лы S R 0 и схема остается в предыд. Сост-и. Перекл-е происх. лишь в момент времени t5, когда приходит тактовый имп-с C и на вх. R присутствует сигнал лог.1.

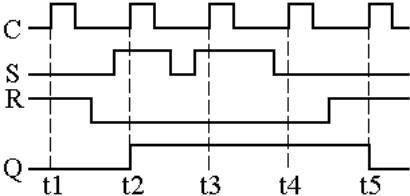

44.

Тактируемый

D-триггер. ТактируемыеD-тр-ры

могут быть с потенциальным

и динамическим

управ-ем. У

тр-ров с потенц. Упр-ем инф-я запис-ся в

теч. времени, при кот. Ур-нь сиг-ла C = 1. А

в тр-рах с динамич. Упр-ем инф-я запис-ся

только в момент перепада (фронта) напр-я

на вх. синхр-и. Тр-ры D-типа

иногда наз. тр-ми задержки. Схема D-тр-ра

сост. из синхронного RS-тр-ра

и инвертора.![]()

Благодаря

инвертору невозм. запрещ. сост-е сигн-в

на вх. R и

S.

Тр-р имеет информ-й вх. D

и вх. синхр-и

C. Если ур-нь сиг-ла на вх. C = 0, сост-е тр-ра

уст-во и не зависит от ур-ня сиг-ла на

информ-м вх. D.

При подаче на вх. синхр-и ур-ня C = 1 инф-я

на прямом вых. будет повторять инф-ю,

подаваемую на вх. D.

В D-тр-р

запис-ся та инф-я, кот.была на вх. D

в момент

прихода имп-са синхр-и, причем вых. сиг-л

Q сохр-ся

до прихода очередного имп-са синхр-и.

Благодаря

инвертору невозм. запрещ. сост-е сигн-в

на вх. R и

S.

Тр-р имеет информ-й вх. D

и вх. синхр-и

C. Если ур-нь сиг-ла на вх. C = 0, сост-е тр-ра

уст-во и не зависит от ур-ня сиг-ла на

информ-м вх. D.

При подаче на вх. синхр-и ур-ня C = 1 инф-я

на прямом вых. будет повторять инф-ю,

подаваемую на вх. D.

В D-тр-р

запис-ся та инф-я, кот.была на вх. D

в момент

прихода имп-са синхр-и, причем вых. сиг-л

Q сохр-ся

до прихода очередного имп-са синхр-и.

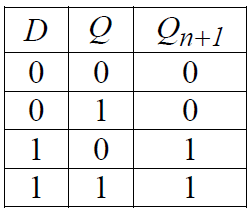

45.

Счетный Т-триггер или триггер со счетным

входом. Его

можно построить на осн. схемы тактируемого

D-тр-ра

с динамич. Синхр-ей, если его инв. Вых.

Qинв соединить с информ-м вх. D, а информ-й

сиг-л подать на вх. C.

![]() Тр-р

будет иметь один упр-щий вх. T и два вых.

Q и Qинв. Инф-я на вых. такого тр-ра меняет

свой знак на противоп. при кажд. положит.

(или при каждом отрицательном) перепаде

напр-я на вх., т.е. сост-е тр-ра меняется

на противоп. при кажд. перепаде имп-са

напр-я на вх. синхр-и C и тр-р как бы считает

проход-е имп-сы. Частота сиг-ла на вых.

Т-тр-ра

в два раза ниже частоты сиг-ла на вх.,

поэтому такой тр-р можно исп-ть как

делитель частоты, или как двоич. счетчик.

Тр-р

будет иметь один упр-щий вх. T и два вых.

Q и Qинв. Инф-я на вых. такого тр-ра меняет

свой знак на противоп. при кажд. положит.

(или при каждом отрицательном) перепаде

напр-я на вх., т.е. сост-е тр-ра меняется

на противоп. при кажд. перепаде имп-са

напр-я на вх. синхр-и C и тр-р как бы считает

проход-е имп-сы. Частота сиг-ла на вых.

Т-тр-ра

в два раза ниже частоты сиг-ла на вх.,

поэтому такой тр-р можно исп-ть как

делитель частоты, или как двоич. счетчик.

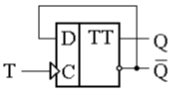

46.

Синхронный

JK-триггер имеет

такую же стр-ру, что и асинхр. Отличие

сост. в том, что вх. логич. эл-ты И

- НЕ имеют

дополнительный третий вх., на кот.подаются

тактовые имп-сы. Перекл-е тр-ра при

наличии соотв-го вх. сиг-ла происх. по

окончании тактового имп-са. На базе

синхр. JK-тр-ра

строятся: счетный(Т-тр-р)

и тр-р задержки

(D-тр-р)

(на рисунке соотв-но JK,

T

и D). Синхр.

счетный Т-тр-р

получ., объединяя информ-е вх. J

и К.

Управляющие

сиг-лы T подаются на объед-й вх., а тактовые

имп-сы на вх. C. Синхр. Тр-р задержки

(D-тр-р)

получ. путем объед-я вх. J с вх. K ч-з

инвертор.

Синхр.

счетный Т-тр-р

получ., объединяя информ-е вх. J

и К.

Управляющие

сиг-лы T подаются на объед-й вх., а тактовые

имп-сы на вх. C. Синхр. Тр-р задержки

(D-тр-р)

получ. путем объед-я вх. J с вх. K ч-з

инвертор.

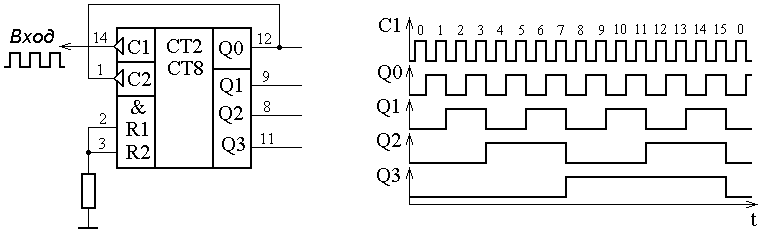

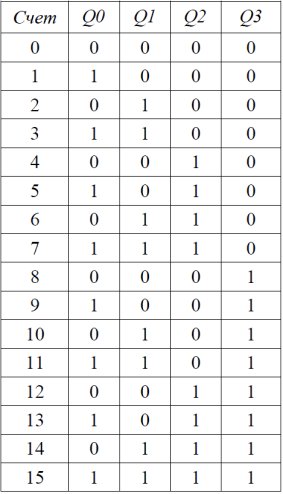

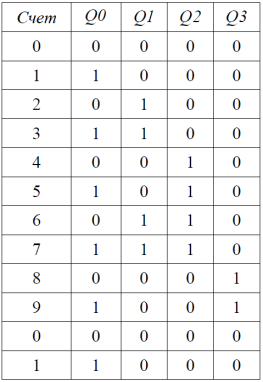

47. Счетчиком наз. устр-во, совокуп-ть сигналов на вых кот в опредном коде отображает число импульсов, поступивших на его вход. Сч-ки предст-ют собой цифровые м-схемы, имеющие внутр. память. Для созд-я сч-ков неск. триггеров Т–типа соед-ют послед-но, так, чтобы вых. предыд-го триггера был подключен к входу последующего. Кажд. триггер может принимать только два сост-я. Поэтому кол-во комбинаций вых. сигналов, снимаемых с выходов всех триггеров, а, соотв-но, и макс. кол-во подсчитанных импульсов Nmax = 2^m, где m – кол-во послед-но вкл-х триггеров. Кажд. из триггеров такой цепочки наз. разрядом сч-ка. Поэтому, если напр., m=4 , то говорят, что сч-к четырехразрядный. Макс. число, кот.может подсчитать счетчик наз. коэффициентом или модулем счета Ксч (Ксч=Nmax). Сч-к может работать на увелич-е вых. кода по кажд. входному импульсу - это основной режим, имеющийся во всех сч-ках. Этот режим наз. режимом прямого счета. Сч-к может также работать на уменьш-е вых. кода по кажд. входному импульсу - это режим обратного или инверсного счета, предусмотр-й в сч-ках, наз. реверсивными. Инверсный счет бывает довольно удобен в схемах, где необх. отсчитывать заданное кол-во входных импульсов. Счетчики подразделяются:

по коэф-ту счета: на двоичные (считают от 0 до (2^n)-1), двоично-десятичные (декадные, предельный код на вых. кот.не превыш. макс-го двоично-десятичного числа, возможного при данном кол-ве разрядов), с произв-м постоянным коэф-м счета, с переменным коэф-ом счета.

по способу организации внутренних связей между триггерами на сч-ки: с послед-м переносом (вых. сигнал кажд.

триггера служит вх. сигналом для след.триггера), с парал-м переносом (все их разряды в пределах одной м-схемы перекл-ся одноврем.), с комбинированным переносом, и кольцевые.

в зависимости от выполняемой функции: на суммирующие, вычитающие и реверсивные счетчики.

по быстродействию: асинхронные сч-ки (или послед-е), синхр-е сч-ки (или парал-е), синхр-е сч-ки с асинхр-м переносом (или парал-е сч-ки с послед-м переносом) (синхронно-асинхронные сч-ки).

48. М-сх К555ИЕ5 явл. четырехразрядным асинхронным двоичным счетчиком. Сост. из счетного триггера (вход С1 и выход Q0), работающего по mod2 (делящего сигнал на 2), и трех послед-но соединенных триггеров (вход С2), работающих по mod8, с асинхронной потенциальной установкой нулевого состояния значением сигнала . Счет до 16:

Счет до

10:![]()

Число,

записанное в счетчике и предст-ное

сочетанием лог нулей и единиц на выходах

Qm можно опред с пом-ю ур-я

Число,

записанное в счетчике и предст-ное

сочетанием лог нулей и единиц на выходах

Qm можно опред с пом-ю ур-я ![]() ,

где m

- номер триггера;

,

где m

- номер триггера; ![]() - вес соотв-го

разряда;

- вес соотв-го

разряда; ![]() - единица или ноль в завис-ти от сигнала

на соот-щем вых.

- единица или ноль в завис-ти от сигнала

на соот-щем вых.