- •7.4. Передающее устройство телесигнализации

- •Генератора тактовых импульсов

- •Логического блока

- •7.5. Приемное устройство телесигнализации

- •Сигналы на выходах триггеров дв1, дв2, двз датчика времени

- •7.6. Передающее устройство телеуправления

- •При формировании командной серии

- •7.7. Приемное устройство телеуправления

7.5. Приемное устройство телесигнализации

Кодовые серии телесигнализации по частотным каналам поступают на ДП с КП. В приемнике частотно-модулированных сигналов (ЧМС) частотные импульсы преобразуются в импульсы постоянного тока, которые поступают на линейный блок (ЛБ).

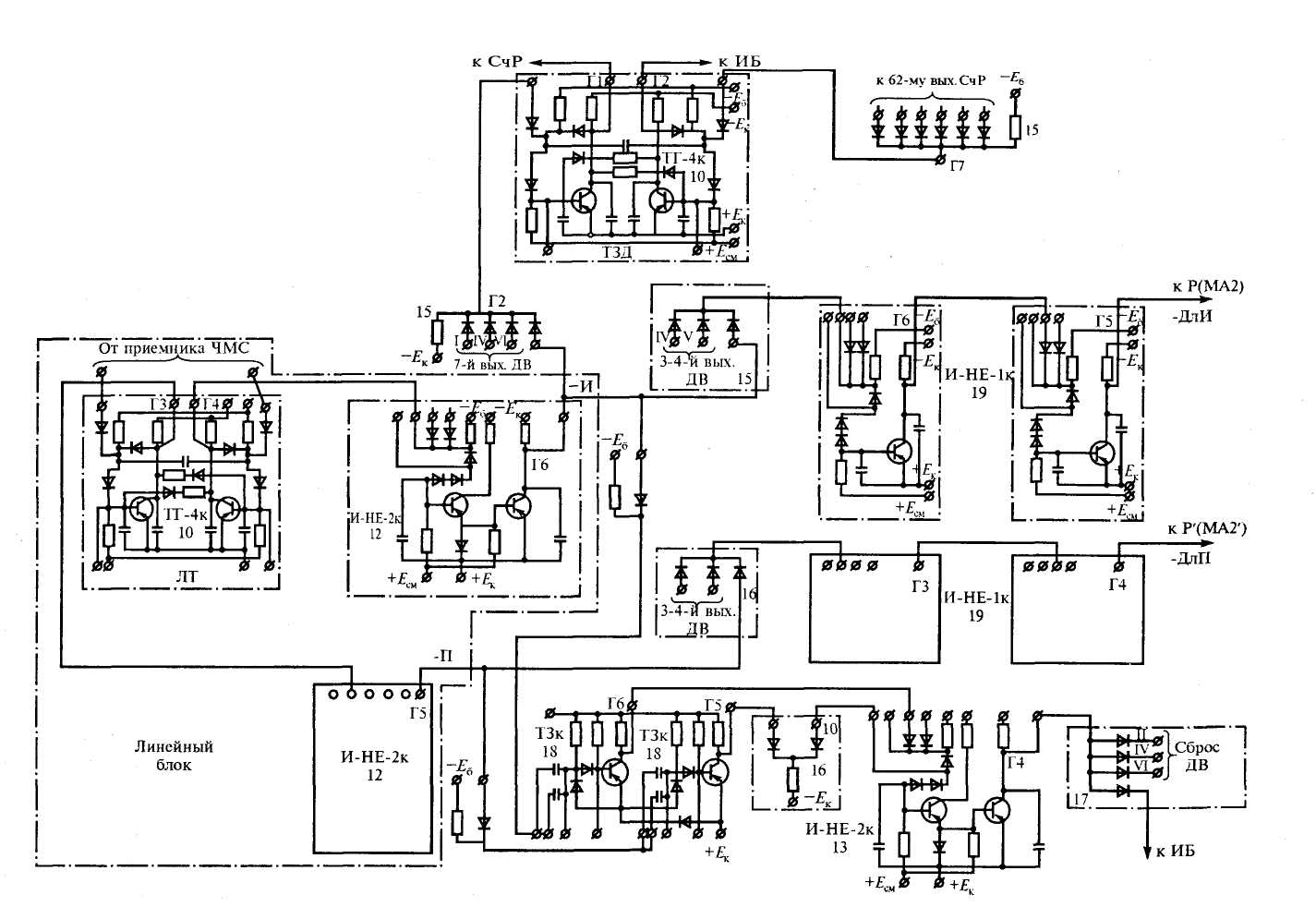

Линейный блок (ЛБ) (рис. 7.23) состоит из линейного триггера (ЛТ) и инверторов И-НЕ-2К 12(Г6) и 12(Г5). Триггер ЛТ переключается на каждом импульсе и каждой паузе, поступающим на его входы от приемника ЧМС. Одновременно с триггера ЛТ переключаются инверторы линейного блока ЛБ. Во время импульса с выхода Г4 триггера ЛТ на вход инвертора 12(Г6) поступает потенциал +ЕК, запирающий его. На выходе Г6 инвертора появляется потенциал —Ек (—И). На выходе Г5 другого инвертора линейного блока Л Б будет потенциал +ЕК (+И).

Рис. 7.23. Функциональная схема блоков селекции, синхронизации и линейного

Во время паузы на выходе ГЗ триггера ЛТ появляется потенциал +ЕК, запирающий инвертор 12(Г5), на выходе которого будет потенциал — Ек (—П). С выхода Г4 триггера ЛТ на вход инвертора 12(Г6) подается потенциал —Ек и на его выходе Г6 будет потенциал +ЕК (+П). Таким образом, инверторы ЛБ переключаются на импульсах и паузах тактовой серии и находятся постоянно в противофазе друг к другу. Их выходы Г6 и Г5 подключены к линиям задержки импульсов и пауз (ЛЗИ и ЛЗП) и к линиям, фиксирующим появление в серии длинных импульсов (ДлИ) и пауз (ДлП), выполненных на модуле И-НЕ-1К-19.

Блок синхронизации и приема данных импульсов и пауз (БСС) включает триггер задержки (ТЗД) (рис. 7.23) с управляющими диодными логическими схемами, линии задержки импульсов и пауз (ЛЗИ и ЛЗП), линии, фиксирующие появление длинных импульсов и пауз (ДлИ и ДлП) в кодовой серии и датчик времени (ДВ) мультивибратором. Датчик времени ДВ замеряет длительность импульсов и пауз: коротких — переключается один раз; длинных — 3-4 раза; на сверхдлинном импульсе делает более семи переключений.

При приеме устройством ТС ДП длинного импульса на выходе Г6 линейного блока появляется отрицательный потенциал (-И), который поступает на один из диодов логической схемы 15. На два других диода этой схемы отрицательные потенциалы поступают с датчика времени ДВ на его третьей и четвертой позициях. Как только на всех входах диодной схемы 15 собираются отрицательные потенциалы, открывается транзистор инвертора 19(Г6). Это приводит к закрытию транзистора схемы 19(Г5) и появлению на шине Р матрицы МА2 отрицательного потенциала (—ДлИ), разрешающего запись в промежуточном запоминающем устройстве (ПрЗУ) длинного импульса.

При приеме длинной паузы аналогично действует линия, фиксирующая появление длинной паузы. С выхода Г5 линейного блока ЛБ отрицательный потенциал (—П) подается на диодную схему 16. После отсчета трех импульсов с выхода датчика времени ДВ на другие два диода схемы 16 также поступают отрицательные потенциалы, происходит переключение инверторов 19 (ГЗ и Г4). На выходе инвертора 19 (Г4) появляется отрицательный потенциал (—ДлП), поступающий на шину разрешения Р' записи длинной паузы.

При приеме коротких импульсов и пауз на диодные схемы 15 и 16 с датчика времени ДВ поступает нулевой потенциал, на шинах Р и Р' будет сохраняться потенциал +ЕК, запрещающий запись.

Проверка синхронной работы распределителей устройств ТС КП и ТС ДП и их синхронизация осуществляются с помощью триггера задержки (ТЗД), на который в ; 62-й позиции распределителя через диодную схему 15(Г7) от счетчика распределителя (СчР) поступает отрицательный потенциал. Триггер ТЗД готовится к переключению (заряжается конденсатор). В 63-й позиции счетчик СчР подает через диоды схемы 15(Г7) на триггер ТЗД нулевой потенциал и переключает его из состояния 0 в состояние 1. С выхода Г1 ТЗД на счетчик СчР подается нулевой потенциал, запрещающий его переключение. Распределитель останавливается в 63-й позиции до тех пор, пока триггер ТЗД находится в состоянии 1. Если 63-й импульс тактовой серии фазирующий (сверхдлинный), то датчик времени ДВ доходит до 7-й позиции и через диодную схему 15 (Г2) на вход триггера ТЗД поступит отрицательный потенциал, разрешающий его подготовку к переключению (заряд конденсатора). На 8-й позиции датчика времени ДВ на триггер ТЗД с выхода Г2 съемы 15 поступает нулевой потенциал, переключающий его ! в состояние 0. С выхода П триггера ТЗД на счетчик СчР подается потенциал —Ек, разрешающий переключение его в последнюю 64-ю позицию.

При рассинхронизации 63-й импульс тактовой серии оказывается не сверхдлинным (коротким или длинным), датчик времени ДВ не доходит на нем до 7-й позиции и сброса триггера ТЗД не происходит. Счетчик СчР останавливается в 63-й позиции до прихода сверхдлинного импульса, на котором происходит сброс триггера ТЗД и переключение счетчика СчР в 64-ю позицию, в которой находится распределитель передающего устройства ТС. Таким образом, осуществляется синхронизация распределителей.

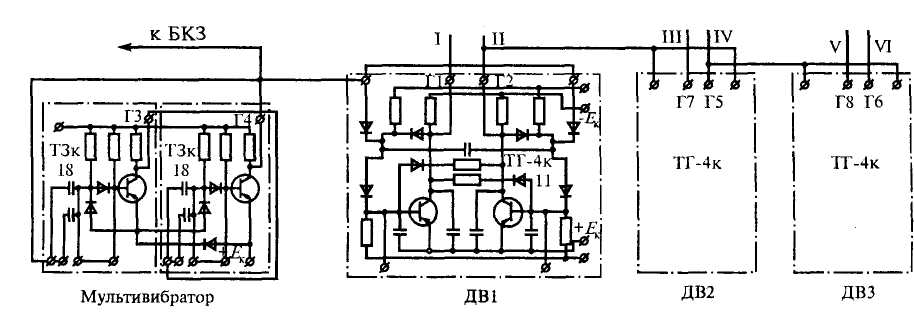

Датчик времени (ДВ) (рис. 7.24) является составной частью блока селекции и синхронизации (БСС). Он управляется мультивибратором 18(ГЗ), который является генератором тактовых импульсов (ГТИ). Измерение длительности импульсов и пауз кодовой серии, поступающей на линейный блок, производится путем отсчета числа импульсов ГТИ. В начале каждого импульса и паузы тактовой серии счетчик сбрасывается транзисторными каскадами 18 (Г6, Г5) линий задержки импульсов и пауз (см. рис. 7.23).

Рис. 7.24. Функциональная схема датчика времени блока БСС

На паузе со схемы инвертора 12(Г5) линейного блока ЛБ отрицательный потенциал поступает на конденсаторный вход каскада задержки 18(Г5), конденсатор заряжается и находится в этом состоянии до конца паузы. Во время импульса с инвертора 12(Г5) на конденсатор поступает нулевой потенциал, который приводит к разряду конденсатора на базу транзистора инвертора. Транзистор закрывается, на его выходе Г5 появляется отрицательный потенциал, поступающий на диодную схему 16. Это приводит к открытию инвертора 13(Г4) и ток по цепи эмиттер-база транзисторов протекает через резистор схемы 16. На выходе Г4 инвертора 13 возникает нулевой потенциал, поступающий через диоды схемы 17 на выходы II, IV, VI триггеров ДВ1, ДВ2, ДВЗ датчика времени (рис. 7.24), которые сбрасываются в состояние 0, а датчик — в позицию 1. Сигналы на выходах 1-V1 триггеров ДВ1—ДВЗ датчика времени в различных его позициях приведено в табл. 7.2. Как известно, полное число позиций двоичного счетчика на трех триггерах, каким является датчик времени, равняется восьми.

Таблица 7.2