- •Загальний опис сапр Electronics Workbench

- •Опис головного вікна програми сапр Electronics Workbench.

- •1.2 Бібліотека аналогових компонент Лінійні елементи

- •Нелінійні елементи

- •Біполярні транзистори.

- •Польові транзистори (fet)

- •Польові транзистори з керуючим р-n переходом (jfet)

- •1.3 Бібліотека цифрових компонент

- •Індикатори

- •Логічні елементи

- •Вузли комбінаційного типу

- •Гібридні компоненти

- •Віртуальні вимірювальні прилади сапр Electronic Workbench

- •Мультиметр

- •Генератор.

- •Осцилограф

- •Генератор слів.

- •Логічний аналізатор.

- •Проектування повного одно розрядного суматора в сапр Electronics Workbanch.

Проектування повного одно розрядного суматора в сапр Electronics Workbanch.

Одно розрядні двійкові суматори будуються по самих різних схемах. Розглянемо функціонування одно розрядного суматора, складеного з двох Непошарпаний. Непошарпаний - це пристрій, що виробляє складання двох одно розрядних двійкових чисел без урахування перенесення попереднього розряду. Складемо таблицю істинності повного одно розрядного двійкового суматора:

№ |

Ai |

Bi |

Pi-1 |

Pi |

Si |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

2 |

0 |

1 |

0 |

0 |

1 |

3 |

0 |

1 |

1 |

1 |

0 |

4 |

1 |

0 |

0 |

0 |

1 |

5 |

1 |

0 |

1 |

1 |

0 |

6 |

1 |

1 |

0 |

1 |

0 |

7 |

1 |

1 |

1 |

1 |

1 |

Табл. 3.1. Таблиця істинності для повного одно розрядного суматора.

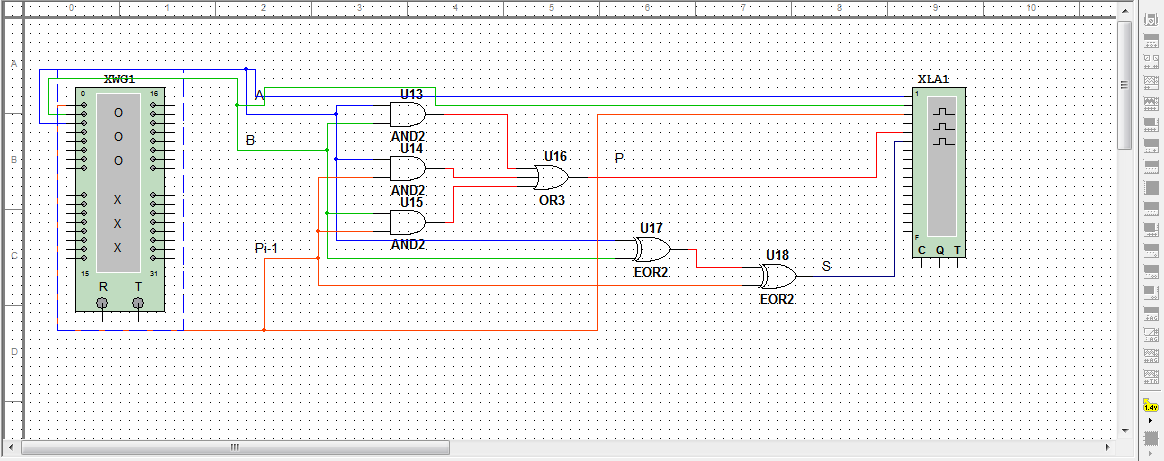

Схема повного одно розрядного суматора наведена на Рисунку 3.1. Показати самостійно, що для отримання переносу в повному одно розрядному двійковому суматорі необхідно сигнали переносів подати на входи логічного елемента 2-АБО, на виході якого вийде перенесення з повного одно розрядного двійкового суматора.

Для того щоб перевірити роботу суматора вводимо двійковий код з таблиці істинності в генератор слів (рис. 3.2.).

Рис. 3.1. Схема повного одно розрядного двійкового суматора в вікні Workbench.

Рис 3.2. Введення коду в генератор слів.

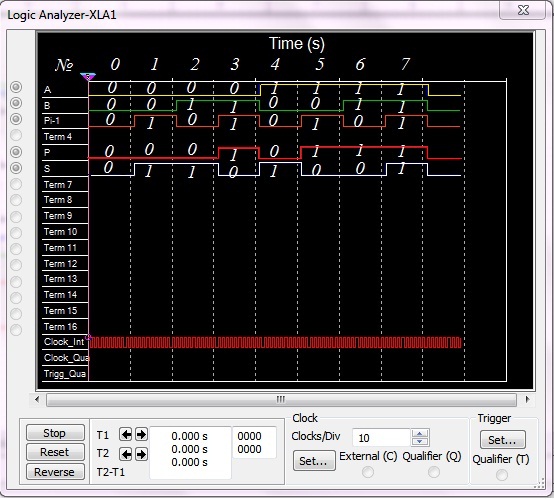

На

виході нашої схеми підключаємо логічний

аналізатор для перевірки правильності

роботи суматора:

На

виході нашої схеми підключаємо логічний

аналізатор для перевірки правильності

роботи суматора:

Рис 3.3. Покази логічного аналізатора.

Покази логічного аналізатора збігаються з таблицею істинності. Отже суматор спроектований правильно.

Висновки

В цій курсовій роботі я розглянув роботу САПР Electronics Workbanch, основні бібліотеки елементів програми. Було вивчено більшість аналогових та цифрових компонент, які умовно можна розділити на: джерела, лінійні та нелінійні компоненти, ключі та індикатори, логічні компоненти, вузли комбінаційного та послідовного типів, логічні та гібридні компоненти.

Також була розглянута робота віртуальних приладів які використовуються в програмі. Проведено проектування повного одно розрядного двійкового суматора на основі логічних елементів. Цю схему було перевірено за допомогою генератора слів, з якого подавалися логічні сигнали на: a, b Pi-1входи схеми, та логічного аналізатора, на якому фіксувалися сигнали з P та S виходів схеми.

Workbench є зручним для логічного моделювання цифрових пристроїв для початківців, в тому числі і для студентів, він представляє значні труднощі в освоєнні. Особливістю програми є наявність контрольно-вимірювальних приладів, за зовнішнім виглядом і характеристиками наближених до їх промисловим аналогам. Програма легка в освоєнні і досить зручна в роботі.

Література

1. Файл довідка Electronics workbench 5.0C;

2. Кучеренко М., Щерба А. Комп’ютерні технології в електроніці та електротехніці (2003)

3. Жабін В. І., Жуков І. А.. - Прикладна теорія цифрових автоматів (2009)

4. Современная система комп’ютерного моделирования и анализа схем электронных устройств - Марк Е. Хернитер (Marc E. Herniter) Издательский дом «ДМК)пресс» Москва, 2006