- •Лекция №1 литература.

- •План лекции

- •Самостоятельная проработка

- •Введение

- •1. Назначение и краткий обзор развития схемотехники эвм(5 проблем)

- •2. Активны и пассивные элементы схемотехники

- •4. Понятие блок-схемы, функциональной и принципиальной схемы

- •5.Условные обозначения схемотехнических элементов

- •Лекция №2 План лекции.

- •3. Формы представления информации

- •4. Входной контроль

- •1 Краткий словарь схемотехники

- •2. Функциональная схема эвм и принцип ее работы

- •3. Формы представления информации

- •Лекция №3 план лекции

- •Функциональные узлы эвм

- •2 Формирование и преобразование сигналов

- •Дифференцирующие цепи

- •Оперативное запоминающее устройство

- •Устройство управления

- •Арифметическое устройство

- •Самостоятельная работа формирование и преобразование сигналов Дифференцирующие цепи

- •Интегрирующие цепи (иц)

- •Лекция №4 план лекции

- •Код. Кодирование. Способы кодирования

- •Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Двоичное кодирование графической информации

- •2. Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Кодирование графической информации

- •Изображения растровые векторные

- •Кодирование векторных изображений.

- •Лекция №5

- •5.1 Логическое отрицание не

- •5.2 Логическое умножение и

- •5.3 Логическая функция сложения или

- •5.4 Функция Шеффера

- •5.5 Стрелка Пирса

- •5.6 Исключающее или

- •5.7 Эквивалентность

- •5.8 Импликация

- •Лекция №6а план лекции

- •Этапы развития логики

- •Законы алгебры логики

- •Законы алгебры логики

- •Лекция №7 минимизация функции

- •Самостоятельная работа Минимизация логической функции

- •Лекция №8-9 план лекции

- •1.Принцип работы полупроводниковых устройств

- •2. Потенциальные системы схем эвм

- •Рассмотрим принцип работы транзистора

- •Инвертор

- •Транзисторная логика(самостоятельная работа)

- •Лекция №10 схемотехника транзисторно-транзисторнй логики (ттл)

- •Лекция №11

- •2. Схемотехника ис инжекционной логики--иил (и2л)

- •Схемотехника ис инжекционной логики и2л

- •Лекция 12

- •Схемотехника транзисторной логики со связанными эмиттерами(эстл).

- •2. Схемотехника ис на полевых транзисторах (пт)

- •Схемотехника ис на полевых транзисторах (пт)

- •Лекция №12а схемотехника цифровых элементов

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №13

- •10.0 Основные динамические параметры интегральных схем потенциального типа

- •Самостоятельная работа Развитие схем потенциального типа

- •10.2 Таблица сравнения цифровых интегральных микросхем

- •Лекция №13а схемотехника цифровых элементов

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №14

- •11.0 Регистры хранения и сдвига

- •11.1 Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №14а универсальные jk триггеры

- •9.7 Триггер Шмитта – (тл)

- •Лекция №15 универсальные регистры

- •Лекция №17(самотоятельно) кольцевой счетчик

- •12.3 Делители частоты

- •Лекция №18a синхронный (тактируемый) rs, d и т триггеры

- •Выходной сигнал q сохраняется до прихода очередного тактового импульса. Причем эта информация хранится в d-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти.

- •Лекция №20 регистры хранения и сдвига

- •Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №21 план лекции

- •Реверсивные счетчики (рс)

- •Кольцевой счетчик

- •Делители частоты(Самостоятельно)

- •Лекция №23 преобразователи кодов

- •Лекция №24 дешифраторы decoder (dc)

- •Контрольная работа Используя таблицу истинности составить временные диаграммы дешифратора 2х4

- •Лекция №25

- •Пример сети с двумя типами мультиплексоров самостоятельная работа

- •Лекция №26 демультиплексоры

- •Лекция №27 сумматоры и алу

- •Контрольная работа

- •Лекция №28 сумматоры и алу

- •Лекция №29-30 схемотехника обслуживающих элементов Генераторы и формирователи импульсов

- •Формирователи импульсов

- •Лекция №28 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №31 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №32-33 компараторы и таймеры

- •Цифро-аналоговые и аналого-цифровые преобразователи

Контрольная работа

Перевести в двоичную систему год свого рождения и возраст.

Сложить эти два числа в двоичной системе счисления.

Полученное число в двоично-десятичную и троичную систему счисления

Лекция №28 сумматоры и алу

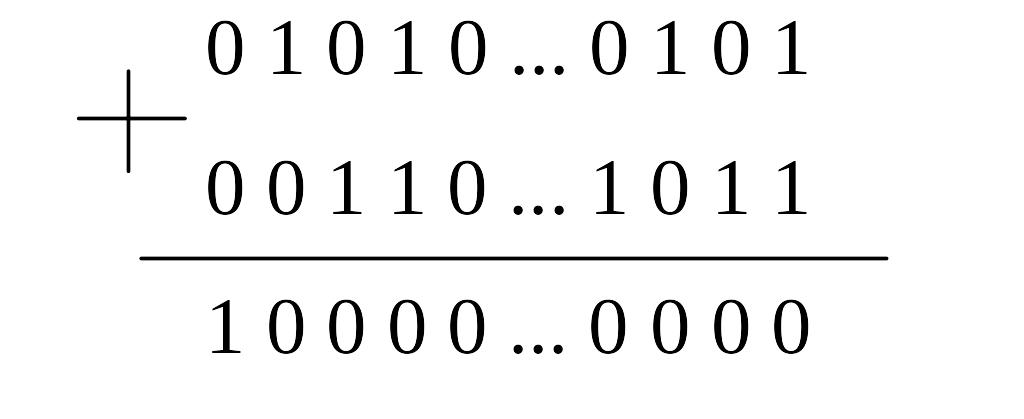

Для сложения двух многоразрядных двоичных чисел используют многоразрядные сумматоры, представляющие собой в простейшем виде соединение одноразрядных сумматоров.

Рис. Параллельный n-разрядный сумматор

Таким образом, получаем параллельный n-разрядный сумматор.

Рассмотрим пример сложения 2-х операндов Хi=00101 и Уi=0011

1-ый сумматор

1+1

2-ой сумматор

1+0+1

3-ий сумматор

1+1+0

4-ый сумматор

1+0+0

У1

Х1

Х3

Х4

У2

У3

У4

Процедура

суммирования двух 4-х разрядных чисел

показана на функциональной схеме

параллельного

сумматора и имеет следующий вид.

Pi

1

1 1

Хi

0

0 1 0 1

Yi

0 0 1 1

0

1 0 0 0

Х2

Функциональная cхема работы параллельного сумматора.

Основными характеристиками сумматора являются разрядность и быстродействие. Очевидно, что при увеличении разрядности сумматора быстродействие уменьшается. Очевидно и другое: что для увеличения быстродействия необходимо уменьшить время распространения переноса через все разряды суммируемых кодов, а также уменьшить общее время задержки ts.

В настоящее время реализована организация группового переноса, при котором ts=(n/2)tзд.р, где n-разряды суммируемых кодов.

Сумматоры с одновременным переносом реализованы в виде специальных микросхем. Например: К155ИП3, К155ИП4, К500ИП181, К500ИП179 и т.д.

Рассмотрим возможность ИС К155ИП3.

Рис. Интегральная схема К155ИП3

Yi, Xi – информационные входы;

Vi – управляющие входы;

М – управляющий вход, определяющий режим работы сумматора (арифметический или логический);

Рвх, Р, и Ргр – входы и выходы одновременного переноса;

Xi-Yi – отдельный выход;

Fi – выходные сигналы, результаты арифметических или же логических операций;

15, 16, 17 – выходы одновременного переноса.

При М=1 ИС выполняет 8 логических функций;

М=0 – 8 арифметических функций.

Микросхема может работать в режиме положительной и отрицательной логики. На основе данной микросхемы легко реализуется n-разрядный сумматор. При этом не требуется дополнительного оборудования. Максимальное время суммирования n-разрядных кодов (n=40) равно 119 нс.

Конкретный пример:

Эта же микросхема может выполнить функцию 4-разрядного АЛУ. Графическое обозначение приведено на рисунке выше, где Х4-Х1 и Y4-Y1 – 4-х разрядные информационные коды; F4..F1 – 4-х разрядный код результата логической или арифметической операции, выполняемой схемой; V4..V1 – код управляющих сигналов.Возможны 24=16 комбинаций управляющих сигналов, каждая из которых определяет выполняемую схемой арифметическую или логическую операцию; М – управляющий сигнал, определяющий режим работы схемы логических или арифметических операций; Рвх, Р, и Ргр – входы и выходы одновременного переноса; хi-yi – отдельный выход, имеющийся только в схеме К155ИП3, сигнал на котором появляется лишь в случае идентичности входных кодов при любом значении М.

При М=1 выполняются логические функции (8), столько же функций выполняется арифметических при М=0 как при положительной, так и при отрицательной логике.

ИС серии К155 и К500 являются основными при построении АЛУ в больших ЭВМ.

4-х разрядный полный сумматор

Рис. 4-хразрядный полный сумматор

Для увеличения разрядности сумматора применяется способ наращивания.

Например, для сложения двух 8-разрядных двоичных чисел, разумеется, нужны два

4-хразрядные сумматоры.

При этом схема выглядит следующим образом:

Рис. Сложение двух 8-разрядных двоичных чисел