- •Лекция №1 литература.

- •План лекции

- •Самостоятельная проработка

- •Введение

- •1. Назначение и краткий обзор развития схемотехники эвм(5 проблем)

- •2. Активны и пассивные элементы схемотехники

- •4. Понятие блок-схемы, функциональной и принципиальной схемы

- •5.Условные обозначения схемотехнических элементов

- •Лекция №2 План лекции.

- •3. Формы представления информации

- •4. Входной контроль

- •1 Краткий словарь схемотехники

- •2. Функциональная схема эвм и принцип ее работы

- •3. Формы представления информации

- •Лекция №3 план лекции

- •Функциональные узлы эвм

- •2 Формирование и преобразование сигналов

- •Дифференцирующие цепи

- •Оперативное запоминающее устройство

- •Устройство управления

- •Арифметическое устройство

- •Самостоятельная работа формирование и преобразование сигналов Дифференцирующие цепи

- •Интегрирующие цепи (иц)

- •Лекция №4 план лекции

- •Код. Кодирование. Способы кодирования

- •Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Двоичное кодирование графической информации

- •2. Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Кодирование графической информации

- •Изображения растровые векторные

- •Кодирование векторных изображений.

- •Лекция №5

- •5.1 Логическое отрицание не

- •5.2 Логическое умножение и

- •5.3 Логическая функция сложения или

- •5.4 Функция Шеффера

- •5.5 Стрелка Пирса

- •5.6 Исключающее или

- •5.7 Эквивалентность

- •5.8 Импликация

- •Лекция №6а план лекции

- •Этапы развития логики

- •Законы алгебры логики

- •Законы алгебры логики

- •Лекция №7 минимизация функции

- •Самостоятельная работа Минимизация логической функции

- •Лекция №8-9 план лекции

- •1.Принцип работы полупроводниковых устройств

- •2. Потенциальные системы схем эвм

- •Рассмотрим принцип работы транзистора

- •Инвертор

- •Транзисторная логика(самостоятельная работа)

- •Лекция №10 схемотехника транзисторно-транзисторнй логики (ттл)

- •Лекция №11

- •2. Схемотехника ис инжекционной логики--иил (и2л)

- •Схемотехника ис инжекционной логики и2л

- •Лекция 12

- •Схемотехника транзисторной логики со связанными эмиттерами(эстл).

- •2. Схемотехника ис на полевых транзисторах (пт)

- •Схемотехника ис на полевых транзисторах (пт)

- •Лекция №12а схемотехника цифровых элементов

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №13

- •10.0 Основные динамические параметры интегральных схем потенциального типа

- •Самостоятельная работа Развитие схем потенциального типа

- •10.2 Таблица сравнения цифровых интегральных микросхем

- •Лекция №13а схемотехника цифровых элементов

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №14

- •11.0 Регистры хранения и сдвига

- •11.1 Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №14а универсальные jk триггеры

- •9.7 Триггер Шмитта – (тл)

- •Лекция №15 универсальные регистры

- •Лекция №17(самотоятельно) кольцевой счетчик

- •12.3 Делители частоты

- •Лекция №18a синхронный (тактируемый) rs, d и т триггеры

- •Выходной сигнал q сохраняется до прихода очередного тактового импульса. Причем эта информация хранится в d-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти.

- •Лекция №20 регистры хранения и сдвига

- •Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №21 план лекции

- •Реверсивные счетчики (рс)

- •Кольцевой счетчик

- •Делители частоты(Самостоятельно)

- •Лекция №23 преобразователи кодов

- •Лекция №24 дешифраторы decoder (dc)

- •Контрольная работа Используя таблицу истинности составить временные диаграммы дешифратора 2х4

- •Лекция №25

- •Пример сети с двумя типами мультиплексоров самостоятельная работа

- •Лекция №26 демультиплексоры

- •Лекция №27 сумматоры и алу

- •Контрольная работа

- •Лекция №28 сумматоры и алу

- •Лекция №29-30 схемотехника обслуживающих элементов Генераторы и формирователи импульсов

- •Формирователи импульсов

- •Лекция №28 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №31 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №32-33 компараторы и таймеры

- •Цифро-аналоговые и аналого-цифровые преобразователи

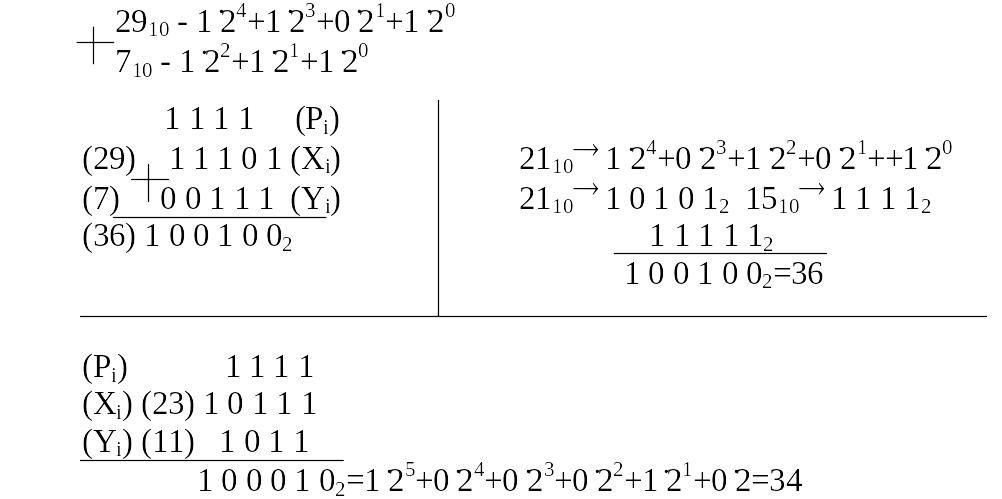

Лекция №27 сумматоры и алу

Сумматор — логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и т д. Указанные операции выполняются в арифметическо-логических устройствах (АЛУ) или процессорных элементах, ядром которых являются сумматоры.

С

КЛАССИФИКАЦИЯ СУММАТОРОВ

ПО СИСТЕМЕ

СЧИСЛЕНИЯ

ПО АРХИТЕКТУРЕ

ПО ПЕРЕНОСУ

ПО ЧИСЛУ ОПЕРАНДОВ

Двоичные

Двоично-десятич.

Десятичные

Прочие

Четвертсумматоры

Полусумматоры

Полные сумматоры

С последовательн.

С паралеллным

С групповым переносом

Бинарные

Тринарные n-арные

умматоры

классифицируют по различным признакам.

умматоры

классифицируют по различным признакам.

четвертьсумматоры, характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (старший разряд);

полные сумматоры, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд). Такие сумматоры изначально ориентированы только на показательные позиционные системы счисления.

Основной арифметической операцией, выполняемой любой ЭВМ, является операция суммирования двух n-разрядных кодов (х1...хn и у1...уn). Суммирование во всех разрядах, начиная с младшего, происходит по единым правилам. В каждом i-м разряде осуществляется сложение хi+yi+Pi, где Pi – перенос из младшего i-го в старший разряд. Результат представляется кодами суммы Si и переноса Pi+1.

Таким образом, сумматор предназначен для арифметического сложения двух чисел. Из принципа сложения многоразрядных двоичных чисел следует, что в каждом i-м разряде находится сумма трех чисел по модулю 2 (слагаемых хi, yi и переноса, поступающего из младшего разряда Pi), и формируется сигнал переноса в старший разряд Pi+1.

Для примера проанализируем таблицу истинности одноразрядного сумматора и запишем логические выражения для выходных величин.

|

Вход |

Выход |

|||

слагаемое |

перенос |

слагаемое |

перенос |

||

i |

Хi |

Yi |

Pi |

Si |

Pi+1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

2 |

0 |

1 |

0 |

1 |

0 |

3 |

1 |

1 |

0 |

0 |

1 |

4 |

0 |

0 |

1 |

1 |

0 |

5 |

1 |

0 |

1 |

0 |

1 |

6 |

0 |

1 |

1 |

0 |

1 |

7 |

1 |

1 |

1 |

1 |

1 |

Логические выражения для выходных величин (формулы Si и Pi+1 получены из таблицы, где значения Si и Pi=1):

![]() ;

;

![]() .

.

В таблице столбцы Si и Pi+1 заполняются по следующим условиям:

Pi+1=1, если не менее 2-х чисел (Xi, Yi,, Pi)=1;

Si=1, если нечетное число величин Хi, Yi, Pi.

Исходя из этих условий, формируется выше представленная таблица истинности работы одноразрядного сумматора.

При разработке функциональной схемы соединение выходов конъюнктора к дизъюнктору определяется из таблицы истинности и согласно характеристическим уравнениям Si и Pi+1. При этом единица означает, что на вход N должны подать для канала Si и Pi+1. Именно те сигналы, где выход равен 1. Например:

По этим функциям можно построить сумматор на элементах И и ИЛИ.

Рис. Сумматор