- •Лекция №1 литература.

- •План лекции

- •Самостоятельная проработка

- •Введение

- •1. Назначение и краткий обзор развития схемотехники эвм(5 проблем)

- •2. Активны и пассивные элементы схемотехники

- •4. Понятие блок-схемы, функциональной и принципиальной схемы

- •5.Условные обозначения схемотехнических элементов

- •Лекция №2 План лекции.

- •3. Формы представления информации

- •4. Входной контроль

- •1 Краткий словарь схемотехники

- •2. Функциональная схема эвм и принцип ее работы

- •3. Формы представления информации

- •Лекция №3 план лекции

- •Функциональные узлы эвм

- •2 Формирование и преобразование сигналов

- •Дифференцирующие цепи

- •Оперативное запоминающее устройство

- •Устройство управления

- •Арифметическое устройство

- •Самостоятельная работа формирование и преобразование сигналов Дифференцирующие цепи

- •Интегрирующие цепи (иц)

- •Лекция №4 план лекции

- •Код. Кодирование. Способы кодирования

- •Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Двоичное кодирование графической информации

- •2. Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Кодирование графической информации

- •Изображения растровые векторные

- •Кодирование векторных изображений.

- •Лекция №5

- •5.1 Логическое отрицание не

- •5.2 Логическое умножение и

- •5.3 Логическая функция сложения или

- •5.4 Функция Шеффера

- •5.5 Стрелка Пирса

- •5.6 Исключающее или

- •5.7 Эквивалентность

- •5.8 Импликация

- •Лекция №6а план лекции

- •Этапы развития логики

- •Законы алгебры логики

- •Законы алгебры логики

- •Лекция №7 минимизация функции

- •Самостоятельная работа Минимизация логической функции

- •Лекция №8-9 план лекции

- •1.Принцип работы полупроводниковых устройств

- •2. Потенциальные системы схем эвм

- •Рассмотрим принцип работы транзистора

- •Инвертор

- •Транзисторная логика(самостоятельная работа)

- •Лекция №10 схемотехника транзисторно-транзисторнй логики (ттл)

- •Лекция №11

- •2. Схемотехника ис инжекционной логики--иил (и2л)

- •Схемотехника ис инжекционной логики и2л

- •Лекция 12

- •Схемотехника транзисторной логики со связанными эмиттерами(эстл).

- •2. Схемотехника ис на полевых транзисторах (пт)

- •Схемотехника ис на полевых транзисторах (пт)

- •Лекция №12а схемотехника цифровых элементов

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №13

- •10.0 Основные динамические параметры интегральных схем потенциального типа

- •Самостоятельная работа Развитие схем потенциального типа

- •10.2 Таблица сравнения цифровых интегральных микросхем

- •Лекция №13а схемотехника цифровых элементов

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №14

- •11.0 Регистры хранения и сдвига

- •11.1 Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №14а универсальные jk триггеры

- •9.7 Триггер Шмитта – (тл)

- •Лекция №15 универсальные регистры

- •Лекция №17(самотоятельно) кольцевой счетчик

- •12.3 Делители частоты

- •Лекция №18a синхронный (тактируемый) rs, d и т триггеры

- •Выходной сигнал q сохраняется до прихода очередного тактового импульса. Причем эта информация хранится в d-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти.

- •Лекция №20 регистры хранения и сдвига

- •Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №21 план лекции

- •Реверсивные счетчики (рс)

- •Кольцевой счетчик

- •Делители частоты(Самостоятельно)

- •Лекция №23 преобразователи кодов

- •Лекция №24 дешифраторы decoder (dc)

- •Контрольная работа Используя таблицу истинности составить временные диаграммы дешифратора 2х4

- •Лекция №25

- •Пример сети с двумя типами мультиплексоров самостоятельная работа

- •Лекция №26 демультиплексоры

- •Лекция №27 сумматоры и алу

- •Контрольная работа

- •Лекция №28 сумматоры и алу

- •Лекция №29-30 схемотехника обслуживающих элементов Генераторы и формирователи импульсов

- •Формирователи импульсов

- •Лекция №28 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №31 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №32-33 компараторы и таймеры

- •Цифро-аналоговые и аналого-цифровые преобразователи

Пример сети с двумя типами мультиплексоров самостоятельная работа

Составить таблицу истинности и уравнение мультиплексора КП-7, затем разработать функциональную схему мультиплексора с 8-ю информационными и 3-я адресными входами.

Рис. Схема и условное обозначение микросхемы 155КП7

Лекция №26 демультиплексоры

Демультиплексоры –это комбинационная схема, имеющая один информационный вход (х1), N информационных выходов Fi (F1…Fn) и ki управляющих входов Vk-V1. Следовательно, выполняют функцию, обратную функции мультиплексоров. Так же как и у мультиплексоров количество информационных выходов определяется N=2к.

Демультиплексор — устройство, в котором сигналы с одного информационного входа поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры обозначают через DMX или DMS. Если между числом выходов и числом адресных входов действует соотношение n=2k для двоичных демультиплексоров или n=3k для троичных демультиплексоров, то такой демультиплексор называют полным. Если n<2k для двоичных демультиплексоров или n<3k для троичных демультиплексоров, то демультиплексор называют неполным. Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора. Таким образом, демультиплексорами называются устройства, которые позволяют подключать один вход к нескольким выходам. Демультиплексоры можно построить на основе точно таких же схем логического "И", как и при построении мультиплексора. Существенным отличием от мультиплексора является возможность объединения нескольких входов в один без дополнительных схем. Однако для увеличения нагрузочной способности микросхемы, на входе демультиплексора, для усиления входного сигнала, лучше поставить инвертор.

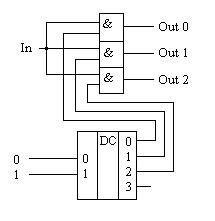

Схема демультиплексора приведена на рисунке. В этой схеме для выбора конкретного выхода демультиплексора, как и в мультиплексоре, используется двоичный дешифратор.

Принципиальная схема демультиплексора, управляемого двоичным кодом.

Демультиплексоры эффективно используются для преобразования последовательного кода в параллельный.

Рассмотрим пример совместного использования мультиплексора с демультиплексором, что обеспечивает последовательную передачу информации с преобразованием параллельного кода в последовательный и последовательный в параллельный.

Рис. Мультиплексор с демультиплексором

В настоящее время в качестве коммутаторов (мультиплексоров) выпускаются в составе серийных ИС серии 155, 561, 500.

Например:

К155КП5 – коммутатор 8 каналов без стробирования;

К155КП7 – 8 каналов со стробированием К155КП2 – сдвоенный цифровой селектор – мультиплексор; К155ИД3 – дешифратор-демультиплексор 4 линии на 16.

Демультиплекоры-селекторы являются многофункциональным узлом ЭВМ. Широкие возможности представляют разработчику мультиплексор-селектор (демультиплексор) на КМОП структурах.

На рисунке приведена схема и условное функциональное обозначение микросхемы 564КП2.

Рис. Схема и условное функциональное обозначение микросхемы 564КП2

При v=0 (вход стробсигнала) и при соответствующем значении адресов а4, а2, а1 один из восьми выходов дешифратора-селектора открывает соответствующий двунаправленный ключ "КЛ", обеспечивая связь выхода (У) с информационными выходами Di.

При V=1 все "КЛ" – закрыты.

Данная схема может работать в качестве дешифратора (ИД), мультиплексора и селектора (демультиплексора).

При работе в качестве демультиплексора адресными входами являются аi, информационными входами – y, а выходами – Di. Если же используется в качестве мультиплексора, то адресные – аi, входы – Di, выход – y.

Дешифратор – с активным уровнем выходов "1" необходимо присоединить Yk источник питания (Uпит), а Di через резистор 20 кОм к Земле.

При дешифрации к активным уровням "0" У – к Земле Di через 20 кОм к Uпит. Входами дешифраторов при этом являются а4, а2, а1, а выходами – Di.