- •Лекция №1 литература.

- •План лекции

- •Самостоятельная проработка

- •Введение

- •1. Назначение и краткий обзор развития схемотехники эвм(5 проблем)

- •2. Активны и пассивные элементы схемотехники

- •4. Понятие блок-схемы, функциональной и принципиальной схемы

- •5.Условные обозначения схемотехнических элементов

- •Лекция №2 План лекции.

- •3. Формы представления информации

- •4. Входной контроль

- •1 Краткий словарь схемотехники

- •2. Функциональная схема эвм и принцип ее работы

- •3. Формы представления информации

- •Лекция №3 план лекции

- •Функциональные узлы эвм

- •2 Формирование и преобразование сигналов

- •Дифференцирующие цепи

- •Оперативное запоминающее устройство

- •Устройство управления

- •Арифметическое устройство

- •Самостоятельная работа формирование и преобразование сигналов Дифференцирующие цепи

- •Интегрирующие цепи (иц)

- •Лекция №4 план лекции

- •Код. Кодирование. Способы кодирования

- •Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Двоичное кодирование графической информации

- •2. Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Кодирование графической информации

- •Изображения растровые векторные

- •Кодирование векторных изображений.

- •Лекция №5

- •5.1 Логическое отрицание не

- •5.2 Логическое умножение и

- •5.3 Логическая функция сложения или

- •5.4 Функция Шеффера

- •5.5 Стрелка Пирса

- •5.6 Исключающее или

- •5.7 Эквивалентность

- •5.8 Импликация

- •Лекция №6а план лекции

- •Этапы развития логики

- •Законы алгебры логики

- •Законы алгебры логики

- •Лекция №7 минимизация функции

- •Самостоятельная работа Минимизация логической функции

- •Лекция №8-9 план лекции

- •1.Принцип работы полупроводниковых устройств

- •2. Потенциальные системы схем эвм

- •Рассмотрим принцип работы транзистора

- •Инвертор

- •Транзисторная логика(самостоятельная работа)

- •Лекция №10 схемотехника транзисторно-транзисторнй логики (ттл)

- •Лекция №11

- •2. Схемотехника ис инжекционной логики--иил (и2л)

- •Схемотехника ис инжекционной логики и2л

- •Лекция 12

- •Схемотехника транзисторной логики со связанными эмиттерами(эстл).

- •2. Схемотехника ис на полевых транзисторах (пт)

- •Схемотехника ис на полевых транзисторах (пт)

- •Лекция №12а схемотехника цифровых элементов

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №13

- •10.0 Основные динамические параметры интегральных схем потенциального типа

- •Самостоятельная работа Развитие схем потенциального типа

- •10.2 Таблица сравнения цифровых интегральных микросхем

- •Лекция №13а схемотехника цифровых элементов

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №14

- •11.0 Регистры хранения и сдвига

- •11.1 Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №14а универсальные jk триггеры

- •9.7 Триггер Шмитта – (тл)

- •Лекция №15 универсальные регистры

- •Лекция №17(самотоятельно) кольцевой счетчик

- •12.3 Делители частоты

- •Лекция №18a синхронный (тактируемый) rs, d и т триггеры

- •Выходной сигнал q сохраняется до прихода очередного тактового импульса. Причем эта информация хранится в d-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти.

- •Лекция №20 регистры хранения и сдвига

- •Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №21 план лекции

- •Реверсивные счетчики (рс)

- •Кольцевой счетчик

- •Делители частоты(Самостоятельно)

- •Лекция №23 преобразователи кодов

- •Лекция №24 дешифраторы decoder (dc)

- •Контрольная работа Используя таблицу истинности составить временные диаграммы дешифратора 2х4

- •Лекция №25

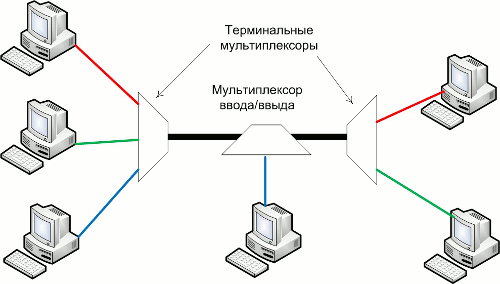

- •Пример сети с двумя типами мультиплексоров самостоятельная работа

- •Лекция №26 демультиплексоры

- •Лекция №27 сумматоры и алу

- •Контрольная работа

- •Лекция №28 сумматоры и алу

- •Лекция №29-30 схемотехника обслуживающих элементов Генераторы и формирователи импульсов

- •Формирователи импульсов

- •Лекция №28 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №31 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №32-33 компараторы и таймеры

- •Цифро-аналоговые и аналого-цифровые преобразователи

Лекция №25

МУЛЬТИПЛЕКСОРЫ (КОММУТАТОРЫ)

Мультиплексор представляет собой узел ЭВМ, осуществляющий преобразование параллельных цифровых кодов в последовательные и применяются для последовательного опроса заданного числа информационных сигналов и передачи их на один выход.

Следовательно, мультиплексор – это комбинационная многовходовая схема с одним выходом F1. Входы при этом делятся на информационные (Х1...Хn) и управляющие (A1...AK).

Количество управляющих(k) и информационных входов (n) определяются как n=2 k .

Обычно, мультиплексор имеет 3 группы входов : 1)информационные(D), 2)адресные(A) – двоичный код, на котором определяется какой из информационных входов подключен к выходу; 3) стробирующий(С) (разрешающий). Стробирование – метод выделения из последовательности импульсов лишь те, которые отличаются либо амплитудой или длительностью, либо же положением на временной оси.

Код, поступающий на управляющие входы, определяет один из информационных входов, значение переменной которого передается на выход Fi.

Для разработки схемы мультиплексора составим таблицу истинности с учетом всех сигналов(информационных-Xi и управляющих-Ai).

УПРАВЛЯЮЩИЕ СИГНАЛЫ |

ИНФОРМАЦИОННЫЕ СИГНАЛЫ |

ФУНКЦИЯ |

|

A1 |

A2 |

Xi |

Fi |

0 |

0 |

X1 |

X1* |

0 |

1 |

X2 |

X2* |

1 |

0 |

X3 |

X3* |

1 |

1 |

X4 |

X4*A1*A2 |

Из таблицы получим характеристическое уравнение мультиплексора.

Fi= (X1* )v( X2* )v(X3* )v(X4*A1*A2)

A1 |

A2 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

Вариант реализации мультиплексора (n=4, k=2) и его условное графическое обозначение представлены на рисунке ниже. Здесь мультиплексор построен как совокупность двухвходовых коньюнкторов (их число равно числу информационных входов =4). В качестве управляющих сигналов используют выходные сигналы дешифратора, дешифрирующего двоичный управляющий код. Выходы конъюнкторов объединены схемой ИЛИ.

Используя таблицу истинности, либо характеристическое уравнение, составим функциональную схему мультиплексора.

Функциональная схема мультиплексора (n=4, k=2) и его условное графическое обозначении.

Рассмотрим вариант, где в качестве дешифратора используется два инвертора(НЕ) при этом в качестве разрешающего сигнала используется стробирующий вход С.

На рисунке приведена схема мультиплексора с четырьмя информационными и с двумя адресными входами. Для передачи входной логической информации Di необходимо подать на вход адресный код А1, А2. При этом выходной сигнал является функцией входных логических переменных, адресов (А1, А2) и стробсигнала С:

Рис. Схема мультиплексора с четырьмя информационными, с двумя адресными и стробирующими входами

Количество информационных входов можно увеличить, но при этом необходимо увеличить и количество адресных входов.

Мультиплексоры применяются как проводных, так и беспроводных каналов передачи информации.

Мультиплексоры бывают терминальные и ввода/вывода. Терминальные мультиплексоры располагаются на концах линии связи. Мультиплексоры ввода/вывода устанавливаются в разрыв линии связи для вывода нескольких каналов из общего потока. Они позволяют избежать установки, обычно более дорогих терминальных мультиплексоров.