- •Лекция №1 литература.

- •План лекции

- •Самостоятельная проработка

- •Введение

- •1. Назначение и краткий обзор развития схемотехники эвм(5 проблем)

- •2. Активны и пассивные элементы схемотехники

- •4. Понятие блок-схемы, функциональной и принципиальной схемы

- •5.Условные обозначения схемотехнических элементов

- •Лекция №2 План лекции.

- •3. Формы представления информации

- •4. Входной контроль

- •1 Краткий словарь схемотехники

- •2. Функциональная схема эвм и принцип ее работы

- •3. Формы представления информации

- •Лекция №3 план лекции

- •Функциональные узлы эвм

- •2 Формирование и преобразование сигналов

- •Дифференцирующие цепи

- •Оперативное запоминающее устройство

- •Устройство управления

- •Арифметическое устройство

- •Самостоятельная работа формирование и преобразование сигналов Дифференцирующие цепи

- •Интегрирующие цепи (иц)

- •Лекция №4 план лекции

- •Код. Кодирование. Способы кодирования

- •Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Двоичное кодирование графической информации

- •2. Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Кодирование графической информации

- •Изображения растровые векторные

- •Кодирование векторных изображений.

- •Лекция №5

- •5.1 Логическое отрицание не

- •5.2 Логическое умножение и

- •5.3 Логическая функция сложения или

- •5.4 Функция Шеффера

- •5.5 Стрелка Пирса

- •5.6 Исключающее или

- •5.7 Эквивалентность

- •5.8 Импликация

- •Лекция №6а план лекции

- •Этапы развития логики

- •Законы алгебры логики

- •Законы алгебры логики

- •Лекция №7 минимизация функции

- •Самостоятельная работа Минимизация логической функции

- •Лекция №8-9 план лекции

- •1.Принцип работы полупроводниковых устройств

- •2. Потенциальные системы схем эвм

- •Рассмотрим принцип работы транзистора

- •Инвертор

- •Транзисторная логика(самостоятельная работа)

- •Лекция №10 схемотехника транзисторно-транзисторнй логики (ттл)

- •Лекция №11

- •2. Схемотехника ис инжекционной логики--иил (и2л)

- •Схемотехника ис инжекционной логики и2л

- •Лекция 12

- •Схемотехника транзисторной логики со связанными эмиттерами(эстл).

- •2. Схемотехника ис на полевых транзисторах (пт)

- •Схемотехника ис на полевых транзисторах (пт)

- •Лекция №12а схемотехника цифровых элементов

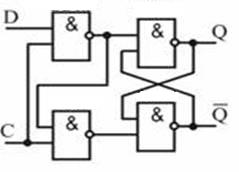

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №13

- •10.0 Основные динамические параметры интегральных схем потенциального типа

- •Самостоятельная работа Развитие схем потенциального типа

- •10.2 Таблица сравнения цифровых интегральных микросхем

- •Лекция №13а схемотехника цифровых элементов

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №14

- •11.0 Регистры хранения и сдвига

- •11.1 Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №14а универсальные jk триггеры

- •9.7 Триггер Шмитта – (тл)

- •Лекция №15 универсальные регистры

- •Лекция №17(самотоятельно) кольцевой счетчик

- •12.3 Делители частоты

- •Лекция №18a синхронный (тактируемый) rs, d и т триггеры

- •Выходной сигнал q сохраняется до прихода очередного тактового импульса. Причем эта информация хранится в d-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти.

- •Лекция №20 регистры хранения и сдвига

- •Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №21 план лекции

- •Реверсивные счетчики (рс)

- •Кольцевой счетчик

- •Делители частоты(Самостоятельно)

- •Лекция №23 преобразователи кодов

- •Лекция №24 дешифраторы decoder (dc)

- •Контрольная работа Используя таблицу истинности составить временные диаграммы дешифратора 2х4

- •Лекция №25

- •Пример сети с двумя типами мультиплексоров самостоятельная работа

- •Лекция №26 демультиплексоры

- •Лекция №27 сумматоры и алу

- •Контрольная работа

- •Лекция №28 сумматоры и алу

- •Лекция №29-30 схемотехника обслуживающих элементов Генераторы и формирователи импульсов

- •Формирователи импульсов

- •Лекция №28 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №31 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №32-33 компараторы и таймеры

- •Цифро-аналоговые и аналого-цифровые преобразователи

12.3 Делители частоты

Часто при проектировании цифровых автоматов возникает необходимость в делителях частоты, для которых коэффициент счета (Ксч) - любое целое число.

Требуемое число Ксч (2, 3, 4, 5 ...10) получают путем введения в счетчики обратных связей. Очевидно, что для разработки счетчика с модулем (коэффициентом деления Ксч) 2, 4, 8 не требуется цепь обратной связи, а меняется лишь количество последовательно соединенных разрядов Т-триггеров.

Следовательно, для разработки делителя частоты с модулем 3, 5, 7, 9 необходимо между выходным и входным триггером включить делитель частоты на любое натуральное число n.

При этом модуль (коэффициент счета) определяется:

Ксч=2n+1.

Например, для счетчика делителя частоты с коэффициентом (модулем) 3 n=1. Это означает, что имеется обратная связь (непосредственная без ЛЭ) между входным и выходным триггерами.

Делитель на 5

Делитель на 6

Рис. 12.20 Делители частоты

Лекция №18a синхронный (тактируемый) rs, d и т триггеры

Синхронный (тактируемый) RS-триггер имеет управляющий вход – С (clock – основная синхронизация), который при С=1 разрешает переключение по закону RS-триггера, при С=0 триггер сохраняет свое состояние.

Схема и временные диаграммы тактируемого синхронного RS-триггера приведены на рис.

Характеристические уравнения для RS-триггеров:

Q(t+1)=S(t)VQ(t)*![]() (t),

(t),

где Q(t+1) – состояние триггера в момент времени t+1.

Рис. Схема и временные диаграммы тактируемого синхронного RS-триггера

Тригер называется синхронным, так как работа триггера управляется при наличии сигналов С, S и R.

В таком простейшем

виде (R-S,

![]() )

ячейки памяти (запоминающие ячейки)

входят в состав более сложных схем.

)

ячейки памяти (запоминающие ячейки)

входят в состав более сложных схем.

Синхронизирующие входы с динамическим управлением часто используются в ИС высоких степеней интеграции.

Техническим решением, обеспечивающим сокращение числа тактовых сигналов в цепях управления цифровыми устройствами, также является применение двухступенчатых триггеров. Такие триггеры позволяют за один такт производить запись новой и съем старой информации. Для хранения одного бита информации в этом случае приходится использовать две элементарные триггерные схемы, информация в которых устанавливается взаимоинверсными тактовыми импульсами. Так как при этом два триггера объединяются в одну схему, то второй тактовый импульс получают инвертированием первого. Если на тактовый вход подается сигнал С=1, то входная информация принимается в триггер ступени I; в это время схемы 2И-НЕ на входе триггера ступени II заблокированы нулевым сигналом.

Рис. Двухступенчатый триггер

При подаче на тактовый вход триггера сигнала, равного "0", схемы " И-НЕ на входе основной запоминающей ячейки закрыты, а на входе вспомогательной запоминающей ячейки – открыты, и она принимает информацию из основной ячейки (триггер II ступени принимает информацию от триггера ступени I).

Так как триггер управляется сигналами R, S, C, то это синхронный двухступенчатый RS-триггер.

Следует отметить, что триггер любого типа является простейшим цифровым автоматом (автоматом Мура), его работу можно представить: в виде таблицы, в виде временных диаграмм или же характеристическим уравнением.

D-ТРИГГЕРЫ.

D-триггер - триггер задержки (от английского delay-задержка), при разрешающем сигнале на тактовом входе C устанавливается в состояние, соответствующее потенциалу на входе D. Если обозначать выходной сигнал триггера буквой Q, то для D – триггера можно написать следующее равенство: Qn=Dn-1. Индексы n и n-1 указывают на то, что выходной сигнал Q изменяется не сразу после изменения входного сигнала D, а только с приходом разрешающего тактового сигнала, т.е. существует задержка.

Dn |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

Тактирование D-триггера может осуществляться уровнем или фронтом. Более простым является статический D-триггер первого типа, который реализуется на основе RS-триггера.

Статический D-триггер синхронизируемый уровнем

Статический D-триггер

Анализ работы и временная диаграмма показывают, что сигнал с входа D проходит на выход Q только при условии высокого уровня на тактовом входе C.

В тактируемом фронтом D-триггере изменение потенциала на входе D, синхронное с тактовыми импульсами, повторяется на выходе Q по перепаду уровня (в данном случае с низкого на высокий) с задержкой относительно тактовых импульсов.

Динамический D-триггер