- •Лекция №1 литература.

- •План лекции

- •Самостоятельная проработка

- •Введение

- •1. Назначение и краткий обзор развития схемотехники эвм(5 проблем)

- •2. Активны и пассивные элементы схемотехники

- •4. Понятие блок-схемы, функциональной и принципиальной схемы

- •5.Условные обозначения схемотехнических элементов

- •Лекция №2 План лекции.

- •3. Формы представления информации

- •4. Входной контроль

- •1 Краткий словарь схемотехники

- •2. Функциональная схема эвм и принцип ее работы

- •3. Формы представления информации

- •Лекция №3 план лекции

- •Функциональные узлы эвм

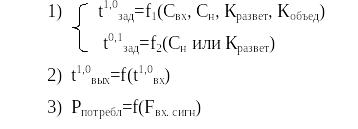

- •2 Формирование и преобразование сигналов

- •Дифференцирующие цепи

- •Оперативное запоминающее устройство

- •Устройство управления

- •Арифметическое устройство

- •Самостоятельная работа формирование и преобразование сигналов Дифференцирующие цепи

- •Интегрирующие цепи (иц)

- •Лекция №4 план лекции

- •Код. Кодирование. Способы кодирования

- •Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Двоичное кодирование графической информации

- •2. Формы представления чисел

- •3. Двоичное кодирование текстовой информации

- •4. Кодирование графической информации

- •Изображения растровые векторные

- •Кодирование векторных изображений.

- •Лекция №5

- •5.1 Логическое отрицание не

- •5.2 Логическое умножение и

- •5.3 Логическая функция сложения или

- •5.4 Функция Шеффера

- •5.5 Стрелка Пирса

- •5.6 Исключающее или

- •5.7 Эквивалентность

- •5.8 Импликация

- •Лекция №6а план лекции

- •Этапы развития логики

- •Законы алгебры логики

- •Законы алгебры логики

- •Лекция №7 минимизация функции

- •Самостоятельная работа Минимизация логической функции

- •Лекция №8-9 план лекции

- •1.Принцип работы полупроводниковых устройств

- •2. Потенциальные системы схем эвм

- •Рассмотрим принцип работы транзистора

- •Инвертор

- •Транзисторная логика(самостоятельная работа)

- •Лекция №10 схемотехника транзисторно-транзисторнй логики (ттл)

- •Лекция №11

- •2. Схемотехника ис инжекционной логики--иил (и2л)

- •Схемотехника ис инжекционной логики и2л

- •Лекция 12

- •Схемотехника транзисторной логики со связанными эмиттерами(эстл).

- •2. Схемотехника ис на полевых транзисторах (пт)

- •Схемотехника ис на полевых транзисторах (пт)

- •Лекция №12а схемотехника цифровых элементов

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №13

- •10.0 Основные динамические параметры интегральных схем потенциального типа

- •Самостоятельная работа Развитие схем потенциального типа

- •10.2 Таблица сравнения цифровых интегральных микросхем

- •Лекция №13а схемотехника цифровых элементов

- •9.1 Схемотехника триггерных схем

- •9.2 Асинхронный rs-триггер

- •Лекция №14

- •11.0 Регистры хранения и сдвига

- •11.1 Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №14а универсальные jk триггеры

- •9.7 Триггер Шмитта – (тл)

- •Лекция №15 универсальные регистры

- •Лекция №17(самотоятельно) кольцевой счетчик

- •12.3 Делители частоты

- •Лекция №18a синхронный (тактируемый) rs, d и т триггеры

- •Выходной сигнал q сохраняется до прихода очередного тактового импульса. Причем эта информация хранится в d-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти.

- •Лекция №20 регистры хранения и сдвига

- •Регистры сдвига на d-триггерах с параллельным выводом информации

- •Лекция №21 план лекции

- •Реверсивные счетчики (рс)

- •Кольцевой счетчик

- •Делители частоты(Самостоятельно)

- •Лекция №23 преобразователи кодов

- •Лекция №24 дешифраторы decoder (dc)

- •Контрольная работа Используя таблицу истинности составить временные диаграммы дешифратора 2х4

- •Лекция №25

- •Пример сети с двумя типами мультиплексоров самостоятельная работа

- •Лекция №26 демультиплексоры

- •Лекция №27 сумматоры и алу

- •Контрольная работа

- •Лекция №28 сумматоры и алу

- •Лекция №29-30 схемотехника обслуживающих элементов Генераторы и формирователи импульсов

- •Формирователи импульсов

- •Лекция №28 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №31 схемотехника аналоговых и комбинированных узлов Операционные усилители(оу)

- •Лекция №32-33 компараторы и таймеры

- •Цифро-аналоговые и аналого-цифровые преобразователи

9.2 Асинхронный rs-триггер

В зависимости от логической структуры различают RS-триггеры с прямыми и инверсными входами. Их схемы и условные обозначения приведены на рис. На базе 2ИЛИ-НЕ.

Рис. 9.3 RS-триггеры с прямыми и инверсными входами

На рисунке 9.3(а)

приведена схема триггера на двух

логических элементах ИЛИ-НЕ

– это RS-триггер

с прямыми входами, на рис.9.3(б) – условное

обозначение ИС.

На рис. 9.3(в) – RS-триггер

собранный на двух логических схемах

И-НЕ

с инверсными входами, на рис.9.3(г) –

условное обозначение. Как видно прямой

(Q) и инверсный (![]() )

подсоединены к одному из входов другого

элемента, что обеспечивает триггеру

два устойчивых состояния.

)

подсоединены к одному из входов другого

элемента, что обеспечивает триггеру

два устойчивых состояния.

Рассмотрим принцип работы RS-триггеров.

При входных сигналах S=1, R=0 триггер устанавливается в единичное состояние Q=1, а при S=0, R=1 в состояние Q=0. При S=R=0 триггер сохраняет исходное состояние. Если же S=R=1 – триггер находится в неустойчивом (неопределенном) состоянии. Следовательно, данная комбинация входов S=R=1 является запрещенной. Временные диаграммы сигналов RS-триггеров приведены ниже.

Рис. 9.4 Временные диаграммы сигналов RS-триггеров

Соответственно таблица истинности RS-триггеров

С прямыми входами С инверсными входами

S |

R |

Q |

|

|

|

|

Q |

|

0 |

0 |

0 |

1 |

|

0 |

0 |

* |

* |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

1 |

1 |

* |

* |

|

1 |

1 |

0 |

1 |

Из таблицы истинности видно, что состояние входов S=1, R=1является запрещенными для RS-триггера с прямыми входами, а состояние входов S=0, R=0 для триггера с инверсными входами. После окончания информации на этих входах в обоих случаях триггер может иметь любое из устойчивых состояний. Именно по этому эти комбинации входов являются запрещенными.

Режим S=1, R=0 называется режимом записи 1, так как при этом Q=1, а режим S=0, R=1 – режим записи 0. Режим S=0, R=0 – режим хранения информации, так как при этом информация на выходе триггера не меняется. Для триггера с инверсными входами все наоборот.

Лекция №13

10.0 Основные динамические параметры интегральных схем потенциального типа

Для эксплуатации триггеров необходим учет ряда диаграммных параметров:

Длительность импульса – tu. Это минимальный отрезок времени, в течение которого активный уровень управляющего сигнала или логической переменной на входе ИС остается неизменным.

Рис. 10.1 Динамические параметры интегральных микросхем

Время восстановления tв – минимально допустимое время между изменением уровней на двух специфицированных входах микросхемы. Например, для триггеров и регистров tв – минимально допустимое время между окончанием действия сигнала по установленному входу (

)

и изменением сигнала на синхронизирующем

входе С.

)

и изменением сигнала на синхронизирующем

входе С.Время предварительной установки tуст – минимальный интервал времени, в течение которого сигнал, поданный на один из специфицированных входов микросхемы, должен оставаться неизменным до смены уровней на другом специфицированном входе.

К основным динамическим характеристикам относятся:

нагрузочная характеристика, время задержки, мощность потребления.

Например, для надежного распознавания триггером или другой микросхемой логической информации сигнала, подаваемого на логический вход, последний должен опережать сигнал на синхровходе на величину tуст.

Время фиксации tфикс – минимальное время, в течение которого сигнал на логическом входе должен оставаться неизменным после смены уровней на синхронизирующем входе. Соблюдение этого условия также гарантирует надежное распознавание микросхемой логической информации.