- •1.Типы корпусов интегральных микросхем, маркировка.

- •2. Серии интегральных микросхем, зарубежная и отечественная система обозначений.

- •3. Варианты выходных каскадов интегральных микросхем. Обозначение, управление.

- •4.Логические элементы и, или и-не, или-не. Типы, уго, таблица истинности.

- •5. Применение простых логических элементов для реализации схем смешивания, разрешения сигналов, формирования коротких прямоугольных импульсов

- •6.Логический элемент “исключающее или”. Уго, таблица истинности.

- •12. Дешифраторы с выходом на 7мисегментный индикатор. Входы управления. Назначение, работа.

- •13. Шифраторы. Приоритетный шифратор. Уго, таблица истинности

- •14. Мультиплексоры. Уго, таблица истинности. Назначение входов управления.

- •15.Микросхемы выполнения арифметических операций. Компараторы, Сумматоры. Уго, таблица истинности. Назначение входов/выходов.

- •17. Типовые применения одно- и мультивибраторов.

- •18. Триггеры. Типы, уго, таблица истинности. Основные характеристики. Назначение входов/выходов.

- •22. Сдвиговые регистры. Назначение входов управления, выходов, режимы, наращивание разрядности.

- •23. 4Хразрядный накапливающий сумматор. Схема, описание работы.

- •25. Элементы с памятью., Асинхронные счетчики. Уго. Назначение, временная диаграмма, схемотехнические решения для одновременного считывания выходного кода.

- •26.Элементы с памятью. Синхронные счетчики с асинхронным переносом.. Уго. Назначение, временная диаграмма. Назначение входов/выходов

- •27. Элементы с памятью. Синхронные счетчики с синхронным переносом, уго. Назначение, временная диаграмма. Назначение входов/выходов.

- •28.Варианты соединения счетчиков для увеличения разрядности в случае применения асинхронных и синхронных счетчиков.

- •29. Измерение частоты/периода сигнала при помощи элементов цифровой вычислительной техники.

- •29. Схема динамической индикации.

- •35. Основные требования, предъявляемые схемам с использование цап. Генерация сигналов произвольной формы

- •38. Основные типы построения ацп. Принципы работы.

- •40. Микросхемы пзу. Назначение, уго, варианты исполнения. Входные/выходные сигналы.

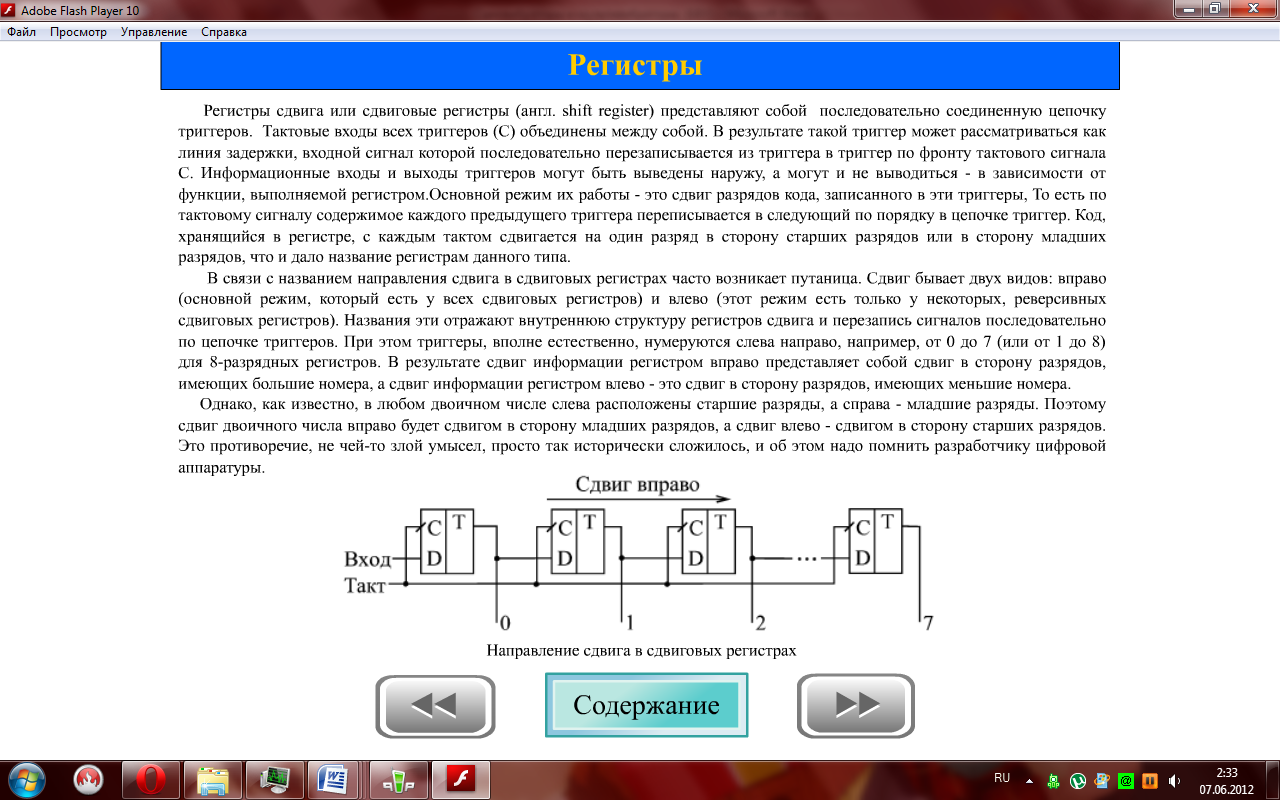

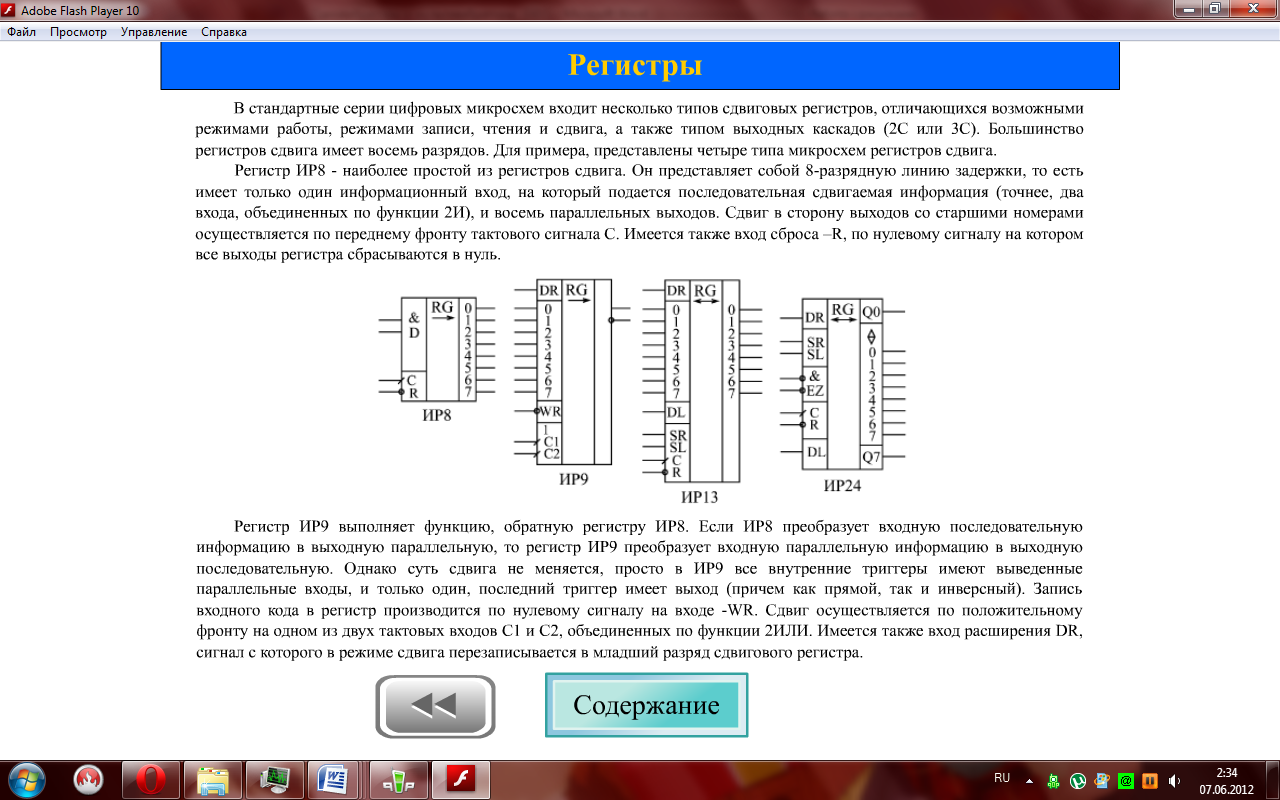

22. Сдвиговые регистры. Назначение входов управления, выходов, режимы, наращивание разрядности.

23. 4Хразрядный накапливающий сумматор. Схема, описание работы.

Сумматор - устройство, выполняющее операции арифметического сложения над двоичными числами.

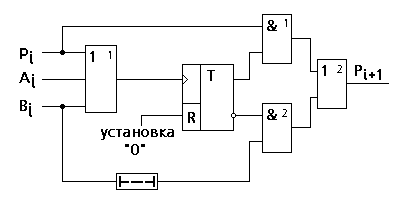

Рис. 1 - Одноразрядный цифровой сумматор

Сумматор имеет входы А и В - слагаемые, С - вход переноса, S - выход суммы, Р - выход переноса. На выходе S представляется сумма сложения трех переменных - А, В, С. При переполнении сумматора, т. е. когда в результате сложения формируется единица в старшем разряде выходного числа, на выходе переноса Р формируется уровень лог. 1, который подается на вход переноса С следующего сумматора. В принципе, старшим разрядом суммы является выход переноса Р.. Из таких одноразрядных сумматоров составляются многоразрядные сумматоры (обычно 4-х разрядные), которые бывают последовательного и параллельного действия. Сумматоры последовательного действия обладают более низким быстродействием. Сумматор может быть построен как комбинационная схема - последовательный сумматор и как последовательностная схема -накапливающий сумматор. Накапливающий сумматор является автоматом с памятью, т.е. слагаемые могут приходить поочередно в произвольные моменты времени и запоминаться в линиях задержки или в триггерах. Накапливающий. сумматор применяется в асинхронных устройствах, в которых слагаемые не привязаны к тактам тактового генератора.

С приходом слагаемого аi=1 элемент "ИЛИ" устанавливается в "1", триггер устанавливается. в "1". Если bi=1 и приходит через какое-то время после ai, то оно запоминается в линии задержки и одновременно bi опрокидывает триггер в "0". На инверсном выходе триггера устанавливается "1", следовательно на вторую схему "И" подаются две единицы, следовательно на выходе второй схемы "ИЛИ" формируется цифра переноса в старший разряд, равная "1". Если Pi=0, то цифра суммы, которая снимается с прямого выхода триггера, равна "0". Если Pi=1, то сумма Si=1.

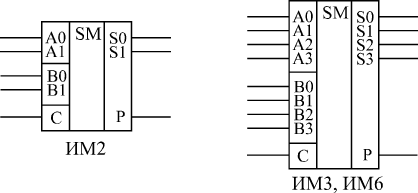

4-х разрядные (суммируют 4-х разрядные числа)

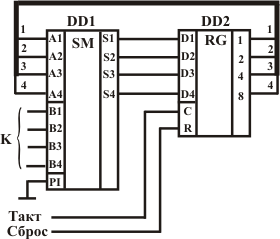

На рисунке показан простейший сумматор-накопитель. На один вход сумматора подается число К, а на второй - число с выхода регистра. В начале работы регистр обнуляется (сброс). Если на входы В сумматора DD1 подать некоторое число К, то при подаче импульса на вход С регистра (такт) в него запишется число К (в начальный момент на выходе регистра лог.0). Это же число К попадет на входы А сумматора и по следующему такту в регистр запишется уже число 2К, которое опять попадет на входы А сумматора. На выходе сумматора появится число 3К и по следующему такту запишется в регистр и т. д. То есть, в сумматоре-накопителе постепенно нарастает число. Когда в сумматоре-накопителе накопленное число превышает его объем, равный 2n-1, на выходе переноса появляется сигнал лог. 1, а на выходах S число nK-2n.