- •Комбинационный конвеерный сумматор с пт

- •3. Умножение с пт. Схема и алгоритм умножения мантисс, начиная со старших разрядов множителя и со сдвигом множимого

- •4. Умножение с пт. Схема и алгоритм умножения мантисс, начиная с младших разрядов множителя и со сдвигом множимого.

- •5. Умножение с пт. Схема и алгоритм умножения мантисс, начиная со старших разрядов множителя и со сдвигом суммы частных произведений.

- •6. Умножение с пт. Способы ускорения умножения. Конвейерный умножитель. Умножение

- •Комбинационный умножитель

- •7. Деление с пт. Схема и алгоритм деления мантисс с восстановлением остатка.

- •8. Деление с пт. Схема и алгоритм деления мантисс без восстановления остатка.

- •Деление без восстановления остатка.

- •9. Управляющие автоматы. Сравнительный анализ. Апл.

- •Способы адресации апл.

- •12. Форматы команд эвм общего назначения

- •Вызов подпрограммы.

- •13. Форматы команд специализированных эвм.

- •14. Структура 8-разрядного мп и его регистровая модель..

- •15. Структура 16-разрядного мп и его регистровая модель.

- •Сигналы мп i286

- •16. Структура мп i486 и его регистровая модель.

- •Программная (регистровая) модель процессора i486.

- •1. Пользовательские rg i486

- •Сегментные регистры

- •Указатель команды ip

- •Регистр флагов. Flags.

- •17. Режимы работы процессоров, форматы команд, виды данных.

- •18. Кэш память.

- •Многоуровневость

- •19. Сегментная и страничная организация памяти.

- •Страничная организация памяти.

- •20. Организация ввода-вывода.

- •1.1. Состав периферийного оборудования мпс

- •1.3. Структурная организация интерфейса ввода-вывода мпс с единой системной шиной

- •21. Сигнальные процессоры, классификация, отличительные особенности, структура мп I 2920

- •22. Внешние устройства, обзор. Клавиатура, мышь, джойстик. Внешние устройства.

- •1.1. Клавиатура

- •1.2.1. Мышь

- •Джойстик

- •23. Сканеры, обзор. Планшетные сканеры. Барабанные сканеры. Сканеры

- •24. Принтеры, обзор. Лазерные, матричные, струйные и плоттеры

- •25. Мониторы, структуры, принципы действия, сравнительная характеристика. Плазменные мониторы.

21. Сигнальные процессоры, классификация, отличительные особенности, структура мп I 2920

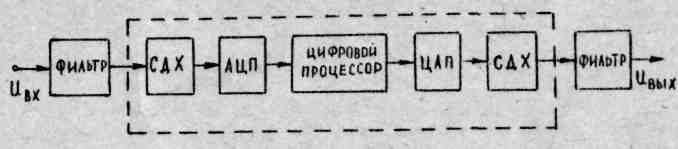

Цифровая обработка аналоговых сигналов (рис.) связана с их квантованием и последующим восстановлением. Входной непрерывный сигнал системы в схеме дискретизации и хранения (СДХ)

квантуется по времени с частотой выборки и запоминается на время его преобразования в АЦП. АЦП осуществляет дополнительное квантование по амплитуде.

Существующие в настоящее время МП для обработки аналоговых сигналов можно условно, в зависимости от их архитектуры, разделить на три класса:

-собственно аналоговые МП, на кристалле которых собраны ЦП, АЦП и ЦАП

- однокристальные МП со встроенным АЦП и цифровым интерфейсом,

- цифровые МП с интерфейсом, обеспечивающим подключение АЦП, ЦАП и цифровых приборов.

Аналоговый микропроцессор INTEL 2920. Структура МП 2920

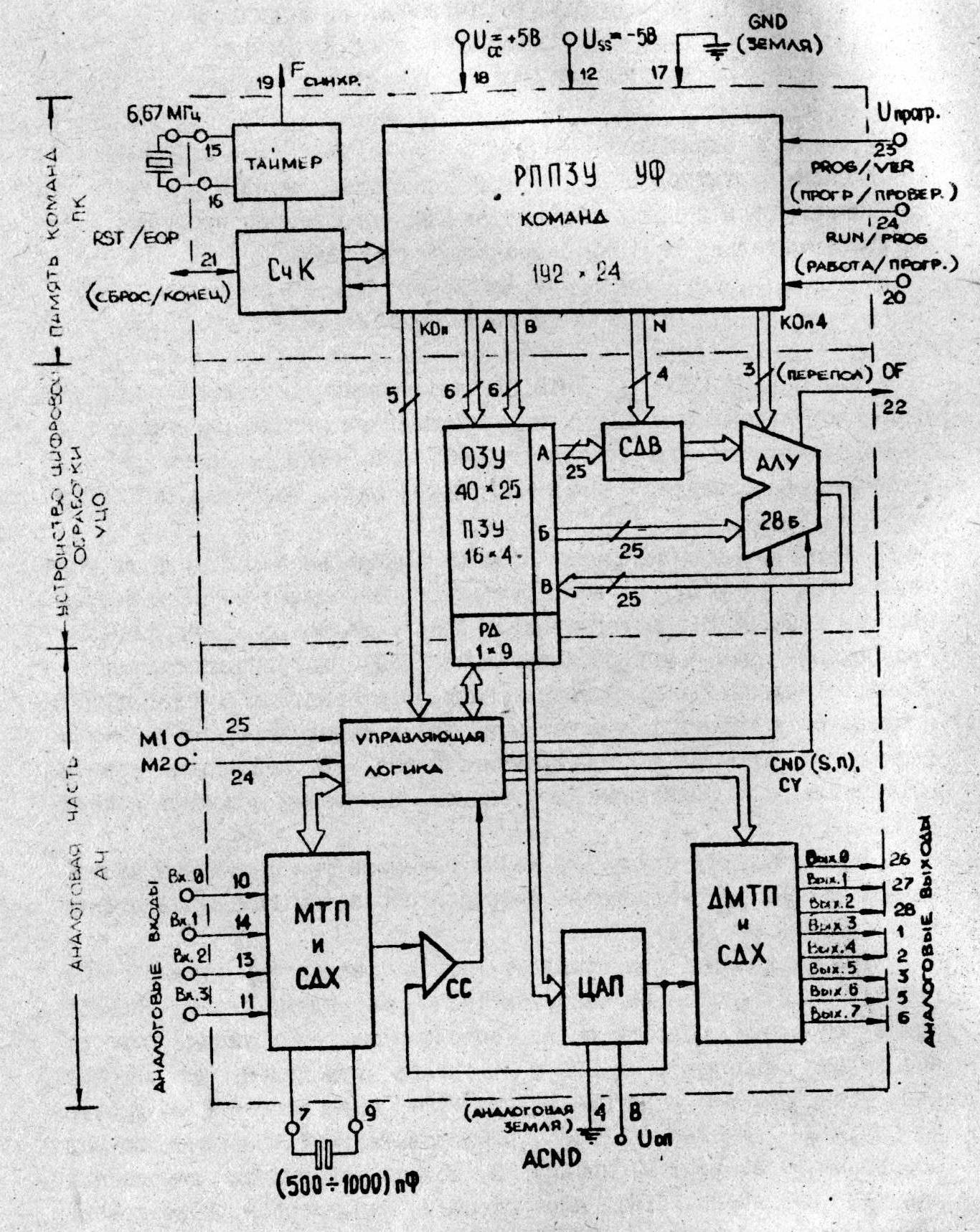

МП 2920 является типичным представителем классических аналоговых МП со встроенными АЦП и ЦАП. Схему МП 2920 можно условно разделить на три зонт аналоговый интерфейс, цифровая обработка данных и программная память.

Четыре независимых аналоговых сигнала, заданных амплитудой напряжения постоянного тока, через четырехканальный аналоговый коммутатор - мультиплексор (МТП) последовательно поступают в схему дискретизация и хранения (СДХ). Под действием сигналов управляющей логики в соответствующие разряды РгД последовательно, начиная со старшего, устанавливаются пробные единицы. ЦАП преобразовывает код РгД в напряжение обратной связи, которое сравнивается компаратором с входным сигналом. Выход компаратора либо подтверждает правильно установленную пробную единицу, либо сбрасывает ложную.

Полученные в результате цифровых вычислений выходные коды фиксируются в РгД, преобразовываются с помощью ЦАП в напряжение, распределяются а демультиплексоре (ДМТП) по восьми аналоговым выходным шинам и фиксируются в восьмиканальной СДХ . Рассмотренные схемы образуют аналоговый интерфейс МП 2920.

Операционная часть микропроцессора, осуществляющая цифровую обработку данных, содержит ОЗУ емкостью 40 25-разрядных слов; сдвигатель СДВ на программно-управляемое число разрядов (от 2 разрядов влево до 13 разрядов вправо); 28-битное АЛУ, способное выполнять операции сложения, вычитания, выделения модуля, пересылки и некоторые логические. Операционная часть выполнена по нестандартной схеме, в частности, здесь использовано двухпортовое О3У (порты А и В). РгД также относится к ОЗУ, так что МП рассматривает свои входы и выходы как ячейки памяти. Под каждый адрес в команде отведено 6 бит, следовательно адресное пространство составляет 64 ячейки, из них 40 - в ОЗУ, 23 - константы и 1 - РгД. Ячейка ОЗУ равнодоступны через любой из двух портов. Результат вычислений записывается в адрес В.

Сдвигатель СДВ осуществляет масштабирование чисел, вызываемых через порт А (первый адрес команды), т.е. умножение их на 2k (где К = 2,1,0,-1,-2,,..,-13). Масштабирование используется для ускорения умножения переменных на константы за счет использования сложения и вычитания сдвинутых (масштабированных) переменных. Разрядность АЛУ - 28 бит, на 3 бита больше длины операндов. Эта избыточность используется при округлении результатов вычислений.