- •Способы организации каналов аналогового ввода (коммутация аналоговых и цифровых сигналов).

- •Обеспечение отказоустойчивости scada системы WinCc.

- •Клиент серверная архитектура scada системы WinCc. 30

- •Уровни стандартизации модулей систем управления. 6

- •5. Модели жизненного цикла аппаратуры. Прототипирование.

- •1.5.1 Модель последовательностного жизненного цикла.

- •Понятия «Система управления», «Внедренная система управления». Модульный принцип построения систем управления.

- •Понятия «Универсальный вычислитель», «Специализированный вычислитель», «Программируемый логический контроллер». Соотнесение процессов универсализации и специализации.

- •Способы программирования. Место программатора при построении систем управления.

- •8.1.2 Внутрисхемное программирование

- •8.1.3 Внутрисистемное программирование

- •8.1.4 Активное программирование

- •8.1.5 Адаптивная система

- •9. Особенности промышленных иус. Понятие «Полевая шина». Требования к специализированным интерфейсам.

- •4.1 Иерархическая структура использования интерфейсов 17

- •10. Логическая реализация интерфейса can.

- •12. Временные характеристики каналов аналогового ввода/вывода.

- •13. Понятие «scada-система», ее основные функции, типичная структура.

- •Клиент-серверная архитектура scada-системы, реализация отказоустойчивости. См. 2,3 вопросы

- •Технология краевого сканирования корпорации jtag.

- •Реализация многовходового логического элемента «и» программируемой логической матрицы. Схема монтажного «и». Структура программируемой логической матрицы на этих элементах.

- •Балансный и небалансный способ передачи сигнала. Реализация балансного способа в сетях на основе rs 485.

- •4.2.3 Реализация симметричных линий связей в rs-485

- •Иерархия интерфейсов интегральных информационно-управляющих систем. Иерархическая структура систем управления производством.

- •Модульная структура scada системы WinCc.

- •Виды внутренних ресурсов программируемых логических интегральных схем. Внутренняя структура программируемых логических интегральных схем.

- •4) Блок программируемой фазовой задержки, или блок формирования фазы

- •8.2.1 Сферы применения

- •8.2.4 Достоинства плис

- •8.2.5 Недостаток плис:

- •Программируемая логическая матрица «и-или».

- •Способы подключения датчиков.

- •Понятие «Система на кристалле» и состав внутренних функциональных модулей.Способы ее построения.

- •Иерархия уровней управления. «Пирамида управления». Иерархическая структура использования интерфейсов. См 18

- •Виды программного обеспечения и альтернативные метафоры программирования.

- •Программно-управляемые вычислительные устройства на базе плис. Интегральные схемы fpslic.

- •Языки описание аппаратуры. Язык vhdl: основные понятия.

- •34. Структура описания vhdl. Виды описаний аппаратуры.

34. Структура описания vhdl. Виды описаний аппаратуры.

Существует 3 вида описаний на языке VHDL:

1. Структурное (регистровое) описание;

При нём архитектура проекта представляется в виде иерархий связанных компонентов, каждый экземпляр компонента представляет часть проекта, которая, с другой стороны, может быть описана объектом другого уровня иерархии, и т.д.

2. Потоковое описание (dataflow description);

Архитектура представляется в виде множества параллельных регистровых операций, каждый и которых управляется специальными сигналами для потокового описания. Часто используется язык графического описания RTL, который представляет разработку в виде набора регистров и систем управления ими. (Register Transfer Language), представляет собой Ассемблер, не зависящий от команд конкретного процессора. Описание конфигурации аппаратуры может быть получено из других типов описания (автоматических).

3. Поведенческое описание (behavior description).

Определяет функционирование устройств без определения его структуры. Например, один из разработчиком может детально специфицировать поведение системы, а проработка деталей может осуществляться другим проектировщиком.

Преимущества VHDL программы перед схемным проектированием:

С помощью VHDL гораздо проще ввести и проверить большой проект. Десятью строками VHDL можно описать как один, так и 100 000 триггеров

VHDL проекты не обязательно макетировать. Достаточно просто запустить их VHDL-код через симулятор HDL.

VHDL программы не требуют их представления в виде схемы. Нечеткость и небрежность описания также исключаются, так как такую программу не сложно проверить.

VHDL программы – надёжны. Синтаксический анализ, программное моделирование и компиляция в логическую схему быстро выявляют ошибки проекта

VHDL программы – универсальны. Однажды разработанный VHDL-компонент может быть многократно использован во множестве других проектов. При этом функции и параметры компонента можно подстраивать под новые задачи на любом этапе проектирования. Также универсальность заключается в том, что VHDL проекты с одной элементной базы легко переносятся на другую (например, микросхемы различных технологий).

На Западе, исторически, наибольшее распространение получил язык Verilog. Два десятилетия назад этот язык выиграл конкурентную борьбу с другими HDL языками благодаря тому, что занимал мало вычислительных ресурсов компьютера. VHDL – более универсальный и быстрый язык, но он проигрывал в быстродействии языку Verilog, особенно при моделировании на уровне вентилей.

VHDL код – долговечен, в отличие от электрической схемы, которая всегда разрабатывается под конкретную элементную базу. Так как обычно через 3-5 лет элементная база сменяется, сменяются и электрические схемы, использующие её. Хорошее техническое решение на языке VHDL может быть использовано в течении десятилетий. При описании цифровой аппаратуры программа VHDL состоит из 5 типов, из которых наиболее часто используются первые два.

1. Объявление объекта проектом (сущность проекта). Entity (сущность) – словом VHDL. Представляет собой описание компонента проекта, имеющего чётко заданные входы и выходы, и выполняющую чётко определённую функцию (содержит константы проекта, и описание входа и выход)

2. Архитектурное тело. Служит для описания структуры или поведения разрабатываемого объекта.

3. Объявление конфигураций. Предназначено для описания того, какие объекты используется для создания полного проекта.

4. Объявление пакета. Представляет собой указания пакетов, содержащих наиболее часто используемые функции. Пакеты эквиваленты набору типовых функций в языках программирования.

5. Тело пакета. Если пользователь использует нестандартные операции или функции, их интерфейс указывается в объявлении проекта, а исполнение функций описывается в теле проекта.

35. Языки описание аппаратуры. Язык VHDL: использование портов, модели данных, определение векторов. +34 начало Типы используемых библиотек

1. Библиотека проекта (Design library) – включает в себя все разработанные и подключенные модули. Библиотека определяется именем. Каждое из описаний является самостоятельной конструкцией языка VHDL и может быть независимо проанализировано анализатором, и имеет название «модуль проекта» (Design unit).

2. Рабочая библиотека – библиотека, в которой в данном сеансе работает пользователь, и в которую помещается библиотечный модуль, полученный в результате анализа модуля проекта.

3. Библиотека ресурсов – библиотека, содержащая библиотечные модули, ссылка на которые имеется в анализируемом модуле проекта.

В тексте VHDL должны быть указаны все используемые библиотеки и их компоненты и используемые модули этих библиотек. Можно использовать всё – «.all»

Первая часть программы – это библиотеки. Все предложения языка VHDL заканчиваются «;».

Library use *библиотека*

--вот так обозначаются комментарии, в конце не нужно ставить «;»

Блок сущности (entity) – начало большого предложения языка, заканчивается «end *имя*». И только после «end» - «;». Сущность состоит из 2х частей:

Generic ((параметры) – содержат переменные, используемые в процессе препроцессинга. Константа используется только в процессе компиляции.)

Generic (*параметр*);

Порты – сдержат описания портов входа и выхода

Port (*описание портов*);

Описания, заключённые в скобки могут быть многострочным.

1. Сущность:

Generic (length : integer := 8); // создаём глобальную константу length, которая во всём проекте на момент компиляции = 8.

2. Порты:

Типы портов:

a. IN – входной порт только для чтения значения сигналов

b. OUT - выходной порт

c. INOUT – двунаправленный порт. Можно как записывать, так и читать из него.

d. Буфер – выходной порт, значение из которого можно считывать

e. Linkage – двунаправленный порт с ограниченным использованием (практически не используется).

Пример:

Port (A,B: IN:std_logic_vector (0 to 3); S:OUT:std_logic_vector (0 to3); C:OUT:std_logic);

Архитектурное тело состоит из 2х частей: определение констант и переменных, и из поля команд, которое содержит исполняемые действия. Поле определений от поля действий отделяется командой begin.

Architecture *имя архитектуры* *OP-имя сущности* *IS-описание определений*;

begin *действия*;

end *имя архитектуры*;

Действия архитектуры.

Действия могут представляться двояко: как операции и процессы.

36. Языки описание аппаратуры. Язык VHDL, блоки: «Сущность», «Архитектура». См 35+34 начало. Архитектура содержит две основные части:

1. часть, содержащую описания (декларации);

2. часть, содержащую исполняемые операторы.

В общем виде архитектура выглядит следующим образом:

architecture NAME_ARCHITECTURE of NAME_ENTITY is

-- Здесь содержатся:

-- - описания типов данных;

-- - функции и процедуры;

-- - компоненты более низкого уровня иерархии;

-- - описания сигналов и глобальных переменных.

begin

-- Здесь содержатся исполняемые операторы.

end NAME_ARCHITECTURE;

Gростой VHDL код для компонента NAND c двумя входами:

-------------------------------------------

-- VHDL код для компонента NAND2

-------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

---------------------------------

entity NAND2 is

port (

a, b : in std_logic;

c : out std_logic

);

end NAND2;

---------------------------------

architecture aaa of NAND2 is

begin

c <= not (a and b);

end aaa;

Получился вполне законченный синтезируемый VHDL-код.

37. Программно-управляемые вычислительные устройства на базе ПЛИС. Интегральные схемы FPSLIC. См 32

38. Языки описание аппаратуры. Язык VHDL: процессы, функции, процедуры. В VHDL используется два вида подпрограмм - это функции и процедуры. В библиотеке std_logic_1164 описаны различные функции, в том числе и rising_edge()/falling_edge() определение которых выглядит так:

function rising_edge (signal s : std_ulogic) return boolean is

begin

return (s'event and s = '1');

end;

function falling_edge (signal s : std_ulogic) return boolean is

begin

return (s'event and s = '0');

end;

А так как мы используем библиотеку std_logic_1164, то спокойно можем задействовать эти функции. Теперь давайте напишем наш дешифратор 16-ти разрядного адреса:

library ieee;

use ieee.std_logic_1164.all;

---------------------------------

entity dec is

port (res, ale : in std_logic;

addr : in std_logic_vector(15 downto 2);

cs : out std_logic);

end dec;

---------------------------------

architecture dec_arch of dec is

begin

process (res, ale)

begin

if (res = '1') then

cs <= '0';

elsif rising_edge(ale) then

if (addr = "11000011110000") then -- Это наше адресное пространство

cs <= '1';

else

cs <= '0';

end if;

end if;

end process;

end dec_arch;

ПРОЦЕСС Process (*лист чувствительности*)

*область декларации*

Begin *VHDL операторы* *описание процесса*

End process;

В программе на VHDL может присутствовать множество процессов, отмеченных разными списками чувствительности. Данные процессы реализуются параллельно. Все процессы в программе выполняются параллельно. Процессы обмениваются сигналами, которые выполняют синхронизацию процессов и переносят значения между ними. Если над сигналами определена функция разрешения, то выходы источников сигнала могут объединяться. Сигналы нельзя объявлять в процессах. Процесс невозможно поместить в процесс, так как там есть место только для последовательных операторов.

В круглых скобках заголовка процесса указывается множество сигналов, по которым процесс запускается - список чувствительности. Это форма оператора процесса, альтернативная процессу с оператором wait on, стоящим последним в цепочке последовательных операторов тела процесса. Любой процесс со списком чувствительности может быть преобразован в эквивалентный процесс с оператором wait on, стоящим последним в списке последовательных операторов. В операторе процесса со списком чувствительности ставить операторы wait не допускается.

Процесс представляет собой маленькую программу, которая выполняется на виртуальном процессорном элементе. Рассмотрим процесс, вычисляющий функцию синуса y от аргумента x по аппроксимирующей формуле:

sin(x) = c1x+c2x3+c3x5+c4x7.

Процесс выглядит следующим образом:

process

type tabl is array(0 to 3) of real;

constant c:tabl:=(0.99999, -0.16666, 0.00831, -0.00019);

variable xtmp, p: real:=0.0;

begin

xtmp:=x;

p:=c(0)*xtmp;

for i in 1 to 3 loop

p:=p+c(i)*xtmp*x*x;

end loop;

y<=p;

wait on x;

end process;

При моделировании логических схем в список чувствительности процесса необходимо вносить все входные сигналы, иначе моделирование схемы будет отличаться от ожидаемого. Например, процесс

process(A) begin

c<= A or B;

end process;

при моделировании дает графики как на рис. Из графиков видно, что изменение результирующего сигнала С происходит только в моменты изменения сигнала A, т.е. процесс моделирует некоторую триггерную схему, а не схему ИЛИ. Если в процессе запрограммирован алгоритм функционирования триггерной схемы, например, регистра, то допускается в списке чувствительности оставлять только сигналы управления записью и разрешения чтения, например, сигналы сброса и синхросерии.

При синтезе списки чувствительности игнорируются компилятором.

39. Языки описание аппаратуры. Язык VHDL: операции, условия, циклы, множественный выбор. Последовательный оператор. Оператор условия.

Особенностью оператора условия является наличие множества блоков срабатывания условия (когда условие верно), которые задаются командой ELSIF (другое если). Условие задаётся следующим образом:

IF *условие 1* then

*выполнение условия 1*…

ELSIF *условие 2* then

*выполнение условия 2*…

ELSE *невыполнение условия*…

End if;

19.7.3 Циклы

Задаются с использованием чётной переменной.

FOR *счётная переменная* IN *диапазон изменения* LOOP

*операция в цикле*;

END LOOP;

FOR i IN 5 downto 0 loop

*операции в цикле*

End loop;

19.7.4 Цикл с условием

Задаётся командой WHILE.

While *условие* LOOP *операции* end loop;

19.7.5 Множественный выбор

CASE *переменная* IS

When *значение 1* => *выполненная команда 1*;

END CASE

CASE sel IS

WHEN "00" => output <= in0;

…

END CASE;

19.7.6 Оператор ожидания

Оператор ожидания – определяет врем ожидания процесса, или события. Задаётся с помощью команды wait. Опирается на такое понятие, как список чувствительности (лист чувствительности) – одна или более переменных, изменение значения которых приводит к активации того или иного оператора.

Wait on (*лист чувствительности*) UNTIL *действие* FOR *время*;

Например:

Wait on (X,Y) UNTIL z=0 FOR 100ns

VHDL работает с точностью указания времени до фемтосекунды (10-15). Список чувствительности может отсутствовать вместе с командой.

События – либо фронт либо срез! Особые ситуации изменения переменных в списке чувствительности – это события фронта и среза сигнала.

Примеры использования последовательных операторов:

-- Использование операторов loop, next, exit, if, присваивание

-- Несинтезируемый фрагмент VHDL-кода подсчитывает кол-во несовпадающих бит в двух массивах

neq := 0;

L1 : for i in 0 to 31 loop

next L1 when mem1(i) = mem2(i);

for j in 7 downto 0 loop

crash := 1;

exit L1 when (mem1(i)(j) = 'X' or mem2(i)(j) = 'X');

crash := 0;

if (mem1(i)(j) /= mem2(i)(j)) then neq := neq+1;

end loop;

end loop L1;

-- Использование операторов wait, case, if

-- Синтезируемый фрагмент VHDL-кода управляет состояниями сфетофора

process begin

wait until clk;

if (trig = '1') then

case state is

when red => state <= green;

when green => state <= yellow;

when yellow => state <= red;

end case;

end if;

end process;

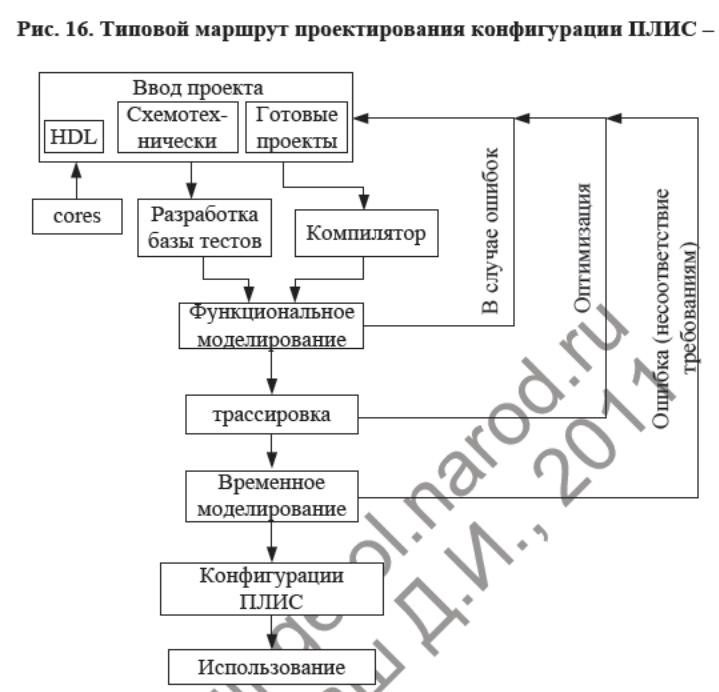

40. Понятие маршрута проектирования конфигурации программируемых логических интегральных схем. Типовой маршрут проектирования. Маршрут проектирования дизайн-flow – это графическое описание структуры передачи управления с одного этапа разработки на другой.

Этапы маршрута проектирования конфигурации ПЛИС.

Данный маршрут проектирования – граф показывающий взаимовысов. Программ, выполняющие различные функции. Маршрут проектирования указывает тип передаваемых данных и файлы их описания (рис.16)

Ввод проекта, в котором осуществляется разработка структуры графического или функционального описания всей схемы конфигурации или ее частей. При этом идет разработка в первую очередь схемы, с точки зрения ПЛИС. Вопросы использования конкретных блоков ПЛИС, сигналов управления, взаимного расположения элементов, как правило, решается на САПР на внешних планах проектирования.

Ввод проекта происходит на следующих уровнях:

1) Схемотехнический, на котором рисуются электрические принципиальные схемы;

2) Использование готовых проектов модулей (как платных, так и бесплатных)

– CORES (ядра) – вычислительные или иные ядра/модели проекта конфигурации.

– IP-блок являются платными ядрами.

3) HDL-описание – язык описания литературы. На данных языках аналогичных языкам программирования описывается конфигурация ПЛИС в виде функций управления.

4) Разработка базы тестов. Для созданных при вводе проектов схем разрабатываются тесты для осуществления проверки корректности разработки. Компилятор предназначен для подготовки проекта и распределения функциональных возможностей ПЛИС между элементами проекта, осуществляет функцию генерации в диаграмме Гайского-Кана.

5) Функциональное моделирование – это процесс, предназначенный для подтверждения работоспособности введенного проекта – верное функциональное функций описаны в техническом задании.

В настоящее время функциональному моделированию уделяется большое внимание в силу того, что высокая сложность ПЛИС создает высокую вероятность ошибок проекта, которые должны быть устранены.

6) Трассировка – это процесс, осуществляющий размещение конкретных функциональных узлов проекта по конкретным элементам ПЛИС, формально может быть отнесена к окончанию функций генерации и переходам по геометрической ветви.

7) Временное моделирование – предназначено для определения временных характеристик проекта. В этом блоке решается задача соответствия временных характеристик проекта требованиям технического задания.

8) Конфигурация ПЛИС (программирование ПЛИС) – запись в микросхему ПЛИС или в конфигурационную память требуемых настроек, сигналов управления и точек соединения в матрицу.

9) Использование (эксплуатация проекта).

41. Диаграмма Гайского-Кана. Данная диаграмма приведена на рисунке 15 и представляет собой последовательность и этапы разработки ПЛИС. Диаграмма состоит из трех ветвей, соединенных в виде литеры Y.

Диаграмма состоит из трех ветвей:

1) Поведенческая ветвь, в рамках которой идет описанное функционирование устройства;

2) Структурная ветвь, в рамках которой идет описание структуры;

3) Топологическая ветвь, или геометрия предназначена для описания внутренней геометрической интегральной схемы.

Диаграмма состоит из иерархии планов:

1) Архитектурный план, описывает тип и внутреннюю архитектуру, используемую в интегральной схеме.

2) Алгоритмический план, на котором решаются вопросы построения алгоритмов и их реализация.

3) Функциональный план, на котором решаются задачи функционирования интегральной схемы.

4) Логический план, который решает вопросы создания схемы из логических элементов. Каждая из ветвей диаграммы имеет на каждом плане свои используемые объекты, то есть каждая ветвь состоит из иерархического множества объектов.

Переход от поведенческой ветви к структурной называется синтезом (синтезировать схему). Переход от структурной ветви к геометрической называют генерацией, или компиляцией. Переход по ветви диаграммы от объектов расположенных на более высоком иерархическом уровне к объектам на менее высоком иерархическом уровне называется детализацией. Поведенческая ветвь содержит:

– Техническое задание, где описываются требования к разрабатываемому устройству;

– Алгоритмы;

– Регистровые передачи, определяет совокупность используемых регистров и последовательность пересылки информации в них. На этом уровне используется язык RTL - (Register Transfer Language), представляющем собой Ассемблер, не зависящий от команд конкретного процессора.

– Булевы уравнения

– Дифференциальные уравнения.

Структурная ветвь:

– Процессорные блоки. На этом уровне определяется используемая архитектура вычислителя, ее виды и особенности.

– Подсистемы. Данный объект предполагает описание вычислительного ядра в виде набора функциональных модулей, так называемый PMS модели. Кроме процессора и памяти рассматриваются и иные функциональные модули.

– Модули. Этот объект определяет, как реализуются отдельные объекты предыдущего плана.

– Вентили – решаются вопросы реализации модулей с помощью вентелей.

– Транзисторы.

Геометрическая ветвь

– Разделы – представляют собой размещение проекта на кристаллах;

– Блоки, определяют на какие блоки разделяется площадь кристаллов.

– Компоновочный план является детализацией блоков и показывает, какие элементы кристалла, каким образом составляют блоки.

– Ячейки – определяют топологию использования типовых элементов (вентели, транзисторы)

– Шаблоны, на этом уровне решаются вопросы построения фотошаблонов для производства интегральных схем (фотошаблон является наиболее дорогостоящей частью проекта).

42. Инструментальное программное обеспечение процесса проектирования. Современная тенденция - переориентация ведущих разработчиков САПР с дорогих и поэтому имеющих ограниченное распространение рабочих станций на дешевые персональные компьютеры способствует расширению областей применения автоматизированного проектирования.

Для оценки современного состояния проблемы проектирования электронных систем приведем некоторые количественные характеристики больших проектов:

для схем ASIC (Application Specific Integrated Circuits)— более 20 млн вентилей в кристалле, для ПЛИС — более 5 млн вентилей;

для описания поведения проекта на системном уровне требуется более 0,5 млн строк кода на языке СИ;

при описании проекта на уровне регистровых передач используется более 5 млн строк кода RTL.

Платформа — комплекс аппаратно-программных средств, который необходим для решения конкретной задачи разработчика. Понятие платформы включает не только набор скомпонованных и взаимно состыкованных средств, но и методику проектирования на его основе.

Средства системного этапа проектирования

Как уже отмечалось (см. рис. 12.2), проектирование начинается с системного этапа, на котором формируются основные идеи проекта и анализируется его реализуемость. Определяются ориентировочные затраты и стоимость конечного продукта. Выбирается платформа проектирования. Именно здесь закладывается набор требуемых далее средств. Выполнение работ этого этапа очень плохо поддается автоматизации.

Результатом этого этапа является спецификация проекта. Под спецификацией понимают краткое описание значимых аспектов системы.

Средства разработки процессорной части проекта

При разбиении проекта разработчик, прежде всего, оценивает целесообразность применения процессорного блока со стандартной архитектурой. Наличие процессора позволяет попытаться возложить именно на него решение большинства задач проекта. Практическая невозможность поручить процессору решение всех задач заставляет выделить специфические задачи, которые (как уже отмечалось ранее) могут быть отнесены к одной из двух групп со специфическим подходом к их решению. К первым относятся задачи, требующие аналоговой и аналого-цифровой обработки. Ко вторым — задачи, связанные с быстродействием, не поддерживаемым выбранным типом МП.

Самая ответственная задача в разработке МПС — разработка программного обеспечения. Отладка может ориентироваться на работу с виртуальным прототипом (моделью), с физическим прототипом или с конечной продукцией.

Отладка на модели — способ, доступный с самых начальных этапов проектирования. Достоинство метода— наблюдаемость (видимость) и управляемость всеми объектами модели.

Отладка на прототипе — способ получения наиболее достоверных данных о работе разработанного программного обеспечения в его взаимодействии с аппаратурой системы и внешней средой.

Принципы построения симметричных и несимметричных линий связи. См 17

Реализация симметричных линий связи в RS-485. См 17

45. Классификация, особенности применения, преимущества и недостатки программируемых логических микросхем. Конфигурационная память. Самыми уязвимыми для взломщиков являются схемы с триггерной памятью конфигурации, которую нужно загружать при каждом включении питания от внешнего источника хранимых данных. Для клонирования проекта достаточно прочитать содержимое этой внешней памяти и использовать его для конфигурирования клонов. Установление соответствия недокументированного битового потока конфигурирования и внутренней структуры схемы (реконструкция проекта) является более сложным, но не считается невозможным. С целью повышения защищенности проектов с триггерной памятью конфигурации, принимается ряд мер: организационных, юридических, конструктивных и др.

К организационным мерам можно отнести поставку немаркированных кристаллов, что существенно затрудняет попытки взлома проектов; к юридическим — встраивание в проект некоторого недокументированного идентификатора; к конструктивным — покрытие кристалла и его связей с другими кристаллами непроницаемым слоем, например, эпоксидной смолой (это имеет и отрицательные последствия, не позволяя в дальнейшем дорабатывать проект и ухудшая тепловой режим кристалла). Возможно и размещение трассы передачи битового потока конфигурирования между энергонезависимой памятью и микросхемой в скрытых внутренних слоях печатной платы.

Можно вообще обойтись без энергонезависимой памяти конфигурирования, если разместить на плате автономный источник питания (литиевую батарею), сохраняющий запрограммированную конфигурацию в триггерной памяти. Однако в этой ситуации потребуются специальные схемы для изоляции источника автономно питания от всех цепей, кроме памяти конфигурации, и, кроме того, при истошении батареи схема все же разрушится. Разрушение может произойти и от мгновенной потери питания вследствие удара, действия помехи и т. д.

Большое распространение получило шифрование данных конфигурации. В этом случае на схему передается поток зашифрованных данных, который преобразуется в данные конфигурирования устройством дешифрации, находящимся на кристалле. Для этих целей используют генераторы и анализаторы CRC (Cyclic Redundance Code) и шифрование ведется по стандартам, обеспечивающим высокую засекреченность данных.

Способ конфигурирования ПЛИС, т. е. настройки микросхем на определенное функционирование, зависит от типа программируемых элементов (ПЭ). Микросхемы с необратимым изменением состояний перемычек (antifuse) и с энергонезависимой памятью конфигурации (EPROM, EEPROM, Flash) программируются электрическими сигналами, отличающимися от рабочих. Конфигурирование таких микросхем производится вне системы с помощью программаторов или же (для вариантов с EEPROM и Flash) в ее составе (т. е. при сохранении монтажа микросхемы на плате).

Загрузка триггерной памяти конфигурации не требует специальных режимов, и конфигурирование состоит в обычной передаче в микросхему информации по заданному протоколу и с фиксированными форматами данных. Эта информация обеспечивает создание требуемых связей в логических блоках, блоках ввода/вывода и системе межсоединений. Конфигурирование выполняется после каждого включения питания, причем, если установлены специальные загрузочные БИС, сам факт очередного включения питания автоматически инициирует процесс конфигурирования, который может повторяться неограниченное число раз. Память конфигурации можно загружать в работающей схеме, причем возможна и частичная реконфигурация схемы. При конфигурировании каждый бит настроечных дан ных задает состояние соответствующему триггеру, управляющему программируй мым ключом в настраиваемой схеме. + см 21 с **

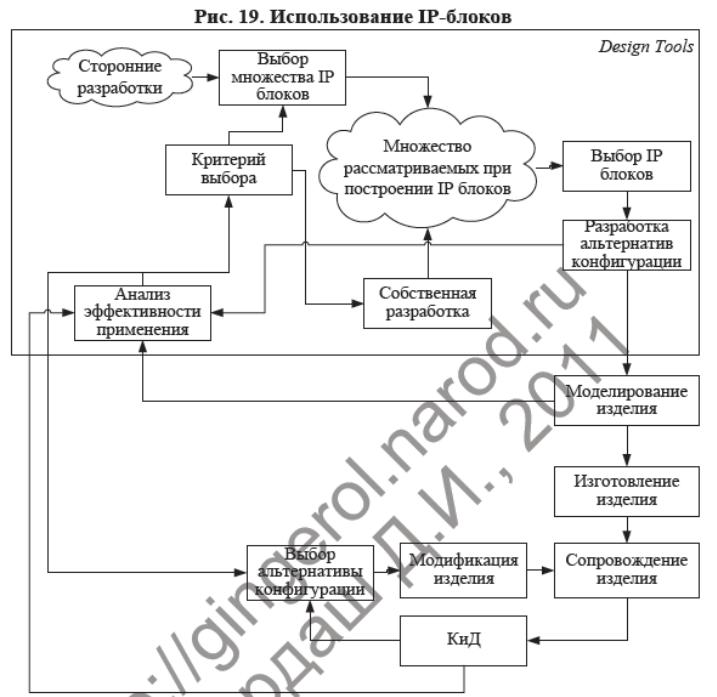

Использование IP-блоков.

IP cores (IP-ядра) (от англ. Intellectual Property — интеллектуальный продукт. Также IP-блоки; также англ. virtual components, VC — виртуальные компоненты) — готовые блоки для проектирования микросхем (например, построения систем-на-кристалле).

Различают 3 основных класса блоков:

программные IP-блоки (англ. soft blocks) — блоки, специфицированные на языке описания аппаратуры.

схемотехнические блоки (англ. firm blocks) — блоки, специфицированные на схемотехническом уровне, без привязки к конкретной топологической реализации.

физические (топологические) блоки (англ. hards blocks) — блоки, специфицированные на физическом уровне реализации СБИС, например, GDSII для ASIC.

Hard IP-Core — сложно-функциональный блок, передаваемый потребителю в виде законченной схемотехнической конструкции, разработанной на основе базы данных для проектирования изготовителя микросхем и оптимизированной по размерам, потребляемой мощности и электрическим характеристикам.

Hard IP-Core — специализированные области кристалла, выделенные для определенных функций. В этих областях создаются блоки неизменной структуры, спроектированные по методологии ASIC (как области типа БМК или схем со стандартными ячейками), оптимизированные для заданной функции и не имеющие средств ее программирования[1].

В случае использования данного вида ядер размер площади используемой на кристалле — сокращается, улучшаются характеристики быстродействия, но в данном случае происходит потеря универсальности.

При использовании IP -блоков используются следующие функциональные модули:

1) Сторонние разработки

2) Выбор множества IP -блоков

3) Критерий выбора, который показывает, какие IP блоки выбираются

4) Множество рассматриваемых IP -блоков

5) Собственная разработка

6) Анализ эффективности применения

7) Выбор конкретных IP блоков

8) Разработка альтернатив конфигурации

9) Моделирование изделия

10) Изготовление изделия

11) Сопровождение изделия

12) Контроль и диагностика

13) Выбор альтернативы конфигурации

14) Модификация изделия (рис.19)

Структура макроячейки ПЛИС CPLD. См 26

Принципы построения симметричных и несимметричных линий связи. См 43

Диаграмма Гайского-Кана. См 41

Программируемая логическая матрица «И-ИЛИ». См 27