- •Способы организации каналов аналогового ввода (коммутация аналоговых и цифровых сигналов).

- •Обеспечение отказоустойчивости scada системы WinCc.

- •Клиент серверная архитектура scada системы WinCc. 30

- •Уровни стандартизации модулей систем управления. 6

- •5. Модели жизненного цикла аппаратуры. Прототипирование.

- •1.5.1 Модель последовательностного жизненного цикла.

- •Понятия «Система управления», «Внедренная система управления». Модульный принцип построения систем управления.

- •Понятия «Универсальный вычислитель», «Специализированный вычислитель», «Программируемый логический контроллер». Соотнесение процессов универсализации и специализации.

- •Способы программирования. Место программатора при построении систем управления.

- •8.1.2 Внутрисхемное программирование

- •8.1.3 Внутрисистемное программирование

- •8.1.4 Активное программирование

- •8.1.5 Адаптивная система

- •9. Особенности промышленных иус. Понятие «Полевая шина». Требования к специализированным интерфейсам.

- •4.1 Иерархическая структура использования интерфейсов 17

- •10. Логическая реализация интерфейса can.

- •12. Временные характеристики каналов аналогового ввода/вывода.

- •13. Понятие «scada-система», ее основные функции, типичная структура.

- •Клиент-серверная архитектура scada-системы, реализация отказоустойчивости. См. 2,3 вопросы

- •Технология краевого сканирования корпорации jtag.

- •Реализация многовходового логического элемента «и» программируемой логической матрицы. Схема монтажного «и». Структура программируемой логической матрицы на этих элементах.

- •Балансный и небалансный способ передачи сигнала. Реализация балансного способа в сетях на основе rs 485.

- •4.2.3 Реализация симметричных линий связей в rs-485

- •Иерархия интерфейсов интегральных информационно-управляющих систем. Иерархическая структура систем управления производством.

- •Модульная структура scada системы WinCc.

- •Виды внутренних ресурсов программируемых логических интегральных схем. Внутренняя структура программируемых логических интегральных схем.

- •4) Блок программируемой фазовой задержки, или блок формирования фазы

- •8.2.1 Сферы применения

- •8.2.4 Достоинства плис

- •8.2.5 Недостаток плис:

- •Программируемая логическая матрица «и-или».

- •Способы подключения датчиков.

- •Понятие «Система на кристалле» и состав внутренних функциональных модулей.Способы ее построения.

- •Иерархия уровней управления. «Пирамида управления». Иерархическая структура использования интерфейсов. См 18

- •Виды программного обеспечения и альтернативные метафоры программирования.

- •Программно-управляемые вычислительные устройства на базе плис. Интегральные схемы fpslic.

- •Языки описание аппаратуры. Язык vhdl: основные понятия.

- •34. Структура описания vhdl. Виды описаний аппаратуры.

Модульная структура scada системы WinCc.

Понятие и основные функции SCADA систем. См 13 вопрос

Виды внутренних ресурсов программируемых логических интегральных схем. Внутренняя структура программируемых логических интегральных схем.

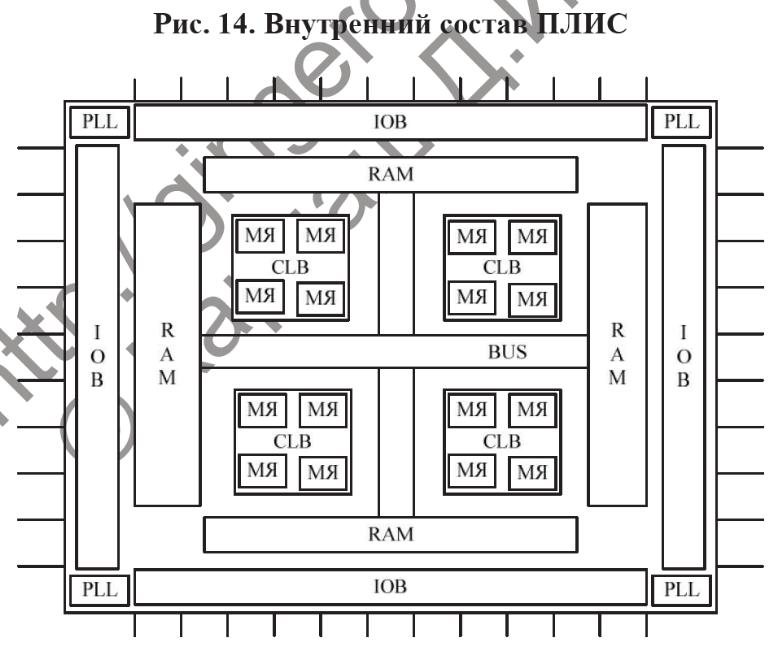

Состав ПЛИС изображен на рисунке 14. Данный рисунок изображает обобщенный состав функциональных блоков для микросхем ПЛИС. Обобщение заключается в том, что не все блоки присутствуют в любой микросхеме, а также не все блоки называются в соответствии с данным рисунком.

Виды внутренних ресурсов: 1) Макроячейка (CPLD) или LUT FPGA; Самая минимальная ячейка ПЛИС – программируемая ячейка (макроячейка в случае CPLD , в случае FPGA – блок LUT. LUT (таблица перекодировки) + триггер).

2) Блок конфигурируемых логических ячеек (CLB) – это объединение множества макроячеек или LUT в рамках единой матрицы. Весь набор базовых элементов (см. п1.) разделяется на равные подгруппы (как правило, 2 или 4 блока) с целью снижения сложности программируемой матрицы.

3) Блок ввода/вывода INPUT/OUTPUT блок – этот блок объединяет элементы в выходную логику макроячеек. Блок предназначен для подключения выходов макроячеек или LUT к ножкам микросхемы, а также определяют логику сигналов (вид логики – уровни напряжений, а также инверсия сигнала). Данных блоков в микросхеме может быть несколько, как и CLB блоков (обычно это число совпадает).

4) Блок программируемой фазовой задержки, или блок формирования фазы

- PLL(PLD) – программируемая защёлка (настраиваем задержку);

- PLL (P-фаза) - программируемый делитель частоты

- PLD – программируемый формирователь фазы сигнала

Данный блок представляет собой управляемый делитель частоты, который формирует полную сетку частот в рамках ПЛИС. Данный блок также имеет функциональную возможность повышать тактовую частоту, приходящую на интегральную схему PLL или DLL присутствуют не во всех интегральных схемах, а лишь в схемах со значительной функциональностью. На вход PLL приходит внешняя тактовая частота, а с выхода PLL мы получаем множество тактовых импульсов доступных всем CLB – тактовый генератор всегда является внешним по отношению к ПЛИС.

5) Блочная оперативная память, или блочная RAM (BRAM) предназначенная для организации и работы макроячеек или LUT и представляет собой конфигурируемый вектор одноразрядных значений. Конфигурация заключается в том, что пользователь сам назначает внутреннюю организацию RAM – разрядность используемых слов. Память является двунаправленной, то есть в одно и то же время можно осуществлять запись и чтение, то есть имеется две адресных шины и две шины данных (одна пара на запись, другая – на чтение). Память реализована как статическое ОЗУ.

6) Шины, предназначенные для обмена информации внутри ПЛИС. Разделение базовых элементов (макроячейки или LUT) на КЛБ предназначено для упрощения логической матрицы. Реализация тех или иных функций проекта пользователя на конкретных макроячейках определяется процессом трассировки.

**Программируемая логическая интегральная схема (ПЛИС, англ. programmable logic device, PLD) — электронный компонент, используемый для создания цифровых интегральных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования).

Для программирования используются программаторы и отладочные среды, позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или программы на специальных языках описания аппаратуры: Verilog, VHDL, AHDL и др.

Альтернативой ПЛИС являются:

– программируемые логические контроллеры (ПЛК),

– базовые матричные кристаллы (БМК), требующие заводского производственного процесса для программирования;

– ASIC — специализированные заказные большие интегральные схемы(БИС), которые при мелкосерийном и единичном производстве существенно дороже; специализированные компьютеры, процессоры (например, цифровой сигнальный процессор) или микроконтроллеры, которые из-за программного способа реализации алгоритмов в работе медленнее ПЛИС.

Некоторые производители ПЛИС предлагают программные процессоры для своих ПЛИС, которые могут быть модифицированы под конкретную задачу, а затем встроены в ПЛИС. Тем самым обеспечивается уменьшение места на печатной плате и упрощение проектирования самой ПЛИС, за счёт быстродействия.