- •1. Системи числення. Переведення чисел із однієї системи числення в іншу.

- •2. Прямий, обернений та додатковий коди. Виконання операції складання (віднімання) в двійковій системі числення.

- •3. Логічні операції та функції. Способи задання функцій. Функціонально повні системи логічних операцій

- •4. Форми запису логічних функцій. Диз'юнктивна (кон'юктивна) нормальна форма

- •5. Мінімізація логічних функцій методом карт Карно. Приклади

- •6. Мінімізація неповністю визначених функцій. Приклад.

- •7. Класифікація цифрових схем та динамічні параметри цифрових елементів

- •Динамічні параметри цифрових мікросхем

- •8. Методика синтезу комбінаційних вузлів з одним виходом у різних базисах. Навести приклад.

- •9. Призначення, класифікація, способи завдання та схеми побудови дешифратора.

- •10. Призначення, способи завдання та побудови шифраторів. Пріоритетні шифратори.

- •11. Призначення, способи завдання та побудови мультиплексорів.

- •12. Призначення, способи завдання та побудови демультиплексорів.

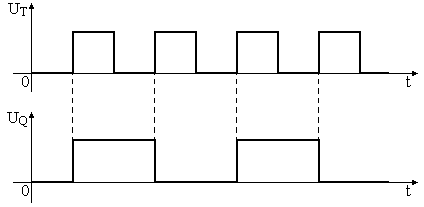

- •13. Асинхронні та синхронні r-s тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

- •14. Синхронні d-тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

- •15. Способи завдання, принципові схеми та часові діаграми роботи j-к та т- тригерів.

- •16. Призначення, класифікація та характеристики регістрів. Паралельні однофазні та парафазні регістри.

- •Классификация регистров

- •Операции в регистрах

- •17. Послідовні регістри. Схеми та робота регістрів зсуву вліво, вправо та реверсивних.

- •18. Призначення, класифікація та характеристики лічильників. Схема двійкового підсумовуючого лічильника із послідовним перенесенням.

- •19. Призначення. Класифікація та характеристики лічильників. Схема двійкового віднімаючого лічильника з послідовним перенесенням.

- •20. Схема кільцевого лічильника.

- •21. Способи та схеми побудови типових недвійкових лічильників та їх характеристики.

14. Синхронні d-тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

D-триггеры также называют триггерами задержки(от англ. Delay).

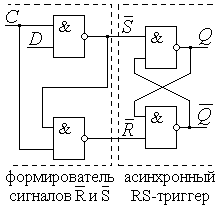

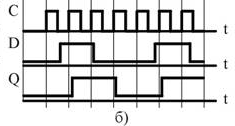

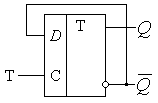

D-триггер синхронный. D-триггер (D от англ. delay — задержка либо от data - данные) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

D |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

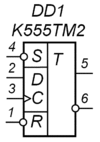

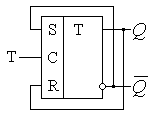

Пример условного графического обозначения (УГО) D-триггера с динамическим синхронным входом С и с дополнительными асинхронными инверсными входами S и R

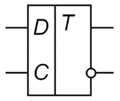

Условное графическое обозначение D-триггера со статическим входом синхронизации С

Рис. 5.7. Структурная схема синхронного D-триггера на элементах И-НЕ

Рис. 3.8. Таблица управления (а) и временные диаграммы (б) D - триггера

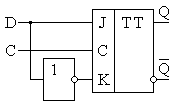

D-триггер двухступенчатый. В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом — две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают ТТ. Двухступенчатый D – триггер называют триггером с динамическим управлением. Общая схема двухступенчатого триггера

15. Способи завдання, принципові схеми та часові діаграми роботи j-к та т- тригерів.

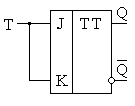

Т-триггер (от англ. Toggle - переключатель) часто называют счётным триггером, так как он является простейшим счётчиком до 2. Асинхронный Т-триггер не имеет входа разрешения счёта - Т и переключается по каждому тактовому импульсу на входе С. Синхронный Т-триггер, при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2.

T |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

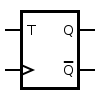

Условное графическое обозначение (УГО) синхронного T-триггера с динамическим входом синхронизации С на схемах.

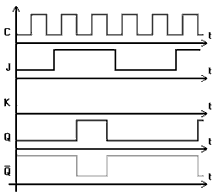

Рис. 5.8. Диаграммы входного и выходного потенциалов T-триггера.

Рис. 5.9. Синтез Т-триггера на базе синхронного RS-триггера и D-триггера.

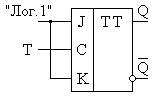

JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен S, вход K (от англ. Kill — убить) аналогичен входу R. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры. На базе JK-триггера возможно построить D-триггер или Т-триггер.

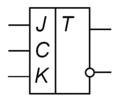

Условное графическое обозначение JK-триггера со статическим входом С

Алгоритм функционирования JK-триггера можно представить формулой

![]()

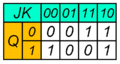

Карта Карно JK-триггера для Q(t+1)

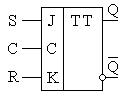

Рис. 5.12. Реализация триггеров различных типов на базе JK-триггера.