- •1. Системи числення. Переведення чисел із однієї системи числення в іншу.

- •2. Прямий, обернений та додатковий коди. Виконання операції складання (віднімання) в двійковій системі числення.

- •3. Логічні операції та функції. Способи задання функцій. Функціонально повні системи логічних операцій

- •4. Форми запису логічних функцій. Диз'юнктивна (кон'юктивна) нормальна форма

- •5. Мінімізація логічних функцій методом карт Карно. Приклади

- •6. Мінімізація неповністю визначених функцій. Приклад.

- •7. Класифікація цифрових схем та динамічні параметри цифрових елементів

- •Динамічні параметри цифрових мікросхем

- •8. Методика синтезу комбінаційних вузлів з одним виходом у різних базисах. Навести приклад.

- •9. Призначення, класифікація, способи завдання та схеми побудови дешифратора.

- •10. Призначення, способи завдання та побудови шифраторів. Пріоритетні шифратори.

- •11. Призначення, способи завдання та побудови мультиплексорів.

- •12. Призначення, способи завдання та побудови демультиплексорів.

- •13. Асинхронні та синхронні r-s тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

- •14. Синхронні d-тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

- •15. Способи завдання, принципові схеми та часові діаграми роботи j-к та т- тригерів.

- •16. Призначення, класифікація та характеристики регістрів. Паралельні однофазні та парафазні регістри.

- •Классификация регистров

- •Операции в регистрах

- •17. Послідовні регістри. Схеми та робота регістрів зсуву вліво, вправо та реверсивних.

- •18. Призначення, класифікація та характеристики лічильників. Схема двійкового підсумовуючого лічильника із послідовним перенесенням.

- •19. Призначення. Класифікація та характеристики лічильників. Схема двійкового віднімаючого лічильника з послідовним перенесенням.

- •20. Схема кільцевого лічильника.

- •21. Способи та схеми побудови типових недвійкових лічильників та їх характеристики.

11. Призначення, способи завдання та побудови мультиплексорів.

Mультиплексор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передавать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

Использование. Мультиплексоры могут использоваться в делителях частоты, триггерных устройствах, сдвигающих устройствах и др. Мультиплексоры могут использоваться для преобразования параллельного двоичного кода в последовательный. Для такого преобразования достаточно подать на информационные входы мультиплексора параллельный двоичный код, а сигналы на адресные входы подавать в такой последовательности, чтобы к выходу поочередно подключались входы, начиная с первого и заканчивая последним.

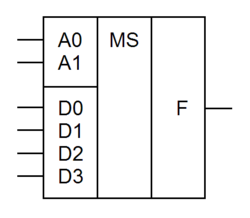

Условное графическое обозначение (УГО) мультиплексора «4 в 1».

Рис. 4.12. Условное обозначение мультиплексора на принципиальных схемах

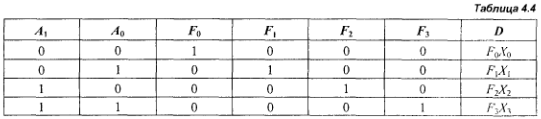

На

основе табл. 4.4. выражение для выходной

функции О

можно представить с использованием

выходов F0-F3

внутреннего дешифратора в виде

![]() или

с минтермами адресного кода:

или

с минтермами адресного кода:

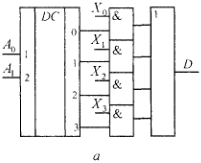

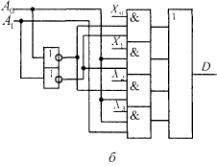

![]() Схемы

мультиплексоров, соответствующие

уравнениям показаны на рис. 4.13.

Схемы

мультиплексоров, соответствующие

уравнениям показаны на рис. 4.13.

Рис. 4.13. Схемы мультиплексоров: a — с внутренним дешифратором; б — с адресными минтермами

12. Призначення, способи завдання та побудови демультиплексорів.

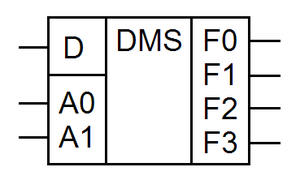

Демультиплексор — это логическое устройство, предназначенное для переключения сигнала (за доп. адресного коду A0, A1, …, Am-1) с одного информационного входа на один из информационных выходов. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. На схемах демультиплексоры обозначают через DMX или DMS.

Условное графическое обозначение (УГО) демультиплексора «1 в 4».

Условное графическое обозначение (УГО) демультиплексора «1 в 4».

Демультиплексоры используют для следующих операций:

коммутации как отдельных линий, так и многоразрядных шин;

преобразования последовательного кода в параллельный;

реализации логических функций и др.

Демультиплексоры часто обозначают: “1 ->п”. D — информационный вход; F0, F1, F2, F3 — выходы внутреннего дешифратора адреса.

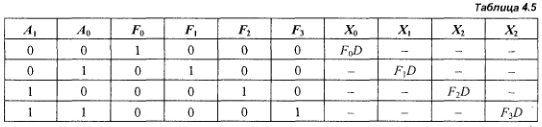

По данным табл 4.5 записываем систему уравнений для информационных выходов:

![]()

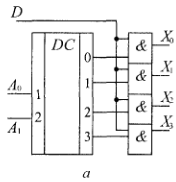

На основе уравнений построены схемы.

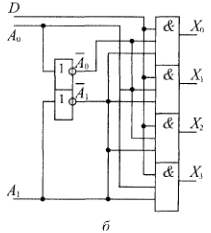

Рис. 4.18. Схема демультиплексоров: а — с внутренним дешифратором; б — с совмещением адресных и входных переменных

13. Асинхронні та синхронні r-s тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

Двовходовий асинхронний RS-тригер – це тригер з прямими (такими, що реагують на наявність 1) й інверсними (такими, що реагують на наявність 0) входами.

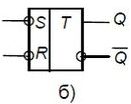

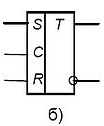

Умовне позначення RS-тригера наведено на рис.1.

Рисунок 1 – Умовні позначення RS-тригера з прямими (а) й інверсними (б) входами

Свою назву RS–тригер одержав від перших літер англійських слів set – встановлювати (S) та reset – відновлювати (R).

S – інформаційний вхід призначений для установлення тригера в одиничний стан (Q = 1), а R – вхід призначений для повернення тригера у нульовий стан (Q = 0).

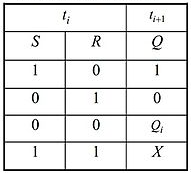

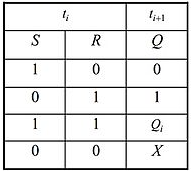

Таблиці переходів

Роботу тригерів описують відповідні таблиці переходів, наведені в табл.1.

Таблиця 1 - Таблиці переходів RS-тригерів

а) з прямими входами

б) з інверсними входами

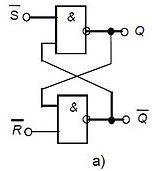

Рисунок 2 – RS-тригер з інверсними входами на елементах І-НІ (а) та з прямими входами на елементах АБО-НІ (б)

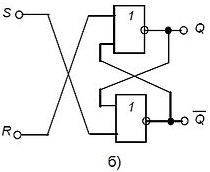

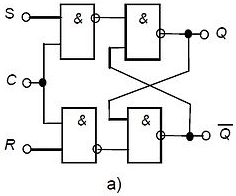

Рисунок 3 – Синхронний RS-тригер

Необхідно зазначити, що тактові входи бувають потенціальні прямі, як у даному випадку (тригер змінює свій стан при надходженні сигналу 1 на вхід С), та інверсні (тригер змінює стан при надходженні сигналу 0), або імпульсні, також прямі й інверсні (коли тригер змінює свій стан при зміні сигналу на тактовому вході з 0 на 1 або з 1 на 0 відповідно).