- •1. Системи числення. Переведення чисел із однієї системи числення в іншу.

- •2. Прямий, обернений та додатковий коди. Виконання операції складання (віднімання) в двійковій системі числення.

- •3. Логічні операції та функції. Способи задання функцій. Функціонально повні системи логічних операцій

- •4. Форми запису логічних функцій. Диз'юнктивна (кон'юктивна) нормальна форма

- •5. Мінімізація логічних функцій методом карт Карно. Приклади

- •6. Мінімізація неповністю визначених функцій. Приклад.

- •7. Класифікація цифрових схем та динамічні параметри цифрових елементів

- •Динамічні параметри цифрових мікросхем

- •8. Методика синтезу комбінаційних вузлів з одним виходом у різних базисах. Навести приклад.

- •9. Призначення, класифікація, способи завдання та схеми побудови дешифратора.

- •10. Призначення, способи завдання та побудови шифраторів. Пріоритетні шифратори.

- •11. Призначення, способи завдання та побудови мультиплексорів.

- •12. Призначення, способи завдання та побудови демультиплексорів.

- •13. Асинхронні та синхронні r-s тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

- •14. Синхронні d-тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

- •15. Способи завдання, принципові схеми та часові діаграми роботи j-к та т- тригерів.

- •16. Призначення, класифікація та характеристики регістрів. Паралельні однофазні та парафазні регістри.

- •Классификация регистров

- •Операции в регистрах

- •17. Послідовні регістри. Схеми та робота регістрів зсуву вліво, вправо та реверсивних.

- •18. Призначення, класифікація та характеристики лічильників. Схема двійкового підсумовуючого лічильника із послідовним перенесенням.

- •19. Призначення. Класифікація та характеристики лічильників. Схема двійкового віднімаючого лічильника з послідовним перенесенням.

- •20. Схема кільцевого лічильника.

- •21. Способи та схеми побудови типових недвійкових лічильників та їх характеристики.

Динамічні параметри цифрових мікросхем

Рис. 2.2 Динамічна характеристика інвертуючої мікросхеми

Основними параметрами динамічних цифрових мікросхем є:

час переходу з стану логічного нуля в стан логічної одиниці –

;

;час переходу з стану логічної одиниці в стан логічного нуля –

;

;час затримки вмикання –

;

;час затримки вимикання –

;

;час затримки поширення при вмиканні – ;

час затримки поширення при вимиканні –

;

;середній час затримки поширення –

;

;тривалість імпульсу –

;

;динамічна завадостійкість;

динамічна потужність;

імпульсна завадостійкість;

робоча частота перемикання.

8. Методика синтезу комбінаційних вузлів з одним виходом у різних базисах. Навести приклад.

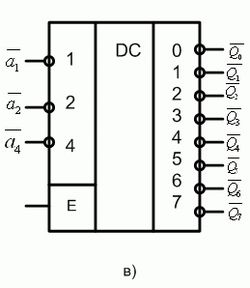

9. Призначення, класифікація, способи завдання та схеми побудови дешифратора.

Дешифра́тор

або деко́дер

(англ.

decoder) —

логічний пристрій, який перетворює код

числа, що поступило на вхід, в сигнал на

одному з його виходів. Якщо число

представлено у вигляді

![]() двійкових

розрядів,

то дешифратор повинен мати

двійкових

розрядів,

то дешифратор повинен мати

![]() виходів.

Дешифратор довільної складності може

бути складено з трьох базових логічних

елементів: кон'юнкції,

диз'юнкції

та заперечення.

виходів.

Дешифратор довільної складності може

бути складено з трьох базових логічних

елементів: кон'юнкції,

диз'юнкції

та заперечення.

Приклад схеми дешифратора 3 на 8

В компьютерах дешифраторы используют для выполнения следующих операций:

дешифрации кода операции, записанного в регистр команд процессора, что обеспечивает выбор требуемой микропрограммы;

преобразования кода адреса операнда в команде в управляющие сигналы выбора заданной ячейки памяти в процессе записи или чтения информации;

обеспечения визуализации на внешних устройствах;

реализации логических операций и построения мультиплексоров и демультиплексоров.

Дешифраторы классифицируют по следующим признакам:

способу структурной организации — одноступенчатые (линейные) и многоступенчатые. в том числе пирамидальные и прямоугольные (матричные);

формату входного кода — двоичные, двоично-десятичные;

разрядности дешифрируемого кода — 2. 3 n;

форме подачи входного кода — с однофазными и парафазными входами;

количеству выходов — полные и неполные дешифраторы;

виду входных стробирующих сигналов — в прямом или инверсном значениях;

типу используемых логических элементов — И, НЕ, ИЛИ, НЕ И, НЕ ИЛИ и т. д.

За принципом дії розрізняють такі види дешифраторів: послідовні, паралельні, паралельно-послідовні.

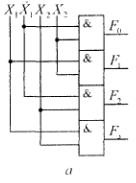

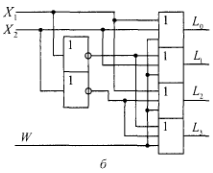

Рис. 4.3. Схемы линейных дешифраторов на элементах И: а — С парафазными входами; б — с однофазными входами и стробированием

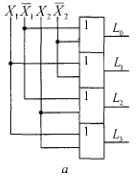

Рис. 4.4. Схема линейных дешифраторов на элементах ИЛИ: а — С парафалными входами; б — с однофазными входами и стробированием

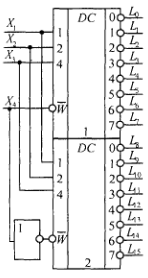

Рис. 4.6. Схема прямоугольного дешифратора

Рис. 4.8. Каскадирование дешифраторов

10. Призначення, способи завдання та побудови шифраторів. Пріоритетні шифратори.

Шифратор (кодер) — (англ. encoder) логическое устройство, выполняющее логическую функцию (операцию) — преобразование позиционного n-разрядного кода в m-разрядный двоичный, троичный или k-ичный код.

Двоичный шифратор выполняет логическую функцию преобразования унитарного n-ичного однозначного кода в двоичный. При подаче сигнала на один из n входов (обязательно на один, не более) на выходе появляется двоичный код номера активного входа.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением:

![]() где

где

![]() —

число входов,

—

число входов,

![]() —

число выходных двоичных разрядов.

—

число выходных двоичных разрядов.

Число входов и выходов в полном k-ичном шифраторе связано соотношением:

![]() ,

где

—

число входов,

—

число выходных k-ичных разрядов,

,

где

—

число входов,

—

число выходных k-ичных разрядов,

![]() —

основание системы

счисления.

—

основание системы

счисления.

В цифровых устройствах шифраторы используются для следующих операций: преобразования унитарного входного кода в выходной двоичный позиционный код; ввода десятичных данных с клавиатуры, указания старшей единицы в слове; передачи информации между различными устройствами при ограниченном числе линий связи.

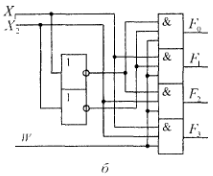

Приоритетный шифратор отличается от шифратора наличием дополнительной логической схемы выделения активного уровня старшего входа для обеспечения условия работоспособности шифратора (только один уровень на входе активный). Уровни сигналов на остальных входах схемой игнорируются.

Рис. 4.9. Условные графические обозначения шифратора на принципиальных схемах

Шифраторы, которые при одновременном нажатии нескольких клавиш вырабатывают код только старшей цифры, называются приоритетными. Приоритетные шифраторы, предназначенные для поиска старшей (левой) единицы в слове и формирования на выходе двоичного номера искомого разряда, называются указателями старшей единицы Их применяют в устройствах нормализации чисел с плавающей запятой, в системах с приоритетным обслуживанием запросов на прерывание работы компьютера.

При

W

=

1 работа схемы блокируется и независимо

от сигналов на входах на инверсных

выходах получаем:

![]() =

111. Если, например,

=

111. Если, например,

![]() = 0 и

= 0 и

![]() =0,

то схема формирует на выходах код номера

входа со старшим приоритетом:

= 001 или в прямом коде Х3Х1Х1

=1102;

= 610.

=0,

то схема формирует на выходах код номера

входа со старшим приоритетом:

= 001 или в прямом коде Х3Х1Х1

=1102;

= 610.