- •«Логічні фрагменти інтегрального виконання»

- •Пояснювальна записка

- •Логічні схеми

- •Для самостійної роботи

- •Л 6 огічні елементи різних серій

- •Поняття тригера

- •Двоступеневі синхронні тригери.

- •З адача 5

- •Регістри

- •Дешифратори

- •Лінійні дешифратори на два входи і чотири виходи

- •Шифратори

- •Лічильники

- •Суматори

- •Завдання

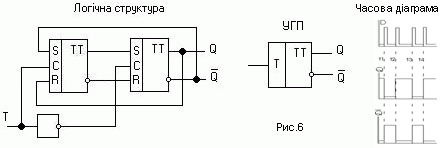

Двоступеневі синхронні тригери.

Розглянуті асинхронні та синхронні однотактнi тригери не можуть задовольнити цілу низку вимог цифрової техніки. Наприклад, в розповсюджених цифрових вузлах - лічильниках i регістрах тригери з'єднуються в ланцюжки послідовно один за одним. По кожному такому ланцюжку відбувається передача цифрової інформації від тригера до тригера в кожному такті на один крок. Тобто, кожен тригер у ланцюжку повинен у даному такті прийняти стан попереднього тригера (записати інформацію, що з нього прийшла) i, одночасно, зберегти свій особистий стан - значення своїх вихідних сигналів, щоб їх зміг сприйняти наступний тригер. Аналогічна ситуація створюється під час побудови логічних структур універсальних JK-тригерів i Т-тригерiв. За допомогою одноступеневих тригерів це зробити неможливо. Для розв'язання такої задачі використовується рознесення в часі етапів прийому (запису) інформації в даний тригер та iї передача в наступний. Очевидно, це можна здійснити впровадженням у схему тригера деякого елемента пам'яті для попереднього запам'ятовування інформації, що надходить (вхідних сигналів). Таким елементом може бути додатковий тригер, що приводить до складнішої схеми ніж двоступеневий тригер. Один тригер тут працює в попередньому ступені, а другий в наступному. Входами двоступеневого тригера є входи першого ступеня, а виходами - виходи другого ступеня. Внутрішні зв'язки першого i другого ступенів дозволяють забезпечити потрібний порядок роботи в кожному такті:

- запис вхідної інформації в запам'ятовуючий тригер першого ступеня з одночасним блокуванням входів тригера другого cтупеня i зберіганням його стану (значення вихідних сигналів Q i Q̅.

- блокування входів тригера першого ступеня з одночасним перезаписом з нього інформації в розблокований тригер другого ступеня. Найпростіше це досягається розділенням такту на дві частини i використанням синхронних тригерів. Виходить двотактне керування двоступеневою схемою.

Однак двотактне керування створює незручності, пов'язані з необхідністю формування двох послідовностей імпульсних синхросигналiв. Запобігти двотактному керуванню i отримати однотактне можливо, якщо між синхровходами першого та другого ступенів поставити інвертор.

11

Двоступеневий синхронний JK-тригер.

J K-тригер

- це універсальний тригер. Він функціонує

за таблицею переходів яка відрізняється

від таблиці переходів RS-тригера тільки

тим, що не має заборонених станів

комбінацій вхідних сигналів. За комбінації

вхідних сигналів J=K=1 i C=1 JK-тригер змінює

свій стан на протилежний. Його

функціонування описується логічним

виразом Q+=JQ̅+K̅Q

K-тригер

- це універсальний тригер. Він функціонує

за таблицею переходів яка відрізняється

від таблиці переходів RS-тригера тільки

тим, що не має заборонених станів

комбінацій вхідних сигналів. За комбінації

вхідних сигналів J=K=1 i C=1 JK-тригер змінює

свій стан на протилежний. Його

функціонування описується логічним

виразом Q+=JQ̅+K̅Q

Таке функціонування JK-тригера забезпечується введенням перехресного зворотного зв'язку в логічну структуру RS-тригера, а входи S i R позначаються як J i K, відповідно.

На рис.5 зображена логічна структура i умовне графічне позначення двоступеневого синхронного JK-тригера. Двоступеневі тригери в УГП позначаються двома літерами Т. За умови лог.0 на вході C тригер Т1 не реагує на сигнали, що діють на входах J i K. На синхронізуючий вхід тригера Т2 за цим подається рівень лог.1, i стан тригера Т1 передається тригеру Т2. Обидва тригери опиняються в одному й тому ж стані. Після переходу на вході C тригера Т1 до рівня лог.1 на синхронізуючий вхід тригера Т2 через інвертор подається рівень лог.0 i логічний зв'язок між тригерами поривається. Тригер Т1 установлюється в стан Q+, який визначається логічним виразом Q+=JQ̅+K̅Q

Подача на вхід С рівня лог.0 приводить до перезапису стану тригера Т1 до тригера Т2.

Двоступеневий Т-тригер.

Т-тригери мають тільки один

вхід i після надходження чергового

сигналу рівня лог.1 на цей вхід змінюють

свій стан на протилежний. Логічна

структура двоступеневого Т-тригера

складається з двох синхронних RS-тригерів

та інвертора

12

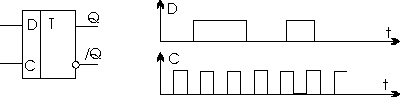

Задача 1

Д ля

D-тригера побудувати

діаграму

вихідної

напруги

Q

для визначених вхідних сигналів

ля

D-тригера побудувати

діаграму

вихідної

напруги

Q

для визначених вхідних сигналів

Задача 2

Д ля D-тригера побудувати діаграму вихідної напруги Q для визначених вхідних сигналів

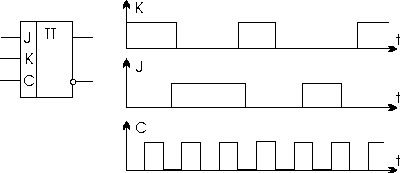

Задача 3

Для JK-тригера визначити послідовність сигналів на виході Q, якщо визначенні вхідні сигнали.

Задача 4

В схемі

з

D-тригером визначити

послідовність сигналів на виході

Q, якщо

на вхід

C поступають

синхроімпульси.

схемі

з

D-тригером визначити

послідовність сигналів на виході

Q, якщо

на вхід

C поступають

синхроімпульси.