- •Самостоятельное изучение

- •Модели и система параметров логических элементов

- •2. Типы выходных каскадов цифровых элементов: логический выход.

- •3. Типы выходных каскадов цифровых элементов: выходы с тремя состояниями.

- •Типы выходных каскадов цифровых элементов: выход с открытым коллектором.

- •Паразитные связи цифровых элементов по цепям питания, фильтрация питающих напряжений в схемах цифровых устройств.

- •6 Типовые ситуации при построении цифровых устройств на имс

- •7 Согласование уровней сигналов. Сопряжение кмоп и тлл схем.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами. (продолжение)

- •9 Элементы индикации

- •9 Элементы индикации (продолжение)

- •10 Риски в комбинационных схемах.

- •11. Дешифраторы, преобразователи кодов

- •12. Шифраторы

- •13. Мультиплексоры.

- •14. Демультиплексоры

- •Компараторы (схемы сравнения).

- •16.Синхронизация в цифровых устройствах.

- •17. Регистры.

- •18. Счетчики. Двоичные счетчики.

- •18. Счетчики. Двоичные счетчики. (продолжение)

- •19. Двоично-кодированные счетчики с произвольным модулем.

- •20. Счетчики с недвоичным кодированием.

- •20. Счетчики с недвоичным кодированием. (продолжение)

- •21. Полиномиальные счетчики.

- •2 1. Полиномиальные счётчики (продолжение)

- •22. Представление чисел с фиксированной запятой.

- •23. Представление чисел с плавающей запятой.

- •24. Погрешности представления чисел.

- •25. Кодирование двоичных чисел со знаком: прямой код

- •26. Кодирование двоичных чисел со знаком: дополнительный код.

- •27. Кодирование двоичных чисел со знаком: обратный код.

- •28. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в прямых кодах. Особенности выполнения операций над числами без знака.

- •29. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в дополнительных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах. (продолжение)

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28]

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28] (продолжение)

- •32.Умножение чисел с фиксированной запятой: общая схема целочисленного умножения. [подробнее с примерами – лекции, стр. 28-3 , но это след. Вопросы]

- •33. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом множимого.

- •34. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом суммы частичных произведений

- •35. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом множимого.

- •36. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом суммы частичных произведений.

- •Умножение двоичных чисел со знаком. Умножение чисел в дополнительном коде.

- •38. Логические методы ускорения умножения: алгоритм Бута.

- •39 Логические методы ускорения умножения: модифицированный алгоритм Бута, алгоритм Лемана

- •40. Логические методы ускорения умножения: умножение с обработкой двух разрядов множителя за шаг (умножение на два разряда одновременно)

- •41.Деление чисел с фиксированной запятой: общая схема целочисленного деления.

- •42. Методы деления двоичных чисел без знака: деление с восстановлением остатка.

- •43. Методы деления двоичных чисел без знака: деление без восстановления остатка.

- •44. Деление двоичных чисел со знаком. Деление чисел в дополнительном коде.

- •Сложение и вычитание двоичных чисел в форме с плавающей запятой.

- •46.Умножение чисел с плавающей запятой.

- •47. Деление чисел с плавающей запятой.

- •48.Выполнение операций сложение и вычитание в двоично-десятичном коде.

- •49.Сложение в двоично-десятичном коде чисел со знаком.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры. (продолжение)

- •51.Арифметико-логические устройства (алу).

9 Элементы индикации (продолжение)

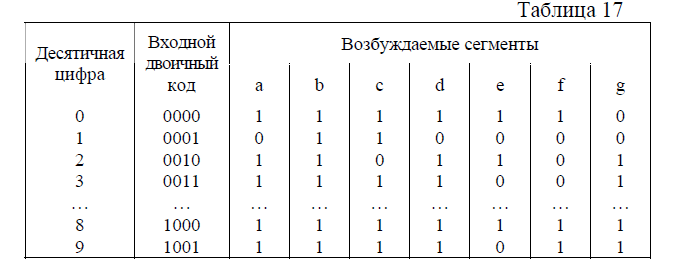

На основе светодиодов изготовляются как семисегментные изображения символов, так и более сложные, отображаемые возбуждением определенных сегментов из поля матрицы. Число строк и столбцов матрицы может быть различным. Принципы формирования изображения при управлении сегментами матрицы те же, что и при управлении ССИ, а именно: входные коды специальным дешифратором преобразуются в сигналы возбуждения отдельных сегментов. При реализации индикаторов многозначных символов, например, содержащих несколько ССИ, удобно использовать мультиплексное управление, при котором одни и те же управляющие схемы поочередно обслуживают различные ССИ, выбирая их в определенной последовательности. При этом каждый индикатор возбуждается импульсно, в течение времени 1/n, где n – число индикаторов. Иллюзия постоянного свечения всех символов создается из-за инерционности человеческого зрения. Если частота возбуждения символов. составляет десятки герц (современные средства визуальной индикации имеют частоты в 70... 100 Гц), то мерцания изображений неощутимы.

10 Риски в комбинационных схемах.

Во время переходных процессов на выходах комбинационных схем появляются временные сигналы, не предусмотренные описанием работы комбинационной цепи и называемые рисками. Со временем они исчезают, и выход комбинационных цепей приобретает значение предусмотренное логической формулой, описывающей работу цепи. Различают статические и динамические риски.Статические риски- это кратковременное изменение сигнала, который должен оставаться неизменным (единичным или нулевым, говорят о 1-риске или 0-риске). Если при работе комбинационной цепи состояние выхода должно измениться, но вместо однократного перехода происходят многократные, то имеет место динамический риск. При динамическом риске первый и последний переходы всегда совпадают с алгоритмическими, предусмотренными логикой работы схемы. Статический риск такого свойства не имеет и поэтому считается более неблагоприятным. Для исключения возможных сбоев в работе из-за явлений риска имеется два пути. Первый состоит в синтезе схем, свободных от рисков, и требует сложного анализа процессов в схеме, введения избыточных элементов для исключения рисков. Второй путь, основанный для современной схемотехники, предусматривает запрещение восприятия сигналов элементами памяти на время переходных процессов. Прием информации с выходов разрешается только специальным сигналом синхронизации, подаваемым на элементы памяти после окончания переходных процессов. Так исключается воздействие ложных сигналов на элементы памяти. Соответствующие структуры называются синхронными.

(Методы, разработанные для устранения рисков сбоя в комбинационных схемах, можно объединить в три группы: структурные, функциональные и конструктивно-технологические. Структурные методы направлены на получение необходимых свойств реализации устройства при неизменном алгоритме его работы. Функциональные методы связаны с изменением алгоритма работы, в частности с изменением кодирования состояний входов. Конструктивно-технологические методы ориентированы на получение требуемых ограничений на уровне используемых математических моделей. Наиболее простыми для соответствующей математической модели являются структурные и функциональные методы, а наиболее сложными конструктивно-технологические, так как они часто связаны с разработкой принципиально новых видов производства интегральных цифровых схем. Структурные методы. При соседней смене входных наборов в комбинационных схемах могут быть устранены статические риски сбоя. В общем случае одной из основных задач синтеза комбинационных схем, свободных от статических рисков сбоя и представленных в дизъюнктивных нормальных формах (ДНФ), будет отыскание таких минимальных покрытий единичных клеток ФАЛ в карте Карно импликантами (контурами на картах Карно), в которых любые соседние единичные клетки покрыты по меньшей мере одной импликантой (контуром). Функциональные методы Здесь используется принцип изменения кодирования последовательных состояний входов комбинационной схемы. К конструктивно-технологическому методу можно отнести метод борьбы с влиянием входных гонок на уровне одного логического элемента, основанный исключительно на совершенствовании технологии изготовления логических элементов и их конструктивного исполнения, которые в совокупности должны обеспечить минимальные разбросы задержки распространения сигналов в элементе по логически одинаковым цепям. В частности, использование интегральной технологии производства ИС, позволяющей получать весьма малые относительные вариации различных параметров, дает возможность считать, что гонки по входу практически не влияют на устойчивость цифровых устройств, проектируемых на любой серии логических ИС.)