- •Самостоятельное изучение

- •Модели и система параметров логических элементов

- •2. Типы выходных каскадов цифровых элементов: логический выход.

- •3. Типы выходных каскадов цифровых элементов: выходы с тремя состояниями.

- •Типы выходных каскадов цифровых элементов: выход с открытым коллектором.

- •Паразитные связи цифровых элементов по цепям питания, фильтрация питающих напряжений в схемах цифровых устройств.

- •6 Типовые ситуации при построении цифровых устройств на имс

- •7 Согласование уровней сигналов. Сопряжение кмоп и тлл схем.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами. (продолжение)

- •9 Элементы индикации

- •9 Элементы индикации (продолжение)

- •10 Риски в комбинационных схемах.

- •11. Дешифраторы, преобразователи кодов

- •12. Шифраторы

- •13. Мультиплексоры.

- •14. Демультиплексоры

- •Компараторы (схемы сравнения).

- •16.Синхронизация в цифровых устройствах.

- •17. Регистры.

- •18. Счетчики. Двоичные счетчики.

- •18. Счетчики. Двоичные счетчики. (продолжение)

- •19. Двоично-кодированные счетчики с произвольным модулем.

- •20. Счетчики с недвоичным кодированием.

- •20. Счетчики с недвоичным кодированием. (продолжение)

- •21. Полиномиальные счетчики.

- •2 1. Полиномиальные счётчики (продолжение)

- •22. Представление чисел с фиксированной запятой.

- •23. Представление чисел с плавающей запятой.

- •24. Погрешности представления чисел.

- •25. Кодирование двоичных чисел со знаком: прямой код

- •26. Кодирование двоичных чисел со знаком: дополнительный код.

- •27. Кодирование двоичных чисел со знаком: обратный код.

- •28. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в прямых кодах. Особенности выполнения операций над числами без знака.

- •29. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в дополнительных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах. (продолжение)

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28]

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28] (продолжение)

- •32.Умножение чисел с фиксированной запятой: общая схема целочисленного умножения. [подробнее с примерами – лекции, стр. 28-3 , но это след. Вопросы]

- •33. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом множимого.

- •34. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом суммы частичных произведений

- •35. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом множимого.

- •36. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом суммы частичных произведений.

- •Умножение двоичных чисел со знаком. Умножение чисел в дополнительном коде.

- •38. Логические методы ускорения умножения: алгоритм Бута.

- •39 Логические методы ускорения умножения: модифицированный алгоритм Бута, алгоритм Лемана

- •40. Логические методы ускорения умножения: умножение с обработкой двух разрядов множителя за шаг (умножение на два разряда одновременно)

- •41.Деление чисел с фиксированной запятой: общая схема целочисленного деления.

- •42. Методы деления двоичных чисел без знака: деление с восстановлением остатка.

- •43. Методы деления двоичных чисел без знака: деление без восстановления остатка.

- •44. Деление двоичных чисел со знаком. Деление чисел в дополнительном коде.

- •Сложение и вычитание двоичных чисел в форме с плавающей запятой.

- •46.Умножение чисел с плавающей запятой.

- •47. Деление чисел с плавающей запятой.

- •48.Выполнение операций сложение и вычитание в двоично-десятичном коде.

- •49.Сложение в двоично-десятичном коде чисел со знаком.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры. (продолжение)

- •51.Арифметико-логические устройства (алу).

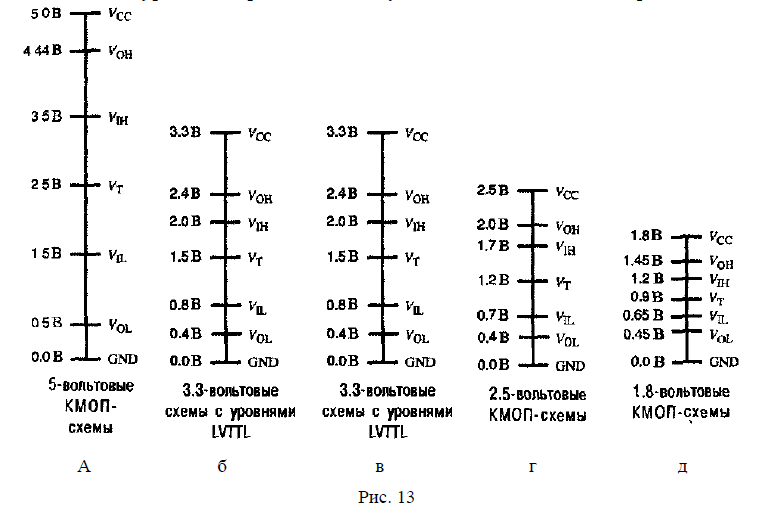

8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами. (продолжение)

Преобразователи

уровней выпускаются также в виде

отдельных к омпонентов.

Следующим шагом

является переход от 2,5-вольтовой логики

к 1,8- вольтовой. Из рис. 13, г и д можно

видеть, что запас помехоустойчивости

по постоянному току при высоком уровне

фактически отрицателен, когда сигнал

с выхода 1,8-вольтовой схемы поступает

на вход 2,5-вольтовой схемы. Поэтому

преобразователи уровня необходимы

также и в этом случае.

омпонентов.

Следующим шагом

является переход от 2,5-вольтовой логики

к 1,8- вольтовой. Из рис. 13, г и д можно

видеть, что запас помехоустойчивости

по постоянному току при высоком уровне

фактически отрицателен, когда сигнал

с выхода 1,8-вольтовой схемы поступает

на вход 2,5-вольтовой схемы. Поэтому

преобразователи уровня необходимы

также и в этом случае.

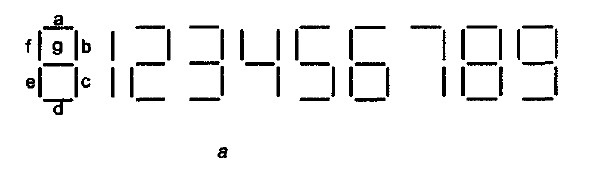

9 Элементы индикации

Д

ля

общения с оператором ЦУ могут снабжаться

средствами визуальной индикации

символьных данных. Среди них имеются и

сложные устройства, такие как экранные

дисплеи, и простые, такие как светодиодные

индикаторы или матрицы. Преобразование

электрических сигналов в видимое

изображение может быть основано на

разных физических явлениях: светоизлучении

полупроводниковых структур, оптических

явлениях в жидких кристаллах,

электролюминесценции, процессах в

газовом разряде и др. Светодиоды

изготовляются на основе полупроводниковых

материалов (арсенида галлия, фосфида

галлия, арсенид-фосфида галлия и др.),

пропускание тока через которые вызывает

их свечение. Яркость свечения светодиода

непосредственно

зависит от величины тока. Обычно

достаточны токи от единиц до приблизительно

двадцати миллиампер при падении

напряжения на диоде около 1...2 В. Как

правило, последовательно со светодиодом

включается резистор, задающий и

стабилизирующий ток диода. Из

нескольких диодов составляются индикаторы

и матрицы, отображающие буквы и цифры.

Широко применяются семисегментные

индикаторы, в которых семь сегментов-диодов

расположены так, что при зажигании

определенной их комбинации высвечивается

тот или иной символ (рис. 46, а).

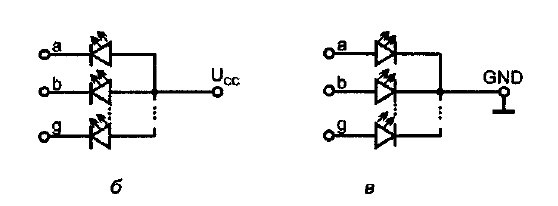

Выпускаются

семисегментные индикаторы (ССИ) с общим

анодом или общим катодом (рис. 46, б, в).

Для зажигания

сегмента в схеме с общим анодом,

подключенным к источнику питания Ucc,

нужно снизить напряжение на его катоде

(зажигание сигналом логического нуля).

Для зажигания сегмента в схеме с общим

катодом, подключенным к общей точке

схемы, необходимо повысить напряжение

на его аноде (зажигание сигналом

логической единицы). Для управления

сегментами удобны элементы с выходом

типа ОК, поскольку при их использовании

имеется внешняя цепочка с резистором,

сопротивление которого можно задать с

учетом характеристик применяемых

светодиодов. В

схеме (рис. 47, а) показано управление

одним из сегментов ССИ. Диод зажигается,

когда на выходе управляющего элемента

напряжение равно U0. Через диод будет

протекать ток Iд = (Uсс - Uд - U0)/R, следовательно,

для его задания требуется условие R =

(Uсс - Uд - U0)/Iд. Для этой схемы требуются

ССИ с общим анодом. Необходим управляющий

элемент с достаточно большим выходным

током в нулевом состоянии (Iвых.0 ≥ Iд).

В схеме (рис. 47, б)

диод зажигается, когда выходной транзистор

управляющего элемента запирается. Через

диод течет ток Iд = (Uсс - Uд)/R, откуда

следует R = (Uсс - Uд)/Iд. Для этой схемы

требуется ССИ с общим катодом. Выход

управляющего элемента должен удовлетворять

условию Iвых.0 ≥ (Uсс - U0)/R. Для

логического управления ССИ имеются

стандартные ИС дешифраторов для ССИ,

работающие согласно табл. 17.

ля

общения с оператором ЦУ могут снабжаться

средствами визуальной индикации

символьных данных. Среди них имеются и

сложные устройства, такие как экранные

дисплеи, и простые, такие как светодиодные

индикаторы или матрицы. Преобразование

электрических сигналов в видимое

изображение может быть основано на

разных физических явлениях: светоизлучении

полупроводниковых структур, оптических

явлениях в жидких кристаллах,

электролюминесценции, процессах в

газовом разряде и др. Светодиоды

изготовляются на основе полупроводниковых

материалов (арсенида галлия, фосфида

галлия, арсенид-фосфида галлия и др.),

пропускание тока через которые вызывает

их свечение. Яркость свечения светодиода

непосредственно

зависит от величины тока. Обычно

достаточны токи от единиц до приблизительно

двадцати миллиампер при падении

напряжения на диоде около 1...2 В. Как

правило, последовательно со светодиодом

включается резистор, задающий и

стабилизирующий ток диода. Из

нескольких диодов составляются индикаторы

и матрицы, отображающие буквы и цифры.

Широко применяются семисегментные

индикаторы, в которых семь сегментов-диодов

расположены так, что при зажигании

определенной их комбинации высвечивается

тот или иной символ (рис. 46, а).

Выпускаются

семисегментные индикаторы (ССИ) с общим

анодом или общим катодом (рис. 46, б, в).

Для зажигания

сегмента в схеме с общим анодом,

подключенным к источнику питания Ucc,

нужно снизить напряжение на его катоде

(зажигание сигналом логического нуля).

Для зажигания сегмента в схеме с общим

катодом, подключенным к общей точке

схемы, необходимо повысить напряжение

на его аноде (зажигание сигналом

логической единицы). Для управления

сегментами удобны элементы с выходом

типа ОК, поскольку при их использовании

имеется внешняя цепочка с резистором,

сопротивление которого можно задать с

учетом характеристик применяемых

светодиодов. В

схеме (рис. 47, а) показано управление

одним из сегментов ССИ. Диод зажигается,

когда на выходе управляющего элемента

напряжение равно U0. Через диод будет

протекать ток Iд = (Uсс - Uд - U0)/R, следовательно,

для его задания требуется условие R =

(Uсс - Uд - U0)/Iд. Для этой схемы требуются

ССИ с общим анодом. Необходим управляющий

элемент с достаточно большим выходным

током в нулевом состоянии (Iвых.0 ≥ Iд).

В схеме (рис. 47, б)

диод зажигается, когда выходной транзистор

управляющего элемента запирается. Через

диод течет ток Iд = (Uсс - Uд)/R, откуда

следует R = (Uсс - Uд)/Iд. Для этой схемы

требуется ССИ с общим катодом. Выход

управляющего элемента должен удовлетворять

условию Iвых.0 ≥ (Uсс - U0)/R. Для

логического управления ССИ имеются

стандартные ИС дешифраторов для ССИ,

работающие согласно табл. 17.