- •Самостоятельное изучение

- •Модели и система параметров логических элементов

- •2. Типы выходных каскадов цифровых элементов: логический выход.

- •3. Типы выходных каскадов цифровых элементов: выходы с тремя состояниями.

- •Типы выходных каскадов цифровых элементов: выход с открытым коллектором.

- •Паразитные связи цифровых элементов по цепям питания, фильтрация питающих напряжений в схемах цифровых устройств.

- •6 Типовые ситуации при построении цифровых устройств на имс

- •7 Согласование уровней сигналов. Сопряжение кмоп и тлл схем.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами. (продолжение)

- •9 Элементы индикации

- •9 Элементы индикации (продолжение)

- •10 Риски в комбинационных схемах.

- •11. Дешифраторы, преобразователи кодов

- •12. Шифраторы

- •13. Мультиплексоры.

- •14. Демультиплексоры

- •Компараторы (схемы сравнения).

- •16.Синхронизация в цифровых устройствах.

- •17. Регистры.

- •18. Счетчики. Двоичные счетчики.

- •18. Счетчики. Двоичные счетчики. (продолжение)

- •19. Двоично-кодированные счетчики с произвольным модулем.

- •20. Счетчики с недвоичным кодированием.

- •20. Счетчики с недвоичным кодированием. (продолжение)

- •21. Полиномиальные счетчики.

- •2 1. Полиномиальные счётчики (продолжение)

- •22. Представление чисел с фиксированной запятой.

- •23. Представление чисел с плавающей запятой.

- •24. Погрешности представления чисел.

- •25. Кодирование двоичных чисел со знаком: прямой код

- •26. Кодирование двоичных чисел со знаком: дополнительный код.

- •27. Кодирование двоичных чисел со знаком: обратный код.

- •28. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в прямых кодах. Особенности выполнения операций над числами без знака.

- •29. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в дополнительных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах. (продолжение)

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28]

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28] (продолжение)

- •32.Умножение чисел с фиксированной запятой: общая схема целочисленного умножения. [подробнее с примерами – лекции, стр. 28-3 , но это след. Вопросы]

- •33. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом множимого.

- •34. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом суммы частичных произведений

- •35. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом множимого.

- •36. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом суммы частичных произведений.

- •Умножение двоичных чисел со знаком. Умножение чисел в дополнительном коде.

- •38. Логические методы ускорения умножения: алгоритм Бута.

- •39 Логические методы ускорения умножения: модифицированный алгоритм Бута, алгоритм Лемана

- •40. Логические методы ускорения умножения: умножение с обработкой двух разрядов множителя за шаг (умножение на два разряда одновременно)

- •41.Деление чисел с фиксированной запятой: общая схема целочисленного деления.

- •42. Методы деления двоичных чисел без знака: деление с восстановлением остатка.

- •43. Методы деления двоичных чисел без знака: деление без восстановления остатка.

- •44. Деление двоичных чисел со знаком. Деление чисел в дополнительном коде.

- •Сложение и вычитание двоичных чисел в форме с плавающей запятой.

- •46.Умножение чисел с плавающей запятой.

- •47. Деление чисел с плавающей запятой.

- •48.Выполнение операций сложение и вычитание в двоично-десятичном коде.

- •49.Сложение в двоично-десятичном коде чисел со знаком.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры. (продолжение)

- •51.Арифметико-логические устройства (алу).

50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры.

Основной элементарной операцией, выполняемой над кодами чисел в цифровых устройствах, является арифметическое сложение.

Сумматор — логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное. Указанные операции выполняются в арифметическо-логических устройствах (АЛУ) или процессорных элементах, ядром которых являются сумматоры.

По количеству одновременно обрабатываемых разрядов складываемых чисел:

одноразрядные,

многоразрядные.

Одноразрядные двоичные сумматоры

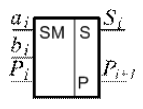

Сумматор SM служит для образования сигнала суммы Si по сигналам трех цифр аi, вi и рi i-го разряда и формирования сигнала переноса рi+1 в следующий старший разряд.

Одноразрядный цифровой сумматор имеет три входа: два входа слагаемых и вход переноса (от предыдущего сумматора).

Одноразрядный сумматор принято обозначать на схемах в следующем виде:

Сумматор имеет входы ai и bi - слагаемые, pi - вход переноса, Si - выход суммы, pi+1 - выход переноса. Табличка истинности:

входы |

выходы |

||||||

слагаемые |

вход переноса |

сумма |

выход переноса |

||||

ai |

bi |

pi |

Si |

pi+1 |

|||

0 |

0 |

0 |

0 |

0 |

|||

0 |

1 |

0 |

1 |

0 |

|||

1 |

0 |

0 |

1 |

0 |

|||

1 |

1 |

0 |

0 |

1 |

|||

0 |

0 |

1 |

1 |

0 |

|||

0 |

1 |

1 |

0 |

1 |

|||

1 |

0 |

1 |

0 |

1 |

|||

1 |

1 |

1 |

1 |

1 |

|||

На выходе Si представляется сумма сложения трех переменных - аi, вi и рi. При переполнении сумматора, т. е. когда в результате сложения формируется единица в старшем разряде выходного числа, на выходе переноса pi+1 формируется уровень лог. 1, который подается на вход переноса рi следующего сумматора. В принципе, старшим разрядом суммы является выход переноса pi+1. В целом работу сумматора полностью иллюстрирует таблица. Из таких одноразрядных сумматоров составляются многоразрядные сумматоры (обычно 4-х разрядные), которые бывают последовательного и параллельного действия. Сумматоры последовательного действия обладают более низким быстродействием.

50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры. (продолжение)

Многоразрядные сумматоры

Многоразрядный сумматор представляет собой комбинацию одноразрядных трехвыходовых сумматоров.

В зависимости от того, каким образом в ЭВМ передаются числа, может быть два способа сложения: последовательный и параллельный. При последовательном способе сложения при передаче каждого слагаемого используется один канал, по которому код числа передается в виде временной последовательности цифр разряд за разрядом. Если для передачи каждого разряда числа предусмотрен отдельный канал, то применяется параллельный способ сложения.

Последовательный сумматор в простейшем случае представляет собой n одноразрядных сумматоров, последовательно (от младших разрядов к старшим) соединенных цепями переноса. Такой сумматор называется сумматором с последовательным переносом. Однако такая схема сумматора характеризуется

сравнительно невысоким быстродействием, так как формирование сигналов суммы и переноса в каждом i-м разряде производится лишь после того, как поступит сигнал переноса с (i-1)-го разряда. Таким образом, быстродействие сумматора определяется временем распространения сигнала по цепи переноса.

Уменьшение этого времени достигается при построении параллельных сумматоров. Сумматоры с параллельным переносом не имеют последовательного распространения переноса вдоль разрядной сетки. Во всех разрядах результаты вырабатываются одновременно, параллельно во времени.