- •Самостоятельное изучение

- •Модели и система параметров логических элементов

- •2. Типы выходных каскадов цифровых элементов: логический выход.

- •3. Типы выходных каскадов цифровых элементов: выходы с тремя состояниями.

- •Типы выходных каскадов цифровых элементов: выход с открытым коллектором.

- •Паразитные связи цифровых элементов по цепям питания, фильтрация питающих напряжений в схемах цифровых устройств.

- •6 Типовые ситуации при построении цифровых устройств на имс

- •7 Согласование уровней сигналов. Сопряжение кмоп и тлл схем.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами. (продолжение)

- •9 Элементы индикации

- •9 Элементы индикации (продолжение)

- •10 Риски в комбинационных схемах.

- •11. Дешифраторы, преобразователи кодов

- •12. Шифраторы

- •13. Мультиплексоры.

- •14. Демультиплексоры

- •Компараторы (схемы сравнения).

- •16.Синхронизация в цифровых устройствах.

- •17. Регистры.

- •18. Счетчики. Двоичные счетчики.

- •18. Счетчики. Двоичные счетчики. (продолжение)

- •19. Двоично-кодированные счетчики с произвольным модулем.

- •20. Счетчики с недвоичным кодированием.

- •20. Счетчики с недвоичным кодированием. (продолжение)

- •21. Полиномиальные счетчики.

- •2 1. Полиномиальные счётчики (продолжение)

- •22. Представление чисел с фиксированной запятой.

- •23. Представление чисел с плавающей запятой.

- •24. Погрешности представления чисел.

- •25. Кодирование двоичных чисел со знаком: прямой код

- •26. Кодирование двоичных чисел со знаком: дополнительный код.

- •27. Кодирование двоичных чисел со знаком: обратный код.

- •28. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в прямых кодах. Особенности выполнения операций над числами без знака.

- •29. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в дополнительных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах. (продолжение)

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28]

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28] (продолжение)

- •32.Умножение чисел с фиксированной запятой: общая схема целочисленного умножения. [подробнее с примерами – лекции, стр. 28-3 , но это след. Вопросы]

- •33. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом множимого.

- •34. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом суммы частичных произведений

- •35. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом множимого.

- •36. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом суммы частичных произведений.

- •Умножение двоичных чисел со знаком. Умножение чисел в дополнительном коде.

- •38. Логические методы ускорения умножения: алгоритм Бута.

- •39 Логические методы ускорения умножения: модифицированный алгоритм Бута, алгоритм Лемана

- •40. Логические методы ускорения умножения: умножение с обработкой двух разрядов множителя за шаг (умножение на два разряда одновременно)

- •41.Деление чисел с фиксированной запятой: общая схема целочисленного деления.

- •42. Методы деления двоичных чисел без знака: деление с восстановлением остатка.

- •43. Методы деления двоичных чисел без знака: деление без восстановления остатка.

- •44. Деление двоичных чисел со знаком. Деление чисел в дополнительном коде.

- •Сложение и вычитание двоичных чисел в форме с плавающей запятой.

- •46.Умножение чисел с плавающей запятой.

- •47. Деление чисел с плавающей запятой.

- •48.Выполнение операций сложение и вычитание в двоично-десятичном коде.

- •49.Сложение в двоично-десятичном коде чисел со знаком.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры. (продолжение)

- •51.Арифметико-логические устройства (алу).

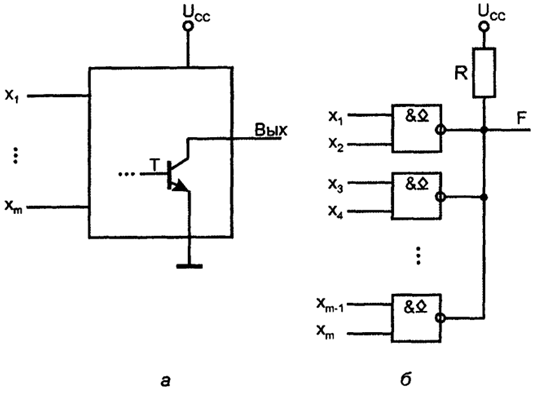

Типы выходных каскадов цифровых элементов: выход с открытым коллектором.

Э лементы

с открытым коллектором

имеют выходную цепь, заканчивающуюся

одиночным транзистором, коллектор

которого не соединен с какими-либо

цепями внутри микросхемы (рисунок 1а).

Транзистор управляется от предыдущей

части схемы элемента так, что может

находиться в насыщенном или запертом

состоянии. Насыщенное

состояние

трактуется как отображение логического

нуля, запертое

– единицы.

лементы

с открытым коллектором

имеют выходную цепь, заканчивающуюся

одиночным транзистором, коллектор

которого не соединен с какими-либо

цепями внутри микросхемы (рисунок 1а).

Транзистор управляется от предыдущей

части схемы элемента так, что может

находиться в насыщенном или запертом

состоянии. Насыщенное

состояние

трактуется как отображение логического

нуля, запертое

– единицы.

Насыщение транзистора обеспечивает на выходе напряжение U0 (малое напряжение насыщения «коллектор-эмиттер» UКЭН). Запирание транзистора какого-либо уровня напряжения на выходе эл-та не задает, выход при этом имеет фактически неизвестный «плавающий» потенциал, т.к. не подключен к каким-либо цепям схемы элемента. Поэтому для формирования высокого уровня напряжения при запирании транзистора на выходе элементов с открытым коллектором (типа ОК) требуется подключать внешние резисторы (или другие нагрузки), соединенные с источником питания.

Несколько выходов типа ОК можно соединять параллельно, подключая их к общей для всех выходов цепочке UCC – R (рисунок 1б).

При реализации

монтажной логики высокое напряжение

на общем выходе возникает только при

запирании всех транзисторов, т.к.

насыщение хотя бы одного из них снижает

выходное напряжение до уровня U0=UКЭН.

Т.е. для

получения логической единицы на

выходе требуется единичное состояние

всех выходов: выполняется монтажная

операция И. Поскольку каждый элемент

выполняет операцию Шеффера над своими

входными переменными, общий результат:

В

обозначения элементов с ОК после символа

функции ставится ромб с черточкой снизу.

В

обозначения элементов с ОК после символа

функции ставится ромб с черточкой снизу.

При использовании элементов с ОК в магистрально-модульных структурах требуется разрешать или запрещать работу того или иного элемента с помощью специального сигнала ОЕ, в качестве входа ОЕ может быть использован один из обычных входов элемента.

Достоинства: защищенность от повреждений из-за ошибок управления, приводящих к одновременной выдаче на шину нескольких слов, а также возможность реализации дополнительных операций монтажной логики. Недостаток: большая задержка переключения из 0 в 1. При этом переключении происходит заряд выходной емкости сравнительно малым током резистора R. Сопротивление резистора нельзя сделать слишком малым, т.к. это привело бы к большим токам выходной цепи в статике при насыщенном состоянии выходного транзистора. Поэтому положительный фронт выходного напряжения формируется относительно медленно с постоянной времени RC. До порогового напряжения (до середины полного перепада напряжения) экспоненциально изменяющийся сигнал изменится за время 0,7 RC, что и составляет задержку tЗ01.

При работе с элементами типа ОК проектировщик должен задать сопротивление резистора R, которое определяется для конкретных условий. Анализ статических режимов задает ограничения величины сопротивления снизу и сверху. Ограничение снизу величины сопротивления резистора связано с тем, что ее уменьшение может вызвать перегрузку насыщенного транзистора по току. Ограничение сверху величины сопротивления резистора связано с необходимостью гарантировать достаточно высокий уровень напряжения U1, формируемого в схеме при запертом состоянии всех выходов элементов с ОК. Имея границы диапазона значений сопротивления резистора проектировщик должен выбрать некоторое конкретное значение. Выбор вблизи нижней границы улучшает быстродействие схемы, а выбор вблизи верхней уменьшает потребляемую схемой мощность.