- •Самостоятельное изучение

- •Модели и система параметров логических элементов

- •2. Типы выходных каскадов цифровых элементов: логический выход.

- •3. Типы выходных каскадов цифровых элементов: выходы с тремя состояниями.

- •Типы выходных каскадов цифровых элементов: выход с открытым коллектором.

- •Паразитные связи цифровых элементов по цепям питания, фильтрация питающих напряжений в схемах цифровых устройств.

- •6 Типовые ситуации при построении цифровых устройств на имс

- •7 Согласование уровней сигналов. Сопряжение кмоп и тлл схем.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами. (продолжение)

- •9 Элементы индикации

- •9 Элементы индикации (продолжение)

- •10 Риски в комбинационных схемах.

- •11. Дешифраторы, преобразователи кодов

- •12. Шифраторы

- •13. Мультиплексоры.

- •14. Демультиплексоры

- •Компараторы (схемы сравнения).

- •16.Синхронизация в цифровых устройствах.

- •17. Регистры.

- •18. Счетчики. Двоичные счетчики.

- •18. Счетчики. Двоичные счетчики. (продолжение)

- •19. Двоично-кодированные счетчики с произвольным модулем.

- •20. Счетчики с недвоичным кодированием.

- •20. Счетчики с недвоичным кодированием. (продолжение)

- •21. Полиномиальные счетчики.

- •2 1. Полиномиальные счётчики (продолжение)

- •22. Представление чисел с фиксированной запятой.

- •23. Представление чисел с плавающей запятой.

- •24. Погрешности представления чисел.

- •25. Кодирование двоичных чисел со знаком: прямой код

- •26. Кодирование двоичных чисел со знаком: дополнительный код.

- •27. Кодирование двоичных чисел со знаком: обратный код.

- •28. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в прямых кодах. Особенности выполнения операций над числами без знака.

- •29. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в дополнительных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах. (продолжение)

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28]

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28] (продолжение)

- •32.Умножение чисел с фиксированной запятой: общая схема целочисленного умножения. [подробнее с примерами – лекции, стр. 28-3 , но это след. Вопросы]

- •33. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом множимого.

- •34. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом суммы частичных произведений

- •35. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом множимого.

- •36. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом суммы частичных произведений.

- •Умножение двоичных чисел со знаком. Умножение чисел в дополнительном коде.

- •38. Логические методы ускорения умножения: алгоритм Бута.

- •39 Логические методы ускорения умножения: модифицированный алгоритм Бута, алгоритм Лемана

- •40. Логические методы ускорения умножения: умножение с обработкой двух разрядов множителя за шаг (умножение на два разряда одновременно)

- •41.Деление чисел с фиксированной запятой: общая схема целочисленного деления.

- •42. Методы деления двоичных чисел без знака: деление с восстановлением остатка.

- •43. Методы деления двоичных чисел без знака: деление без восстановления остатка.

- •44. Деление двоичных чисел со знаком. Деление чисел в дополнительном коде.

- •Сложение и вычитание двоичных чисел в форме с плавающей запятой.

- •46.Умножение чисел с плавающей запятой.

- •47. Деление чисел с плавающей запятой.

- •48.Выполнение операций сложение и вычитание в двоично-десятичном коде.

- •49.Сложение в двоично-десятичном коде чисел со знаком.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры. (продолжение)

- •51.Арифметико-логические устройства (алу).

2 1. Полиномиальные счётчики (продолжение)

Рассмотрим схему счетчика при s = 3 (рис. 10.7):

В данном случае D-триггер и сумматор по модулю два в его обратной связи представляют собой T-триггер. Поэтому эту схему можно преобразовать следующим образом (рис. 10.8), и она может быть построена только на D- и T-триггерах, соединенных в кольцо (рис. 10.9).

З

десь

необходимо отметить, что для того, чтобы

каждый выходной разряд счетчика также

формировал последовательности

максимальной длины, необходимо, чтобы

число шагов s и период последовательности

M были взаимно простыми числами, т.е. (M,

s) = 1. Поскольку в данном примере это

условие не выполняется, диаграмма

последовательности состояний регистра

разбивается на несколько периодов

меньшей длины

десь

необходимо отметить, что для того, чтобы

каждый выходной разряд счетчика также

формировал последовательности

максимальной длины, необходимо, чтобы

число шагов s и период последовательности

M были взаимно простыми числами, т.е. (M,

s) = 1. Поскольку в данном примере это

условие не выполняется, диаграмма

последовательности состояний регистра

разбивается на несколько периодов

меньшей длины

Пусть s = 4. Матрица в этом случае имеет вид:

Э та

схема может быть построена только на

Т-триггерах и одном сумматоре по модулю

два (рис. 10.12):

та

схема может быть построена только на

Т-триггерах и одном сумматоре по модулю

два (рис. 10.12):

В общем случае схема полиномиального

счетчика на основе n-разрядного регистра

сдвига с линейными обратными связями

представлена на рис. 10.13:

общем случае схема полиномиального

счетчика на основе n-разрядного регистра

сдвига с линейными обратными связями

представлена на рис. 10.13:

с ли

коэффициент Ci =

1, то выход i-го триггера подается на вход

сумматора по модулю 2, если же Ci =

0, то – не подается. В соответствии с

коэффициентами многочлена однозначно

определяется структура обратной связи

регистра сдвига. Есть таблица всех

неприводимых многочленов, из которой

находят многочлены, представленные в

8-ричной форме.

ли

коэффициент Ci =

1, то выход i-го триггера подается на вход

сумматора по модулю 2, если же Ci =

0, то – не подается. В соответствии с

коэффициентами многочлена однозначно

определяется структура обратной связи

регистра сдвига. Есть таблица всех

неприводимых многочленов, из которой

находят многочлены, представленные в

8-ричной форме.

Например, характеристический многочлен = x4 x 1 в этой таблице будет иметь следующий вид:

![]() =

= ![]() .

.

В двоичном виде этом многочлен запишется как: 10 011, или в 8-ричном виде – 23. По такой записи многочлена однозначно строится схема полиномиального счетчика.

22. Представление чисел с фиксированной запятой.

!!!!Уважаемый читатель, знай, все указанные в тексте и на рисунках точки и запятые не случайны! Они нужны для правильного ответа!

В ЭВС числа и нечисловая информация представляются совокупностью двоичных разрядов. Совокупность двоичных разрядов, предназначенных для представления (записи) данных, называется разрядной сеткой.

В ЭВС применяют две формы представления чисел: с фиксированной запятой (точкой) и с плавающей запятой (точкой). Эти формы называют также соответственно естественной и нормальной.

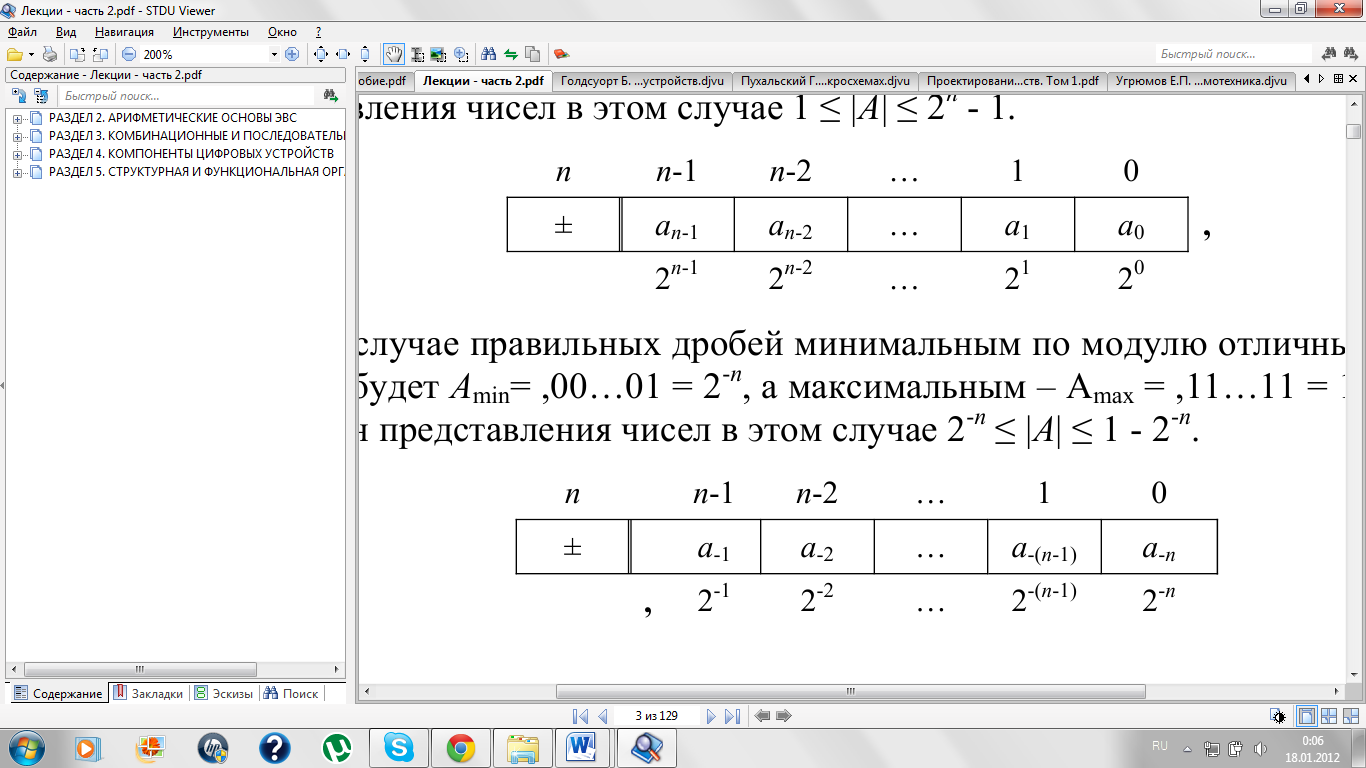

При естественной форме число записывается в естественном натуральном виде с выделением в общем случае следующих компонент числа: знака, запятой и цифр числа. Для сокращения длины разрядной сетки и упрощения обработки данных в конкретных ЭВС положение запятой фиксируется схемотехнически, т.е. аппаратными средствами. Такая форма представления числа называется формой с фиксированной запятой. Такое название связано с тем, что запятая, отделяющая дробную часть от целой, фиксируется в определенном месте относительно разрядов числа. При этом в слове данных сохраняются только два структурных компонента: один знаковый разряд и n разрядов для представления цифр числа. Для кода знака обычно выделяется крайний слева разряд. В знаковом разряде 1 соответствует минусу, а 0 – плюсу. Обычно положение запятой фиксируется либо после младшего (0 разряда), либо перед старшим, (n-1) разрядом. В первом случае числа представлены как целые, во втором – как правильные дроби. При этом запятая никак не обозначается, но в алгоритмах выполнения операций (умножение, деление) ее место учтено заранее одним из указанных способов.

В случае целых чисел минимальным по модулю отличным от нуля числом будет Аmin = 00…01, = 1, а максимальным, которому соответствуют единицы во всех n разрядах, – Amах = 11…11, = 2n - 1, т. е. диапазон представления чисел в этом случае 1 ≤ |A| ≤ 2n - 1.

В случае правильных дробей минимальным по модулю отличным от нуля числом будет Аmin= ,00…01 = 2-n, а максимальным – Аmax = ,11…11 = 1 - 2-n, т. е. диапазон представления чисел в этом случае 2-n ≤ |A| ≤ 1 - 2-n.

Достоинство фиксированной запятой: имеется возможность построить сравнительно несложные арифметические устройства с высоким быстродействием.