- •Самостоятельное изучение

- •Модели и система параметров логических элементов

- •2. Типы выходных каскадов цифровых элементов: логический выход.

- •3. Типы выходных каскадов цифровых элементов: выходы с тремя состояниями.

- •Типы выходных каскадов цифровых элементов: выход с открытым коллектором.

- •Паразитные связи цифровых элементов по цепям питания, фильтрация питающих напряжений в схемах цифровых устройств.

- •6 Типовые ситуации при построении цифровых устройств на имс

- •7 Согласование уровней сигналов. Сопряжение кмоп и тлл схем.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами. (продолжение)

- •9 Элементы индикации

- •9 Элементы индикации (продолжение)

- •10 Риски в комбинационных схемах.

- •11. Дешифраторы, преобразователи кодов

- •12. Шифраторы

- •13. Мультиплексоры.

- •14. Демультиплексоры

- •Компараторы (схемы сравнения).

- •16.Синхронизация в цифровых устройствах.

- •17. Регистры.

- •18. Счетчики. Двоичные счетчики.

- •18. Счетчики. Двоичные счетчики. (продолжение)

- •19. Двоично-кодированные счетчики с произвольным модулем.

- •20. Счетчики с недвоичным кодированием.

- •20. Счетчики с недвоичным кодированием. (продолжение)

- •21. Полиномиальные счетчики.

- •2 1. Полиномиальные счётчики (продолжение)

- •22. Представление чисел с фиксированной запятой.

- •23. Представление чисел с плавающей запятой.

- •24. Погрешности представления чисел.

- •25. Кодирование двоичных чисел со знаком: прямой код

- •26. Кодирование двоичных чисел со знаком: дополнительный код.

- •27. Кодирование двоичных чисел со знаком: обратный код.

- •28. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в прямых кодах. Особенности выполнения операций над числами без знака.

- •29. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в дополнительных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах. (продолжение)

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28]

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28] (продолжение)

- •32.Умножение чисел с фиксированной запятой: общая схема целочисленного умножения. [подробнее с примерами – лекции, стр. 28-3 , но это след. Вопросы]

- •33. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом множимого.

- •34. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом суммы частичных произведений

- •35. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом множимого.

- •36. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом суммы частичных произведений.

- •Умножение двоичных чисел со знаком. Умножение чисел в дополнительном коде.

- •38. Логические методы ускорения умножения: алгоритм Бута.

- •39 Логические методы ускорения умножения: модифицированный алгоритм Бута, алгоритм Лемана

- •40. Логические методы ускорения умножения: умножение с обработкой двух разрядов множителя за шаг (умножение на два разряда одновременно)

- •41.Деление чисел с фиксированной запятой: общая схема целочисленного деления.

- •42. Методы деления двоичных чисел без знака: деление с восстановлением остатка.

- •43. Методы деления двоичных чисел без знака: деление без восстановления остатка.

- •44. Деление двоичных чисел со знаком. Деление чисел в дополнительном коде.

- •Сложение и вычитание двоичных чисел в форме с плавающей запятой.

- •46.Умножение чисел с плавающей запятой.

- •47. Деление чисел с плавающей запятой.

- •48.Выполнение операций сложение и вычитание в двоично-десятичном коде.

- •49.Сложение в двоично-десятичном коде чисел со знаком.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры. (продолжение)

- •51.Арифметико-логические устройства (алу).

14. Демультиплексоры

Демультиплексоры выполняют операцию, обратную операции мультиплексоров (13 вопрос) — передают данные из одного входного канала в один из нескольких каналов-приемников. Многоразрядные демультиплексоры составляются из нескольких одноразрядных.

Нетрудно заметить, что дешифратор со входом разрешения работы будет работать в режиме демультиплексора, если на вход разрешения подавать информационный сигнал. Действительно, при единичном значении этого сигнала адресация дешифратора (подача адресного кода на его входы) приведет к возбуждению соответствующего выхода, при нулевом — нет. А это и соответствует передаче информационного сигнала в адресованный выходной канал.

В связи с указанным, в сериях элементов отдельные демультиплексоры могут отсутствовать, а дешифратор (11 вопрос) со входом разрешения часто называется дешифратором-демультиплексором.

Компараторы (схемы сравнения).

Компараторы (устройства сравнения) определяют отношения между двумя словами. Основными отношениями, через которые можно выразить остальные, можно считать два — "равно" и "больше".

Определим функции, вырабатываемые компараторами, следующим образом: они принимают единичное значение (истинны), если соблюдается условие, указанное в индексе обозначения функции. Например, функция FA = в = 1, если А = В и принимает нулевое значение при А ≠ В.

П![]() риняв

в качестве основных отношения "равно"

и "больше", для остальных можно

записать:

риняв

в качестве основных отношения "равно"

и "больше", для остальных можно

записать:

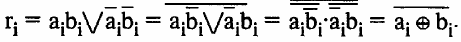

Устройства сравнения на равенство строятся на основе поразрядных операций над одноименными разрядами обоих слов. Слова равны, если равны все одноименные их разряды, т. е. если в обоих нули или единицы. Признак равенства разрядов:

Признак неравенства разрядов:

Признак равенства слов:

![]()

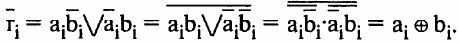

С хема

компаратора на равенство в базисе И-НЕ:

хема

компаратора на равенство в базисе И-НЕ:

16.Синхронизация в цифровых устройствах.

Основным методом построения работоспособных цифровых устройств в настоящее время является синхронизация, устраняющая критические временные состязания сигналов.

Синхронизация осуществляется тактовым генератором, сигналы которого распределяются по всем частям устройства и разрешают прием данных элементам памяти — синхронным триггерам. Она упорядочивает во времени последовательность операций при обработке информации в ЦУ. Темп обработки задается частотой тактовых сигналов.

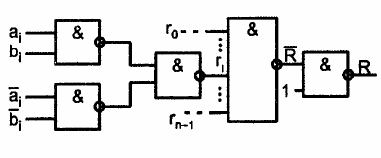

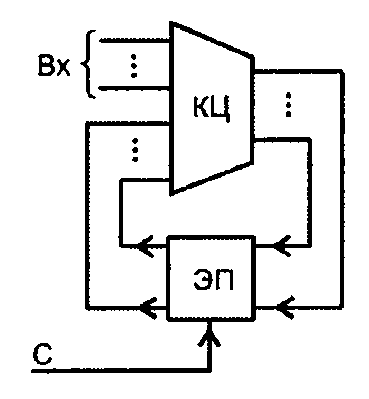

О

бобщенный

тракт обработки информации

при синхронной организации процессов

можно представить чередованием

комбинационных цепей КЦ и элементов

памяти ЭП, что отражает работу ЦУ как

при пространственном чередовании КЦ и

ЭП (рис. 3.29, а), так и при последовательном

выполнении различных

операций в разных временных тактах на

одном и том же оборудовании (рис. 3.29, б).

При работе устройства КЦ преобразуют

данные по тем или иным логическим

зависимостям, а ЭП принимают их после

окончания переходных процессов, т. е.

установления на выходах КЦ истинных

значений сигналов.

бобщенный

тракт обработки информации

при синхронной организации процессов

можно представить чередованием

комбинационных цепей КЦ и элементов

памяти ЭП, что отражает работу ЦУ как

при пространственном чередовании КЦ и

ЭП (рис. 3.29, а), так и при последовательном

выполнении различных

операций в разных временных тактах на

одном и том же оборудовании (рис. 3.29, б).

При работе устройства КЦ преобразуют

данные по тем или иным логическим

зависимостям, а ЭП принимают их после

окончания переходных процессов, т. е.

установления на выходах КЦ истинных

значений сигналов.

Рис. 3.29. Обобщенные структуры тракта обработки информации в цифр. устройствах (а, б)

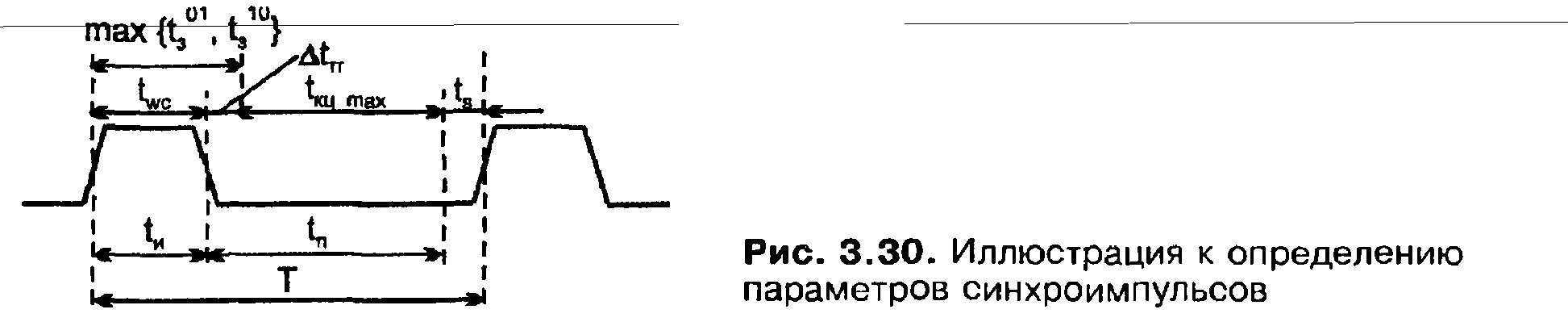

Параметры тактовых импульсов

П ериод

тактовых импульсов (синхроимпульсов)

складывается из длительностей

импульса и паузы. Длительность импульса

должна быть достаточной для

надежной записи информации в триггер,

этот параметр задается в пас- портных

данных триггера.

ериод

тактовых импульсов (синхроимпульсов)

складывается из длительностей

импульса и паузы. Длительность импульса

должна быть достаточной для

надежной записи информации в триггер,

этот параметр задается в пас- портных

данных триггера.

П риняв

новое состояние, триггеры тем самым

формируют на входах КЦ но

риняв

новое состояние, триггеры тем самым

формируют на входах КЦ новые

значения сигналов.

Для многих схем, особенно для БИС/СБИС,

большую роль играют задержки сигналов

в линиях связи, которые следует оценивать

с учетом топологии межсоединений.

Определенные требования предъявляются

и к крутизне фронтов синхроимпульсов.

Она не должна снижаться ниже допустимого

предела.

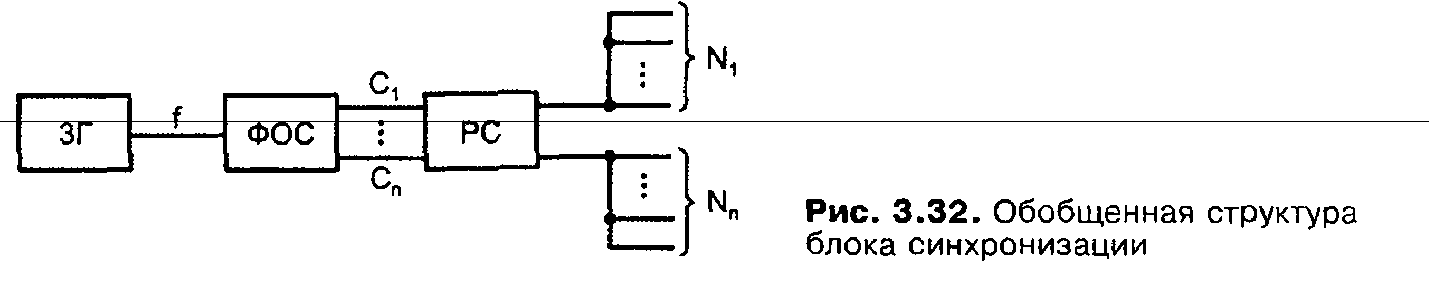

Структура устройств синхронизации

Обобщенная структура устройства синхронизации (рис. 3.32) содержит следующие блоки: задающий генератор ЗГ, формирователь опорных сигналов ФОС и размножитель сигналов PC. Блок ФОС служит для выработки необходимого числа импульсных последовательностей заданной формы в зависимости от фазности системы синхронизации и временных параметров синхросигналов этих последовательностей. Фазность — важный признак системы синхронизации, определяемый числом синхроимпульсов в одном периоде синхронизации (иначе говоря, числом импульсных последовательностей, используемых для синхронизации устройства). Фазность зависит от типа триггеров, применяемых в устройстве, способа обмена между функциональными узлами, требований к быстродействию и аппаратурной сложности устройства.

Различают следующие системы синхронизации: однофазную; двухфазную; многофазную