- •Самостоятельное изучение

- •Модели и система параметров логических элементов

- •2. Типы выходных каскадов цифровых элементов: логический выход.

- •3. Типы выходных каскадов цифровых элементов: выходы с тремя состояниями.

- •Типы выходных каскадов цифровых элементов: выход с открытым коллектором.

- •Паразитные связи цифровых элементов по цепям питания, фильтрация питающих напряжений в схемах цифровых устройств.

- •6 Типовые ситуации при построении цифровых устройств на имс

- •7 Согласование уровней сигналов. Сопряжение кмоп и тлл схем.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами.

- •8 Схемы низковольтной кмоп-логики и их сопряжение с другими схемами. (продолжение)

- •9 Элементы индикации

- •9 Элементы индикации (продолжение)

- •10 Риски в комбинационных схемах.

- •11. Дешифраторы, преобразователи кодов

- •12. Шифраторы

- •13. Мультиплексоры.

- •14. Демультиплексоры

- •Компараторы (схемы сравнения).

- •16.Синхронизация в цифровых устройствах.

- •17. Регистры.

- •18. Счетчики. Двоичные счетчики.

- •18. Счетчики. Двоичные счетчики. (продолжение)

- •19. Двоично-кодированные счетчики с произвольным модулем.

- •20. Счетчики с недвоичным кодированием.

- •20. Счетчики с недвоичным кодированием. (продолжение)

- •21. Полиномиальные счетчики.

- •2 1. Полиномиальные счётчики (продолжение)

- •22. Представление чисел с фиксированной запятой.

- •23. Представление чисел с плавающей запятой.

- •24. Погрешности представления чисел.

- •25. Кодирование двоичных чисел со знаком: прямой код

- •26. Кодирование двоичных чисел со знаком: дополнительный код.

- •27. Кодирование двоичных чисел со знаком: обратный код.

- •28. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в прямых кодах. Особенности выполнения операций над числами без знака.

- •29. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в дополнительных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах.

- •30. Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах. (продолжение)

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28]

- •31. Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды. [лекции, стр.26-28] (продолжение)

- •32.Умножение чисел с фиксированной запятой: общая схема целочисленного умножения. [подробнее с примерами – лекции, стр. 28-3 , но это след. Вопросы]

- •33. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом множимого.

- •34. Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом суммы частичных произведений

- •35. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом множимого.

- •36. Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом суммы частичных произведений.

- •Умножение двоичных чисел со знаком. Умножение чисел в дополнительном коде.

- •38. Логические методы ускорения умножения: алгоритм Бута.

- •39 Логические методы ускорения умножения: модифицированный алгоритм Бута, алгоритм Лемана

- •40. Логические методы ускорения умножения: умножение с обработкой двух разрядов множителя за шаг (умножение на два разряда одновременно)

- •41.Деление чисел с фиксированной запятой: общая схема целочисленного деления.

- •42. Методы деления двоичных чисел без знака: деление с восстановлением остатка.

- •43. Методы деления двоичных чисел без знака: деление без восстановления остатка.

- •44. Деление двоичных чисел со знаком. Деление чисел в дополнительном коде.

- •Сложение и вычитание двоичных чисел в форме с плавающей запятой.

- •46.Умножение чисел с плавающей запятой.

- •47. Деление чисел с плавающей запятой.

- •48.Выполнение операций сложение и вычитание в двоично-десятичном коде.

- •49.Сложение в двоично-десятичном коде чисел со знаком.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры.

- •50.Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры. (продолжение)

- •51.Арифметико-логические устройства (алу).

Модели и система параметров логических элементов.

Типы выходных каскадов цифровых элементов: логический выход.

Типы выходных каскадов цифровых элементов: выходы с тремя состояниями.

Типы выходных каскадов цифровых элементов: выход с открытым коллектором.

Паразитные связи цифровых элементов по цепям питания, фильтрация питающих напряжений в схемах цифровых устройств.

Типовые ситуации при построении цифровых устройств на интегральных микросхемах.

Согласование уровней сигналов. Сопряжение КМОП- и TTJI-схем.

Схемы низковольтовой КМОП-логики и их сопряжение с другими схемами.

Элементы индикации.

Риски в комбинационных схемах.

Дешифраторы, преобразователи кодов.

Шифраторы.

Мультиплексоры.

Демультиплексоры.

Компараторы (схемы сравнения).

Синхронизация в цифровых устройствах.

Регистры.

Счетчики. Двоичные счетчики.

Двоично-кодированные счетчики с произвольным модулем.

Счетчики с недвоичным кодированием.

Полиномиальные счетчики.

Представление чисел с фиксированной запятой.

Представление чисел с плавающей запятой.

Погрешности представления чисел.

Кодирование двоичных чисел со знаком: прямой код.

Кодирование двоичных чисел со знаком: дополнительный код.

Кодирование двоичных чисел со знаком: обратный код.

Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в прямых кодах. Особенности выполнения операций над числами без знака.

Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в дополнительных кодах.

Сложение и вычитание двоичных чисел в форме с фиксированной запятой со знаком в обратных кодах.

Переполнение при сложении чисел с фиксированной запятой. Модифицированные коды.

Умножение чисел с фиксированной запятой: общая схема целочисленного умножения.

Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом множимого.

Методы умножения двоичных чисел без знака: умножение с младших разрядов множителя со сдвигом суммы частичных произведений.

Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом множимого.

Методы умножения двоичных чисел без знака: умножение со старших разрядов множителя со сдвигом суммы частичных произведений.

Умножение двоичных чисел со знаком. Умножение чисел в дополнительном коде.

Логические методы ускорения умножения: алгоритм Бута.

Логические методы ускорения умножения: модифицированный алгоритм Бута, алгоритм Лемана.

Логические методы ускорения умножения: умножение с обработкой двух разрядов множителя за шаг (умножение на два разряда одновременно).

Деление чисел с фиксированной запятой: общая схема целочисленного деления.

Методы деления двоичных чисел без знака: деление с восстановлением остатка.

Методы деления двоичных чисел без знака: деление без восстановления остатка.

Деление двоичных чисел со знаком. Деление чисел в дополнительном коде.

Сложение и вычитание двоичных чисел в форме с плавающей запятой.

Умножение чисел с плавающей запятой.

Деление чисел с плавающей запятой.

Выполнение операций сложение и вычитание в двоично-десятичном коде.

Сложение в двоично-десятичном коде чисел со знаком.

Сумматоры. Одноразрядный сумматор. Многоразрядные сумматоры.

Арифметико-логические устройства (АЛУ).

Самостоятельное изучение

Двоичные умножители. Последовательные умножители. Матричные умножители. Древовидные умножители.

Основные параметры и классификация запоминающих устройств (ЗУ). Постоянные запоминающие устройства (ПЗУ). Масочные ПЗУ. Программируемые ПЗУ. Непрограммируемые ПЗУ. Флэш-память. Оперативные запоминающие устройства (ОЗУ). Статические ОЗУ. Динамические ОЗУ.

Программируемые логические интегральные схемы (ПЛИС). Базовые матричные кристаллы (вентильные матрицы с масочным программированием). Программируемые пользователем вентильные матрицы (FPGA). Сложные программируемые логические схемы (CPLD).

Модели и система параметров логических элементов

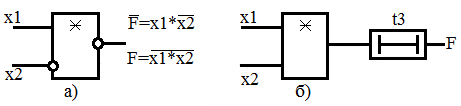

Даже самые сложные преобр-я цифр. инф-ции сводятся к простейшим операциям над логич. переменными 0 и 1. Они реализ-ся логич-ми эл-ми в соотв-ии с формулами алгебры логики. В идеализированных схемах логич-е эл-ты мб представлены усл-ми графич-ми обознач-ми (а).

В реальных усл-ях логич. переменные 0 и 1

отображ-ся 2мя уровнями напр-я: U0

и U1.

В положительной

логике

U1

> U0,

в отрицательной

U1

< U0.

Переход от операции в «+» логике к

операции в «-» производится инвертированием

всех переменных. По умолчанию исп-ся

«+» логика. Мб использованы обознач-я

высокого и низкого уровней напр-я как

Н

(High) и L (Low).

реальных усл-ях логич. переменные 0 и 1

отображ-ся 2мя уровнями напр-я: U0

и U1.

В положительной

логике

U1

> U0,

в отрицательной

U1

< U0.

Переход от операции в «+» логике к

операции в «-» производится инвертированием

всех переменных. По умолчанию исп-ся

«+» логика. Мб использованы обознач-я

высокого и низкого уровней напр-я как

Н

(High) и L (Low).

Преобр-я логических переменных можно задать в различных формах: с помощью операций И, ИЛИ, НЕ (булевский базис), операции И-НЕ (базис Шеффера), опер. ИЛИ-НЕ (базис Пирса) и др. Чаще всего встреч. базисы Шеффера и Пирса.

Реальные переходные процессы в логических эл-ах сложны, и в моделях они отображаются с помощью упрощений. В простейшей модели динамические св-ва эл-та отражаются введением в его выходную цепь эл-та задержки сигнала на время tз (рис. б).

Статические параметры логических элементов.

4ре знач-я напряжений задают границы отображения переменных (0 и 1) на выходе и входе элемента. Требуется, чтобы напр-е, отображающее логич. 1, было высоким, а напр-е, отображающее 0, – низким. Эти требования задаются параметрами Uвх.1.min и Uвх.0.max. Уровни, гарантируемые на выходе элемента при соблюдении допустимых нагрузочных условий, задаются параметрами Uвых.1.min и Uвых.0.max. Выходные уровни несколько лучше входных, что обеспечивает определенную помехоустойчивость элемента. Для уровня U1 опасны отрицательные помехи, снижающие его, причем допустимая статич. помеха равна: U–пом = Uвых.1.min - Uвх.1.min. Для уровня U0 опасны положит. помехи, причем допустимая статич. помеха равна: U+пом = Uвых.0.max - Uвх.0.max.

4 ре

знач-я токов

– вх. и вых. токи в обоих логических

состояниях. При

высоком уровне вых. напр-я

из элемента-источника ток вытекает,

цепи нагрузки ток поглощают. При

низком: ток

нагрузки втекает в элемент-источник, а

из входных цепей элементов-приемников

токи вытекают.

ре

знач-я токов

– вх. и вых. токи в обоих логических

состояниях. При

высоком уровне вых. напр-я

из элемента-источника ток вытекает,

цепи нагрузки ток поглощают. При

низком: ток

нагрузки втекает в элемент-источник, а

из входных цепей элементов-приемников

токи вытекают.

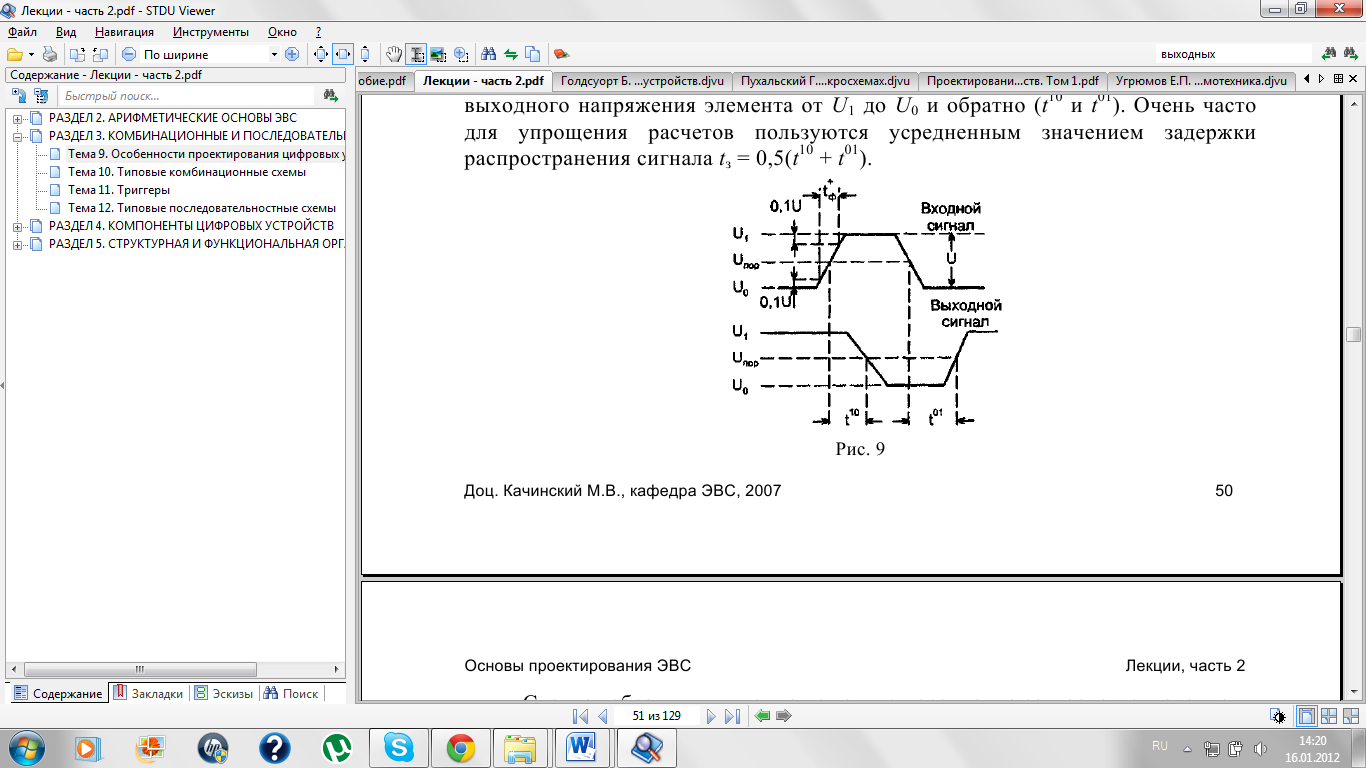

Быстродействие логич. эл-ов опред-ся скоростями их перехода из одного сост-я в другое. Временные диаграммы переключения инвертирующего логического элемента (рис.) показывают длительности характерных этапов переходных процессов, отсчитываемые по измерительным уровням. Моментом изменения логического сигнала считают момент достижения им порогового уровня. Часто за пороговый уровень принимают середину логического перепада сигнала, т.е. 0,5(U0 + U1). Иногда пороговый уровень указывается более точно в паспортных данных элемента. На временных диаграммах показаны задержки распространения сигнала при изменении выходного напряжения элемента от U1 до U0 и обратно (t10 и t01). Очень часто для упрощения расчетов пользуются усредненным значением задержки распространения сигнала tз = 0,5(t10 + t01). На быстродействие ЦУ влияют также емкости, на перезаряд которых требуются затраты времени. В справочных данных приводятся входные и выходные емкости логических элементов, знание которых позволяет подсчитать емкости нагрузки в узлах схемы. Для подключаемой к выходу элемента емкости приводятся две цифры: номинальная емкость CL и предельно допустимая емкость Cmax. Первая емкость соответствует условиям измерения задержек сигналов. Значения реальных задержек можно оценить с помощью соотн.: tз = tз н + k∆C, где tз н – номин. значение задержки; ∆C = С - CL; С – фактич. знач. нагрузочной емкости; k – к-т, кот. задается для каждой серии эл-ов индивидуально.

Предельно допустимая емкость указывает границу, которую нельзя нарушать, поскольку при этом работоспособность элемента не гарантируется.

Мощности потребления логических элементов. Статическая мощность потребляется элементом, который не переключается. При переключении потребляется дополнительно динамическая мощность, которая пропорциональна частоте переключения элемента. Таким образом, полная мощность зависит от частоты переключения элемента, что и следует учитывать при ее подсчете.