- •5. Простейшая схема защиты от дребезга

- •6. Шинный фиксатор уровня

- •7. Биполярные последовательностные плу

- •8. Последовательностные устройства типа gal

- •8_8. Последовательные устройства типа gal

- •13. Итерационные и последовательностные схемы

- •14. Методология синхронного проектирования

- •15. Структура синхронной системы

- •16. Разброс задержек тактового сигнала

- •17. Стробирование тактового сигнала

- •18. Асинхронные входы

- •19. Сбой в работе синхронизирующего устройства и метастабильность

- •20. Сбой в работе синхронизирующего устройства

- •21.Время выхода из метастабильности

- •22.Разработка надежного синхронизирующего устройства

- •23.Анализ времени пребывания в состоянии метастабильности

- •24. Более совершенные синхронизирующие устройства

- •25. Другие схемы синхронизирующих устройств

- •26. Триггеры с защитой от метастабильности

- •27. Синхронизация при высокоскоростной передаче данных

- •28.Интегральные схемы типа cpld

- •29. Семейство ис xc9500 фирмы Xilinx

- •30. Архитектура функционального блока

- •31. Архитектура блока ввода/вывода

- •32. Переключающая матрица

- •33. Интегральные схемы типа fpga

- •34. Семейство ис типа fpga хс4000 фирмы Xilinx

- •35. Перестраиваемый логический блок

- •36. Блок ввода/вывода

- •37. Программируемые соединения

- •38. Средства автоматизированного проектирования

- •39. Языки описания схем

- •40 Ввод схемы

- •41 Временные диаграммы и временные параметры

- •42. Анализ схемы и моделирование

- •43. Разработка печатной платы

- •44. Проектирование, предусматривающее тестируемость

- •45. Тестирование

- •46. Тестер с игольчатыми контактами и внутрисхемное тестирование

- •47. Методы сканирования

- •48. Оценка надежности цифровой системы

- •49. Основы теории длинных линий

- •50. Передача логических сигналов по длинным линиям

- •51. Согласованные нагрузки на концах линий передачи логических сигналов

- •5. Простейшая схема защиты от дребезга

15. Структура синхронной системы

Если число триггеров в последовательностной схеме велико, то неудобно (а часто невозможно) рассматривать схему как одно целое, поскольку число состояний такого конечного автомата слишком велико.

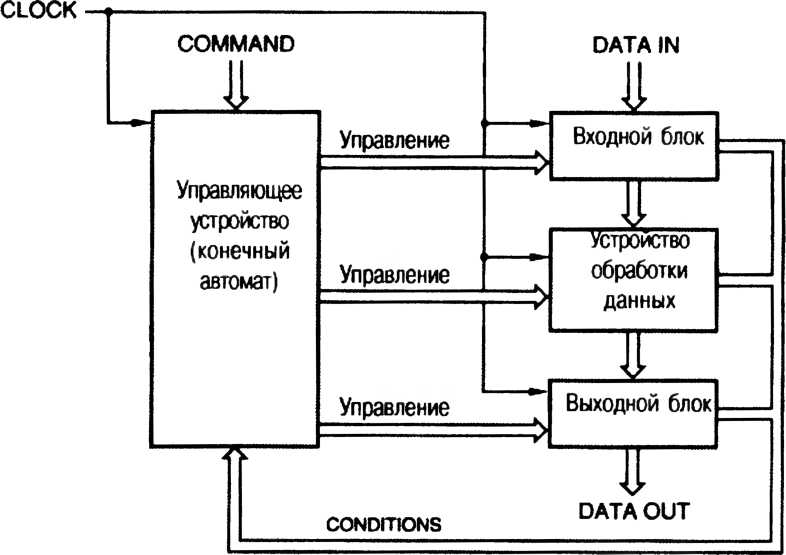

В большинстве случаев цифровые системы или подсистемы можно разбить на две или большее число частей. Независимо от того, что именно обрабатывается в цифровой системе, - числа, оцифрованный речевой сигнал, - можно считать, что в определенной части цифровой системы происходит запоминание, перенаправление, объединение или преобразование «данных» в самом общем виде; эту часть мы будем называть устройством обработки данных.

Что касается другой части - управляющее устройство, то она производит запуск или остановку устройства обработки данных, проверяет правильность его функционирования и, в зависимости от обстоятельств, решает, что надо делать дальше. Как правило, только управляющее устройство необходимо разрабатывать как конечный автомат.

Рис. 8.79. Структура синхронной системы

На рис. 8.79 представлена блок-схема системы, где, помимо управляющего устройства и устройства обработки данных, явным образом включены входной и выходной блоки.

Управляющее устройство представляет собой конечный автомат с командными входами и входами условий; сигналами на командных входах определяется функция, которую должен выполнить автомат, а сигналы на входах условий вырабатываются устройством обработки данных. На командные входы сигналы поступают от другой подсистемы или от пользователя, и ими устанавливается режим работы управляющего конечного автомата. Сигналы на входах условий позволяют управляющему устройству изменить свое поведение, как того требуют обстоятельства, по результатам работы устройства обработки данных.

Ключевым моментом в структуре является то, что во всех блоках используется один и тот же общий тактовый сигнал.

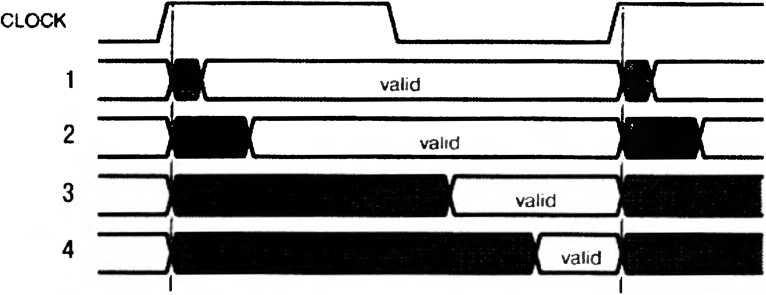

Рис. 8.80 служит иллюстрацией того, что происходит в управляющем устройстве и в устройстве обработки данных в пределах одного периода тактового сигнала:

Спустя небольшое время после начала очередного периода устанавливается состояние управляющего устройства и принимают установившиеся значения регистровые выходные сигналы устройства обработки данных.

Затем, спустя время, определяемое задержкой комбинационной логики, устанавливаются значения сигналов на выходах типа Мура управляющего конечного автомата. Для устройства обработки данных эти сигналы являются управляющими входными сигналами. Именно ими определяется, какие функции выполняет устройство обработки данных на остающейся части периода тактового сигнала.

Ближе к концу периода тактового сигнала в устройстве обработки данных вырабатываются и становятся доступными управляющему устройству выходные сигналы условий типа обнаружения нуля или переполнения.

В конце периода тактового сигнала, к моменту времени, который непосредственно предшествует началу интервала, задаваемого временем установления, логикой переходов в управляющем конечном автомате определяется следующее состояние; оно зависит от текущего состояния, а также от сигналов на командных входах и входах условий. Примерно к этому же времени результаты вычислений в устройстве обработки данных оказываются готовыми к тому, чтобы быть загруженными в регистры этого устройства.

С приходом фронта тактового сигнала описанный цикл может повторяться.

Сигналы на управляющих входах устройства обработки данных, являющиеся выходными сигналами управляющего конечного автомата, могут быть сигналами типа Мура, Мили или сигналами на конвейерном выходе Мили; приведенные на рис. 8.80 временные диаграммы относятся к случаю выходов типа Мура.

Сигналы на выходах типа Мура или на конвейерных выходах типа Мили управляют работой устройства обработки данных в строгом соответствии с текущим состоянием и последними значениями входных сигналов, но это воздействие не зависит от сигналов условий, вырабатываемых устройством обработки данных в этом периоде тактового сигнала. Это повышает гибкость системы, но одновременно требует большего времени для правильной работы, поскольку много большими становятся задержки распространения сигнала, что приводит, как минимум, к увеличению требуемого периода тактового сигнала.

Рис.

8.80. События,

происходящие в синхронной системе в

пределах одного периодатактового

сигнала