- •5. Простейшая схема защиты от дребезга

- •6. Шинный фиксатор уровня

- •7. Биполярные последовательностные плу

- •8. Последовательностные устройства типа gal

- •8_8. Последовательные устройства типа gal

- •13. Итерационные и последовательностные схемы

- •14. Методология синхронного проектирования

- •15. Структура синхронной системы

- •16. Разброс задержек тактового сигнала

- •17. Стробирование тактового сигнала

- •18. Асинхронные входы

- •19. Сбой в работе синхронизирующего устройства и метастабильность

- •20. Сбой в работе синхронизирующего устройства

- •21.Время выхода из метастабильности

- •22.Разработка надежного синхронизирующего устройства

- •23.Анализ времени пребывания в состоянии метастабильности

- •24. Более совершенные синхронизирующие устройства

- •25. Другие схемы синхронизирующих устройств

- •26. Триггеры с защитой от метастабильности

- •27. Синхронизация при высокоскоростной передаче данных

- •28.Интегральные схемы типа cpld

- •29. Семейство ис xc9500 фирмы Xilinx

- •30. Архитектура функционального блока

- •31. Архитектура блока ввода/вывода

- •32. Переключающая матрица

- •33. Интегральные схемы типа fpga

- •34. Семейство ис типа fpga хс4000 фирмы Xilinx

- •35. Перестраиваемый логический блок

- •36. Блок ввода/вывода

- •37. Программируемые соединения

- •38. Средства автоматизированного проектирования

- •39. Языки описания схем

- •40 Ввод схемы

- •41 Временные диаграммы и временные параметры

- •42. Анализ схемы и моделирование

- •43. Разработка печатной платы

- •44. Проектирование, предусматривающее тестируемость

- •45. Тестирование

- •46. Тестер с игольчатыми контактами и внутрисхемное тестирование

- •47. Методы сканирования

- •48. Оценка надежности цифровой системы

- •49. Основы теории длинных линий

- •50. Передача логических сигналов по длинным линиям

- •51. Согласованные нагрузки на концах линий передачи логических сигналов

- •5. Простейшая схема защиты от дребезга

13. Итерационные и последовательностные схемы

Функцию итерационной схемы, состоящей из п модулей, может выполнить последовательностная схема, в которой модуль имеется лишь в одном экземпляре, но ей требуется совершить п шагов (за п тактов), чтобы получить нужный результат. Это блестящий пример пространственно-временного обмена при цифровом проектировании.

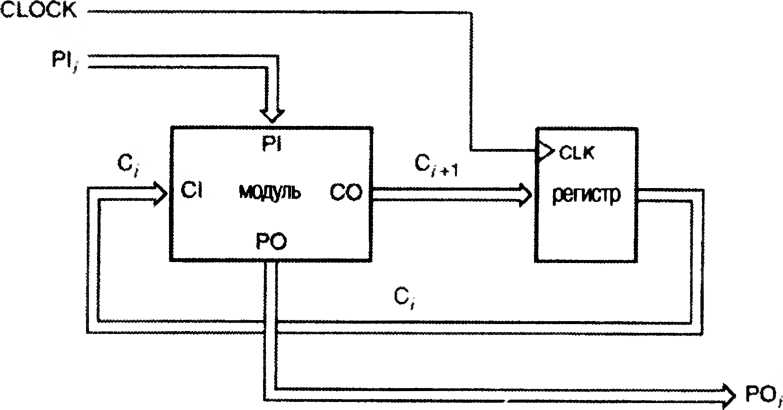

Как видно из рис. 8.74, в последовательностной схеме для сохранения значений сигналов в межкаскадном соединении в конце каждого шага используются триггеры; именно их выходные сигналы служат входными сигналами межкаскадного соединения в начале следующего шага. Перед началом первого такта триггеры необходимо загрузить граничными значениями входных сигналов; по окончании n-го такта они содержат граничные значения выходных сигналов.

Рис. 8.74. Общая структура последовательностной схемы, эквивалентной итерационной схеме

Поскольку итерационная схема является комбинационной, все ее первичные и граничные входные сигналы можно подать одновременно, а все ее первичные и граничные выходные сигналы доступны спустя время, равное комбинационной задержке.

В последовательностной схеме первичные входные сигналы должны поступать последовательно, по одному комплекту на каждом такте, и первичные выходные сигналы должны вырабатываться в соответствующие моменты времени. Поэтому входные сигналы часто формируют с помощью регистров сдвига с последовательным выводом, а выходные сигналы собирают в регистрах сдвига с последовательным вводом.

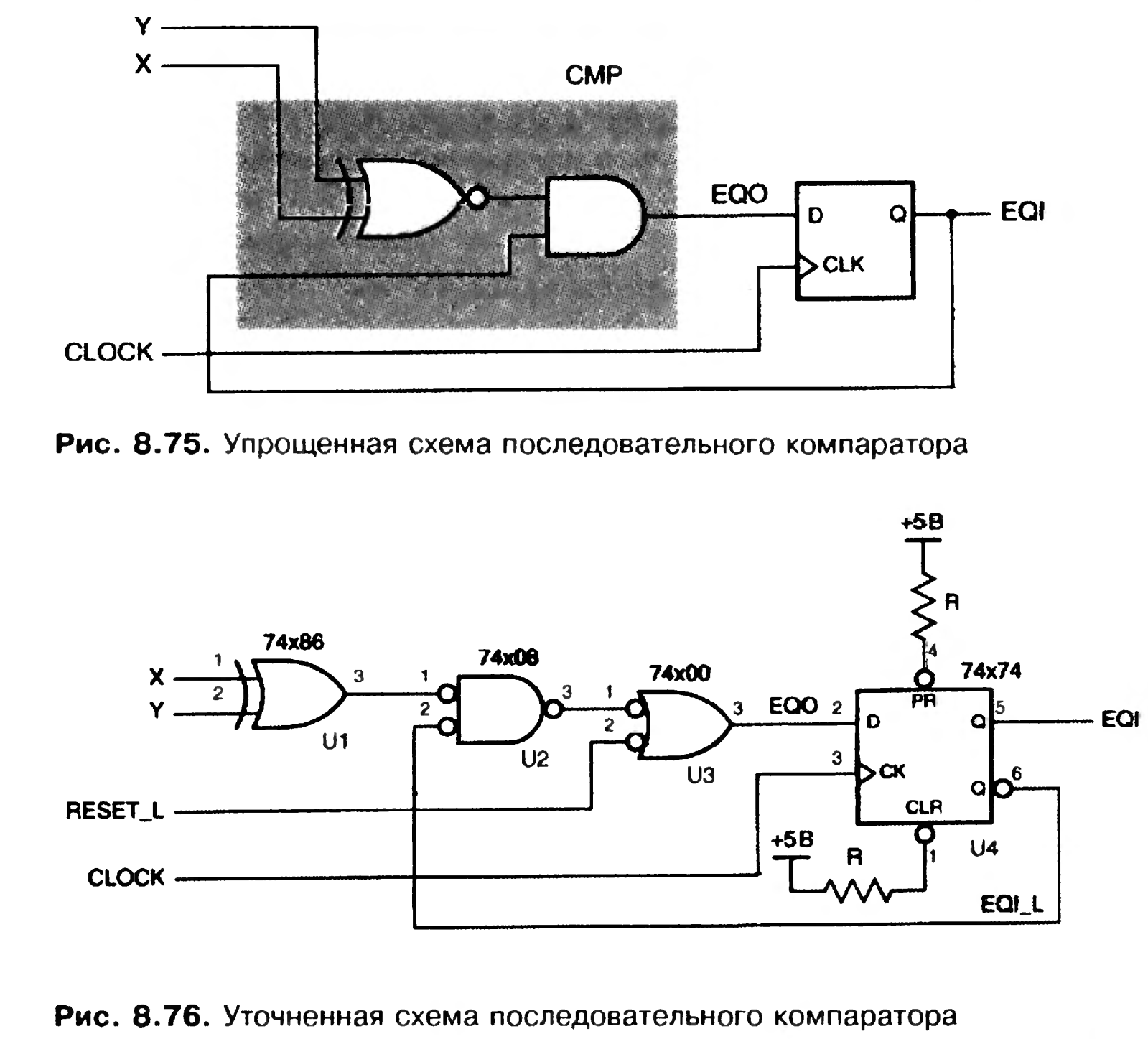

На рис. 8.75 в качестве примера приведена основная схема последовательного компаратора. Более подробная схема показана на рис. 8.76. В схеме предусмотрен синхронный сброс: при подаче сигнала на этот вход междукаскадный триггер на следующем такте устанавливается в начальное единичное состояние. Это начальное значение соответствует граничному входному сигналу итерационного компаратора.

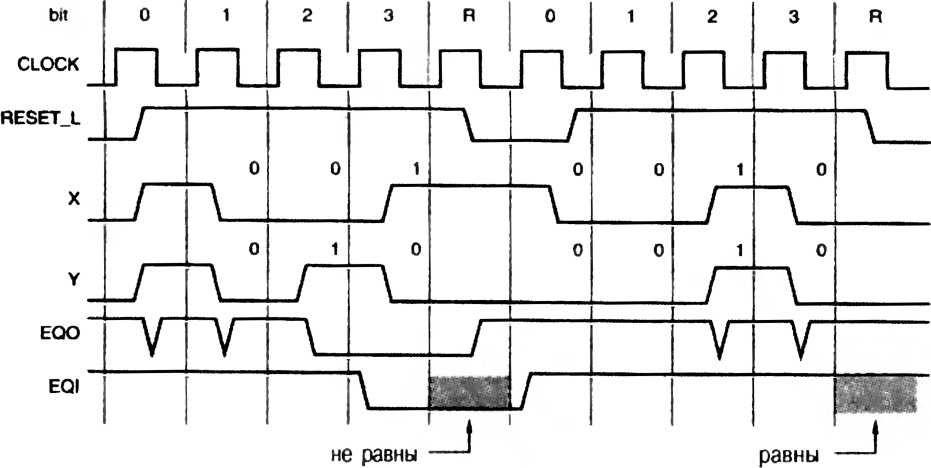

С помощью последовательного компаратора n-разрядное сравнение осуществляется за п + 1 тактов. Сигнал RESET_L действует на первом такте, а на следующих п тактах этот сигнал имеет неактивный уровень, и на входы X и Y подаются биты данных. На выходе EQI вырабатывается результат сравнения, удерживаемый в течение периода, следующего за очередным перепадом в тактовом сигнале. На рис. 8.77 приведены временные диаграммы для последовательного сравнения в 4-х разрядах. Паразитные импульсы в сигнале EQO возникают в те моменты времени, когда изменяются сигналы на выходах комбинационных схем в качестве отклика на поступление новых значений сигналов на входы X и Y.

Рис. 8.77. Временные диаграммы для последовательного компаратора

14. Методология синхронного проектирования

В синхронной системе все триггеры переключаются по одному и тому же общему сигналу, а входы установки в единичное состояние и сброса не используются за исключением начальной инициализации системы. При состыковке цифровых систем или подсистем с различными тактовыми сигналами обычно бывает достаточно указать ограниченное число асинхронных сигналов, требующих специальной обработки.

В синхронных системах гонки и источники опасности не страшны по двум причинам. Во-первых, схемами классического образца, в которых могли бы иметь место гонки и существенные источники опасности, являются только заранее отлаженные элементы, например, триггеры в дискретном исполнении или ячейки специализированной ИС, а в отношении таких элементов производитель гарантирует, что они будут работать хорошо. Во-вторых, статические, динамические и функциональные источники опасности, которыми могут обладать комбинационные схемы на управляющих входах триггеров, не оказывают никакого влияния на работу системы, так как существенны значения сигналов на управляющих входах только в такие моменты времени, когда паразитные импульсы уже не имеют возможности оказать какое-либо воздействие.

Помимо проработки функционального поведения конечного автомата, разработчику практической синхронной системы или подсистемы необходимо решить следующие три четко очерченные задачи, без чего нельзя гарантировать надежную работу системы:

Найти и минимизировать разброс задержек тактового сиг нала при его прохождении по разным путям.

Обеспечить наличие у триггеров положительного запаса по времени установления и по времени удержания с учетом возможного разброса задержек тактового сигнала.

Синхронизировать воздействие асинхронных входных сигналов с тактовым сигналом, позаботившись о том, чтобы вероятность отказа у схем синхронизации была достаточно малой.