- •5. Простейшая схема защиты от дребезга

- •6. Шинный фиксатор уровня

- •7. Биполярные последовательностные плу

- •8. Последовательностные устройства типа gal

- •8_8. Последовательные устройства типа gal

- •13. Итерационные и последовательностные схемы

- •14. Методология синхронного проектирования

- •15. Структура синхронной системы

- •16. Разброс задержек тактового сигнала

- •17. Стробирование тактового сигнала

- •18. Асинхронные входы

- •19. Сбой в работе синхронизирующего устройства и метастабильность

- •20. Сбой в работе синхронизирующего устройства

- •21.Время выхода из метастабильности

- •22.Разработка надежного синхронизирующего устройства

- •23.Анализ времени пребывания в состоянии метастабильности

- •24. Более совершенные синхронизирующие устройства

- •25. Другие схемы синхронизирующих устройств

- •26. Триггеры с защитой от метастабильности

- •27. Синхронизация при высокоскоростной передаче данных

- •28.Интегральные схемы типа cpld

- •29. Семейство ис xc9500 фирмы Xilinx

- •30. Архитектура функционального блока

- •31. Архитектура блока ввода/вывода

- •32. Переключающая матрица

- •33. Интегральные схемы типа fpga

- •34. Семейство ис типа fpga хс4000 фирмы Xilinx

- •35. Перестраиваемый логический блок

- •36. Блок ввода/вывода

- •37. Программируемые соединения

- •38. Средства автоматизированного проектирования

- •39. Языки описания схем

- •40 Ввод схемы

- •41 Временные диаграммы и временные параметры

- •42. Анализ схемы и моделирование

- •43. Разработка печатной платы

- •44. Проектирование, предусматривающее тестируемость

- •45. Тестирование

- •46. Тестер с игольчатыми контактами и внутрисхемное тестирование

- •47. Методы сканирования

- •48. Оценка надежности цифровой системы

- •49. Основы теории длинных линий

- •50. Передача логических сигналов по длинным линиям

- •51. Согласованные нагрузки на концах линий передачи логических сигналов

- •5. Простейшая схема защиты от дребезга

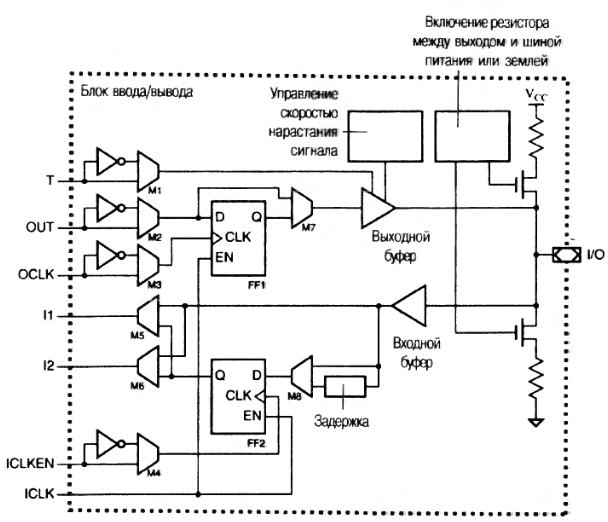

36. Блок ввода/вывода

Структура блока ввода/вывода в ИС семейства ХС4000 показана на рис. I/O-вывод можно использовать в качестве входа или выхода, либо в качестве того и другого.

На пути входного и выходного сигналов имеются переключающиеся по фронту D-триггеры, возможность записи в которые определяется мультиплексорами М5-М7. Размещение входного и выходного триггеров «рядом» с I/O-выводами является особенно полезным свойством ИС типа FPGA. Относительно большие задержки при прохождении сигналов от выходов внутренних триггеров логических блоков до блоков ввода/вывода могут затруднить стыковку данной ИС со стороны ее выходов с внешними синхронными системами, если частота тактового сигнала очень высока. Большие задержки от I/О-выводов до входов триггеров в логических блоках могут затруднить сопряжение данной ИС со стороны ее входов с внешней системой с точки зрения удовлетворения требованиям по времени установления и времени удержания, если внешние входные сигналы поступают непосредственно на тактовые входы триггеров внутри логических блоков, а не фиксируются сначала триггерами в блоках ввода/вывода. Конечно, применение триггеров в блоках ввода/вывода возможно только в том случае, когда технические требования к внешнему интерфейсу ИС типа FPGA допускают «конвейерный режим» работы по входам и выходам.

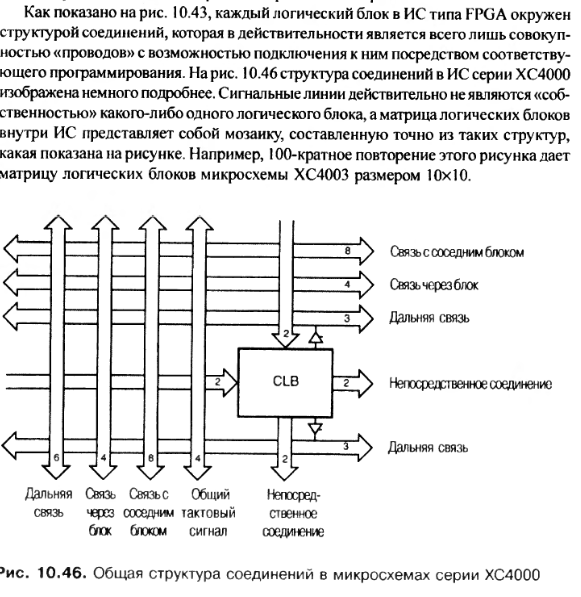

37. Программируемые соединения

Как показано на рис., каждый логический блок в ИС типа FPGA окружен структурой соединений, которая в действительности является всего лишь совокупностью «проводов» с возможностью подключения к ним посредством соответствующего программирования. Матрица логических блоков внутри ИС представляет собой мозаику, составленную из таких структур, какая показана на рисунке.

Цифрами внутри стрелок укатано число сигнальных линий в каждой шине. Т.е., у логического блока есть две выходные шины, идущие к логическим блокам, расположенным непосредственно под данным блоком и справа от него. Кроме того, каждый логический блок соединяется с тремя шинами, изображенными над ним, с одной шиной, находящейся под ним и с четырьмя шинами, расположенными слева от него. Сигналы по этим шинам могут передаваться в любом направлении.

Четыре сигнальные линии в шине «Общий тактовый сигнал» позволяют логическому блоку наилучшим образом использовать тактовые входные сигналы, обеспечивая малую задержку и минимальный разброс задержек.

По шине «Связь с соседним блоком» данный логический блок можно соединить не только с соседним, но и с другим блоком, но для этого потребуется более одной пересылки. При этом каждый раз сигналы должны пройти через программируемый переключатель, в результате чего задержка увеличивается. По шинам «Связь через блок» сигналы проходят мимо двух логических блоков, прежде чем попадают на переключатель, что позволяет получить меньшие задержки при более длинных связях. Для действительно длинных связей используются шины «Дальняя связь», в которых сигналы вообще не проходят через какие-либо программируемые переключатели. Вместо этого сигналы вырабатываются буферами с тремя состояниями, помещенными рядом с логически блоком, и проходят вдоль всей строки матрицы, образованной логическими блоками, или вдоль всего столбца.