- •5. Простейшая схема защиты от дребезга

- •6. Шинный фиксатор уровня

- •7. Биполярные последовательностные плу

- •8. Последовательностные устройства типа gal

- •8_8. Последовательные устройства типа gal

- •13. Итерационные и последовательностные схемы

- •14. Методология синхронного проектирования

- •15. Структура синхронной системы

- •16. Разброс задержек тактового сигнала

- •17. Стробирование тактового сигнала

- •18. Асинхронные входы

- •19. Сбой в работе синхронизирующего устройства и метастабильность

- •20. Сбой в работе синхронизирующего устройства

- •21.Время выхода из метастабильности

- •22.Разработка надежного синхронизирующего устройства

- •23.Анализ времени пребывания в состоянии метастабильности

- •24. Более совершенные синхронизирующие устройства

- •25. Другие схемы синхронизирующих устройств

- •26. Триггеры с защитой от метастабильности

- •27. Синхронизация при высокоскоростной передаче данных

- •28.Интегральные схемы типа cpld

- •29. Семейство ис xc9500 фирмы Xilinx

- •30. Архитектура функционального блока

- •31. Архитектура блока ввода/вывода

- •32. Переключающая матрица

- •33. Интегральные схемы типа fpga

- •34. Семейство ис типа fpga хс4000 фирмы Xilinx

- •35. Перестраиваемый логический блок

- •36. Блок ввода/вывода

- •37. Программируемые соединения

- •38. Средства автоматизированного проектирования

- •39. Языки описания схем

- •40 Ввод схемы

- •41 Временные диаграммы и временные параметры

- •42. Анализ схемы и моделирование

- •43. Разработка печатной платы

- •44. Проектирование, предусматривающее тестируемость

- •45. Тестирование

- •46. Тестер с игольчатыми контактами и внутрисхемное тестирование

- •47. Методы сканирования

- •48. Оценка надежности цифровой системы

- •49. Основы теории длинных линий

- •50. Передача логических сигналов по длинным линиям

- •51. Согласованные нагрузки на концах линий передачи логических сигналов

- •5. Простейшая схема защиты от дребезга

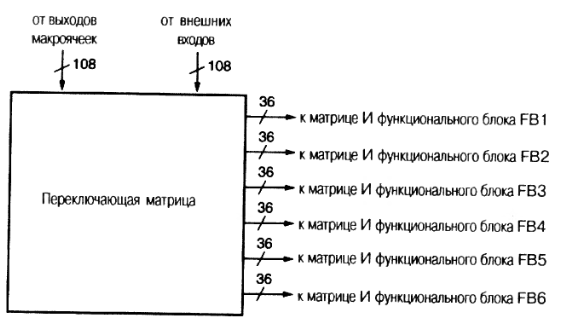

32. Переключающая матрица

Теоретически программируемая структура соединений внутри ИС типа OM-D должна допускать соединение любого внутреннего выхода ПЛУ и любого внешнего входа с любым внутренним входом ПЛУ Аналогично, должно быть возможным подключение любого выхода любого из внутренних ПЛУ к любому внешнему выводу.

Рис. 10.42 служит иллюстрацией требований, предъявляемых к переключающей матрице.

У этой микросхемы имеются 108 выходов внутренних макроячеек и 108 внешних входных выводов, так что полное число сигналов, которые должны быть поданы на переключающую матрицу в качестве входных, составляет 216. Так как в ИС имеется 6 функциональных блоков с 36 входами каждый, то переключающая матрица должна иметь в случае наибольшей полноты 216 мультиплексоров с 216 входами каждый, так чтобы сигнал с выхода каждого мультиплексора поступал на один из входов матрицы И одного из функциональных блоков.

Переключающая матрица, показанная на рисунке, может быть выполнена в микросхеме в виде прямоугольной структуры, у которой входы расположены по столбцам, а выходы - по строкам, с проходным транзистором (или логическим ключом) в каждой точке пересечения, позволяющим соединить данный вход с соответствующим выходом. Приведенный пример показывает, что это все же слишком большая структура: 216 строк и 216 столбцов!

Для каждого функционального блока должно быть возможным подключение любой комбинации входов переключающей матрицы к какой-либо комбинации входов данного функционального блока.

При проектировании различных устройств на основе ИС типа CPLD каждый раз необходимо найти соответствующий набор связей, реализуемых переключающей матрицей. Это делается с помощью «программы компоновки».

Таким образом, структура переключающей матрицы ИС типа CPLD - это компромисс между характеристиками микросхемы (быстродействие, площадь кристалла, стоимость) и возможностями программы компоновки. Программа компоновки обычно не только устанавливает соединения в переключающей матрице, но также производит назначение входов и выходов функциональных блоков и макроячеек и их привязку к внешним выводам микросхемы, а также задает «внутреннюю логику» функциональных блоков и макроячеек.

Другой важной проблемой при разработке ИС типа CPLD и программного обеспечения является привязка выводов. В большинстве приложений ИС типа CPLD считается нормальным разрешить программе компоновки выбирать любые возможные выводы в качестве внешних входов и выходов данного устройства. Но когда проект закончен и изготовлена печатная плата, разработчик может пожелать «зафиксировать» назначение выводов, так чтобы они оставались теми же самыми при изменениях, связанных с исправлением ошибок в проекте. Желаемая «привязка» выводов обычно указывается в файле, который читается программой компоновки.

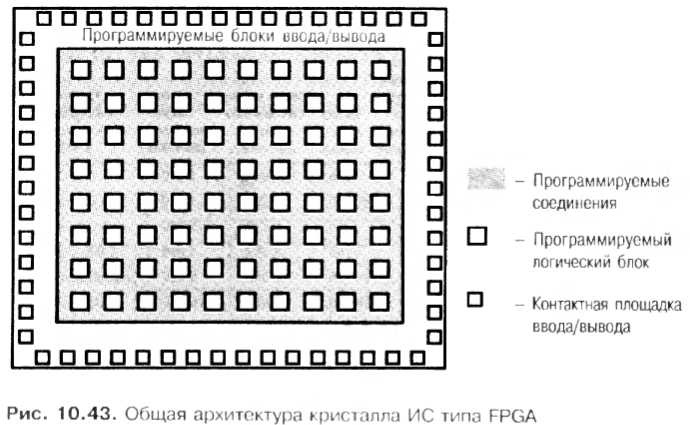

33. Интегральные схемы типа fpga

Программируемая в условиях эксплуатации матрица вентилей в какой-то мере подобна CPLD, вывернутой изнутри наружу. Как показано на рис. 10.43, на кристалле расположено большое число программируемых логических блоков, каждый из которых меньше, чем ПЛУ. Они распределены по всему кристаллу среди программируемых соединений, а вся матрица окружена программируемыми блоками ввода/вывода. Программируемый логический блок ИС типа FPGA обладает меньшими возможностями, чем типичное ПЛУ, но одна микросхема типа FPGA содержит гораздо больше логических блоков, чем ИС типа CPLD при том же самом размере кристалла.

Микросхемы типа FPGA были изобретены фирмой Xilinx, Inc., и в этом параграфе для иллюстрации архитектуры ИС типа FPGA мы воспользуемся одним из популярных семейств этой фирмы - семейством ХС4000Е.