- •5. Простейшая схема защиты от дребезга

- •6. Шинный фиксатор уровня

- •7. Биполярные последовательностные плу

- •8. Последовательностные устройства типа gal

- •8_8. Последовательные устройства типа gal

- •13. Итерационные и последовательностные схемы

- •14. Методология синхронного проектирования

- •15. Структура синхронной системы

- •16. Разброс задержек тактового сигнала

- •17. Стробирование тактового сигнала

- •18. Асинхронные входы

- •19. Сбой в работе синхронизирующего устройства и метастабильность

- •20. Сбой в работе синхронизирующего устройства

- •21.Время выхода из метастабильности

- •22.Разработка надежного синхронизирующего устройства

- •23.Анализ времени пребывания в состоянии метастабильности

- •24. Более совершенные синхронизирующие устройства

- •25. Другие схемы синхронизирующих устройств

- •26. Триггеры с защитой от метастабильности

- •27. Синхронизация при высокоскоростной передаче данных

- •28.Интегральные схемы типа cpld

- •29. Семейство ис xc9500 фирмы Xilinx

- •30. Архитектура функционального блока

- •31. Архитектура блока ввода/вывода

- •32. Переключающая матрица

- •33. Интегральные схемы типа fpga

- •34. Семейство ис типа fpga хс4000 фирмы Xilinx

- •35. Перестраиваемый логический блок

- •36. Блок ввода/вывода

- •37. Программируемые соединения

- •38. Средства автоматизированного проектирования

- •39. Языки описания схем

- •40 Ввод схемы

- •41 Временные диаграммы и временные параметры

- •42. Анализ схемы и моделирование

- •43. Разработка печатной платы

- •44. Проектирование, предусматривающее тестируемость

- •45. Тестирование

- •46. Тестер с игольчатыми контактами и внутрисхемное тестирование

- •47. Методы сканирования

- •48. Оценка надежности цифровой системы

- •49. Основы теории длинных линий

- •50. Передача логических сигналов по длинным линиям

- •51. Согласованные нагрузки на концах линий передачи логических сигналов

- •5. Простейшая схема защиты от дребезга

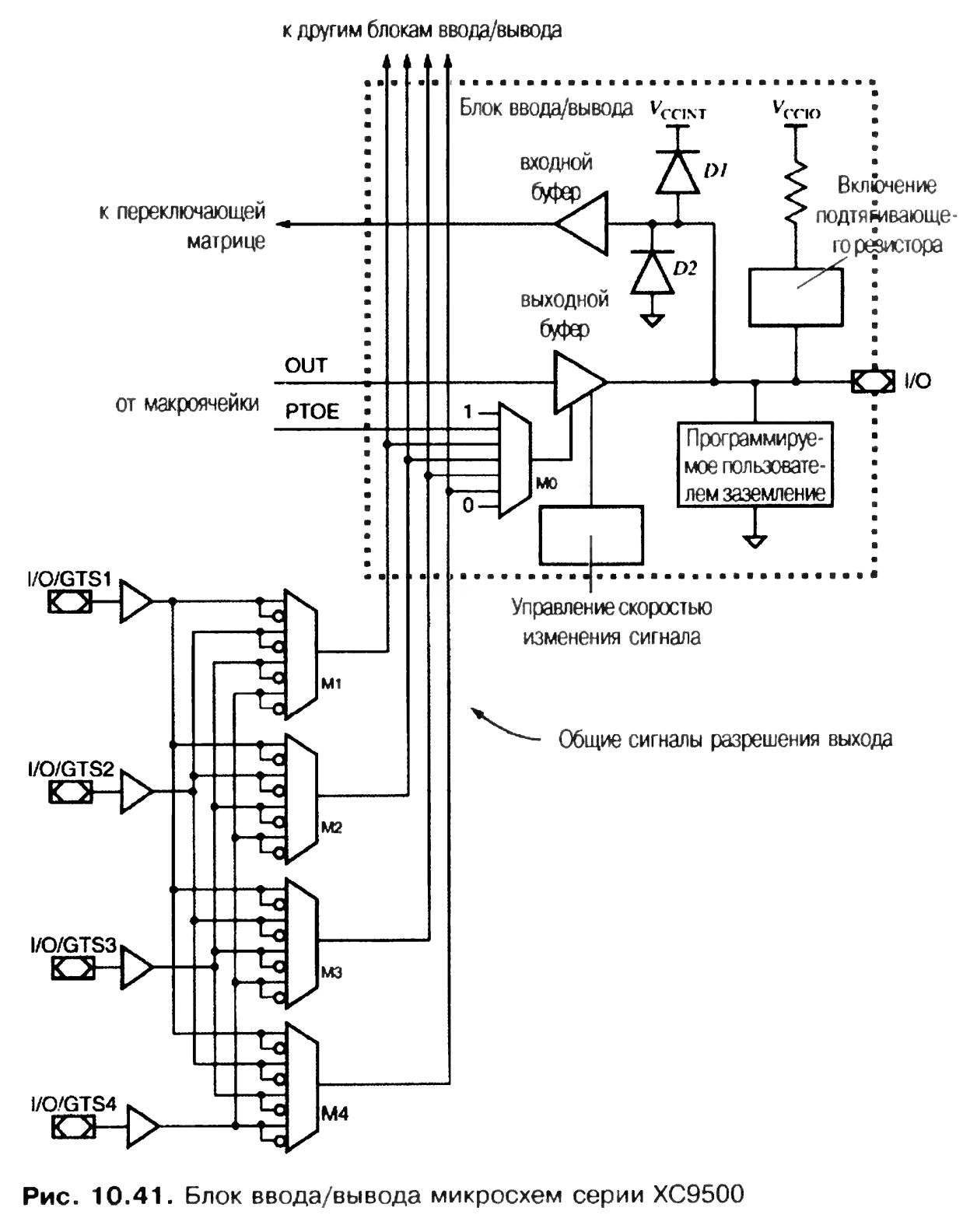

31. Архитектура блока ввода/вывода

Структура блока ввода/вывода {I/O block, IOB) в ИС семейства ХС9500 показана на рис. 10.41. Имеются семь вариантов выбора сигнала разрешения выхода для выходного буфера с тремя состояниями. Буфер может быть всегда открытым, всегда запертым, его состояние может определяться термом-произведением РТОЕ, поступающим от соответствующей макроячейки, или любым из четырех сигналов общего разрешения выхода. Сигналы общего разрешения выхода могут иметь как высокий активный уровень, так и низкий активный уровень, в зависимости от сигналов на внешних выводах GTS.

Блок ввода/вывода микросхем семейства ХС9500 является хорошим примером важной тенденции в архитектуре блоков ввода/вывода микросхем типа CPLD и FPGA: в нем, кроме управления «логическими» действиями вроде разрешения выхода, имеется возможность изменять многие «аналоговые» параметры. В блоке ввода/вывода можно изменять значения трех аналоговых параметров:

• Управление скоростью изменения выходного напряжения. Для того чтобы получать быстродействующее или медленно работающее устройство, можно задавать время нарастания и спада выходных сигналов. Установка наибольшего быстродействия обеспечивает наименьшую возможную задержку распространения, в то время как задание режима медленной работы устройства позволяет уменьшить «звон» в линии передачи и шумы в системе за счет небольшой дополнительной задержки.

• Включение резистора нагрузки между выходом и шиной питания. Когда резистор нагрузки включен, он предотвращает появление на выходном выводе плавающего напряжения при подаче на микросхему напряжения питания. Это полезно в том случае, когда выходные сигналы поступают на входы разрешения других логических устройств с низким активным уровнем, в отношении которых не предполагается, что в момент включения питания на них будет подан сигнал, имеющий активное значение.

• Образование программируемых пользователем выводов земли. Эта возможность фактически позволяет перераспределять I/O-выводы так, чтобы те или иные выводы были выводами земли, а вовсе не сигнальными выводами. Это оказывается полезным в быстродействующих устройствах с высокой скоростью изменения сигналов. Необходимость в дополнительных выводах земли возникает в тех случаях, когда имеют место большие броски тока, возникающие при одновременном переключении сигналов на нескольких выходах.

Кроме этих особенностей, ИС семейства ХС9500 совместимы с внешними устройствами с напряжением питания 5 В и 3.3 В. Входной буфер и внутренняя логика работают от источника питания с напряжением VCCINT равным 5 вольтам. В зависимости от напряжения питания внешних устройств, в выходном каскаде используется напряжение питания VCCIO, равное 5 В или 3.3 В. Обратите внимание, что включение резистора между выходом и шиной питания подтягивает напряжение на выходе до напряжения питания блока I/O, то есть до напряжения VCCIO- Диоды DI и D2 необходимы для фиксации выходного напряжения на уровне не выше значения VCCINT, и не ниже уровня земли. За эти границы величина выходного напряжения могла бы выходить из-за «звона» в линии передачи.